LLVM API Documentation

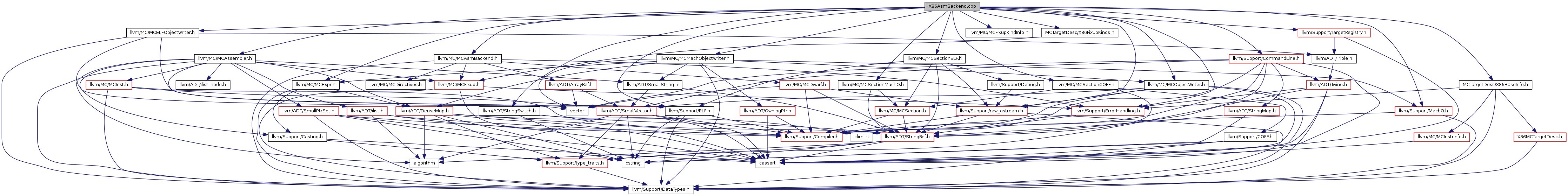

#include "MCTargetDesc/X86BaseInfo.h"#include "MCTargetDesc/X86FixupKinds.h"#include "llvm/ADT/StringSwitch.h"#include "llvm/MC/MCAsmBackend.h"#include "llvm/MC/MCAssembler.h"#include "llvm/MC/MCELFObjectWriter.h"#include "llvm/MC/MCExpr.h"#include "llvm/MC/MCFixupKindInfo.h"#include "llvm/MC/MCMachObjectWriter.h"#include "llvm/MC/MCObjectWriter.h"#include "llvm/MC/MCSectionCOFF.h"#include "llvm/MC/MCSectionELF.h"#include "llvm/MC/MCSectionMachO.h"#include "llvm/Support/CommandLine.h"#include "llvm/Support/ELF.h"#include "llvm/Support/ErrorHandling.h"#include "llvm/Support/MachO.h"#include "llvm/Support/TargetRegistry.h"#include "llvm/Support/raw_ostream.h"

Go to the source code of this file.

Namespaces | |

| CU | |

Enumerations | |

| enum | CompactUnwindEncodings |

| Compact unwind encoding values. More... | |

Functions | |

| static unsigned | getFixupKindLog2Size (unsigned Kind) |

| static unsigned | getRelaxedOpcodeBranch (unsigned Op) |

| static unsigned | getRelaxedOpcodeArith (unsigned Op) |

| static unsigned | getRelaxedOpcode (unsigned Op) |

Variables | |

| static cl::opt< bool > | MCDisableArithRelaxation ("mc-x86-disable-arith-relaxation", cl::desc("Disable relaxation of arithmetic instruction for X86")) |

Compact unwind encoding values.

Definition at line 397 of file X86AsmBackend.cpp.

Definition at line 38 of file X86AsmBackend.cpp.

References llvm::FK_Data_1, llvm::FK_Data_2, llvm::FK_Data_4, llvm::FK_Data_8, llvm::FK_PCRel_1, llvm::FK_PCRel_2, llvm::FK_PCRel_4, llvm::FK_PCRel_8, llvm::FK_SecRel_1, llvm::FK_SecRel_2, llvm::FK_SecRel_4, llvm::FK_SecRel_8, llvm_unreachable, llvm::X86::reloc_global_offset_table, llvm::X86::reloc_riprel_4byte, llvm::X86::reloc_riprel_4byte_movq_load, and llvm::X86::reloc_signed_4byte.

Definition at line 227 of file X86AsmBackend.cpp.

References getRelaxedOpcodeArith(), and getRelaxedOpcodeBranch().

Definition at line 158 of file X86AsmBackend.cpp.

Referenced by getRelaxedOpcode().

Definition at line 133 of file X86AsmBackend.cpp.

Referenced by getRelaxedOpcode().