LLVM API Documentation

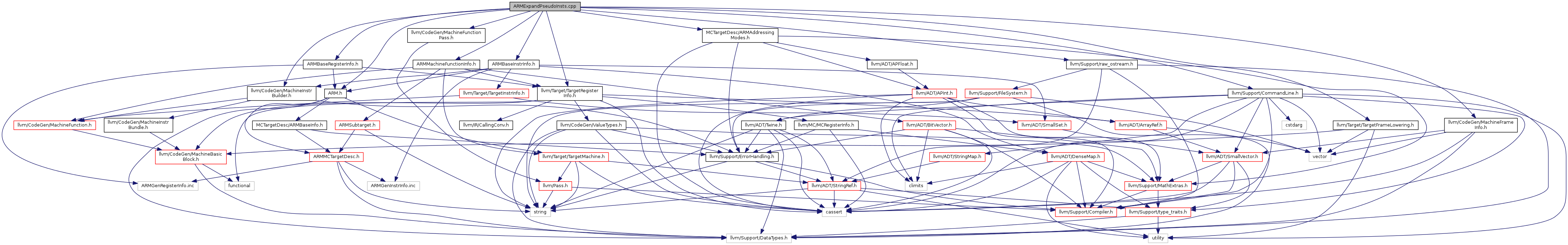

#include "ARM.h"#include "ARMBaseInstrInfo.h"#include "ARMBaseRegisterInfo.h"#include "ARMMachineFunctionInfo.h"#include "MCTargetDesc/ARMAddressingModes.h"#include "llvm/CodeGen/MachineFrameInfo.h"#include "llvm/CodeGen/MachineFunctionPass.h"#include "llvm/CodeGen/MachineInstrBuilder.h"#include "llvm/Support/CommandLine.h"#include "llvm/Support/raw_ostream.h"#include "llvm/Target/TargetFrameLowering.h"#include "llvm/Target/TargetRegisterInfo.h"

Go to the source code of this file.

Macros | |

| #define | DEBUG_TYPE "arm-pseudo" |

Enumerations | |

| enum | NEONRegSpacing |

Functions | |

| static const NEONLdStTableEntry * | LookupNEONLdSt (unsigned Opcode) |

| static void | GetDSubRegs (unsigned Reg, NEONRegSpacing RegSpc, const TargetRegisterInfo *TRI, unsigned &D0, unsigned &D1, unsigned &D2, unsigned &D3) |

Variables | |

| static cl::opt< bool > | VerifyARMPseudo ("verify-arm-pseudo-expand", cl::Hidden, cl::desc("Verify machine code after expanding ARM pseudos")) |

| static const NEONLdStTableEntry | NEONLdStTable [] |

| #define DEBUG_TYPE "arm-pseudo" |

Definition at line 17 of file ARMExpandPseudoInsts.cpp.

| enum NEONRegSpacing |

Definition at line 92 of file ARMExpandPseudoInsts.cpp.

|

static |

GetDSubRegs - Get 4 D subregisters of a Q, QQ, or QQQQ register, corresponding to the specified register spacing. Not all of the results are necessarily valid, e.g., a Q register only has 2 D subregisters.

Definition at line 350 of file ARMExpandPseudoInsts.cpp.

References llvm::MCRegisterInfo::getSubReg().

|

static |

LookupNEONLdSt - Search the NEONLdStTable for information about a NEON load or store pseudo instruction.

Definition at line 326 of file ARMExpandPseudoInsts.cpp.

References llvm::array_lengthof(), I, and NEONLdStTable.

|

static |

Definition at line 130 of file ARMExpandPseudoInsts.cpp.

Referenced by LookupNEONLdSt().