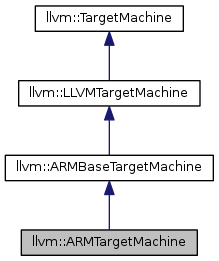

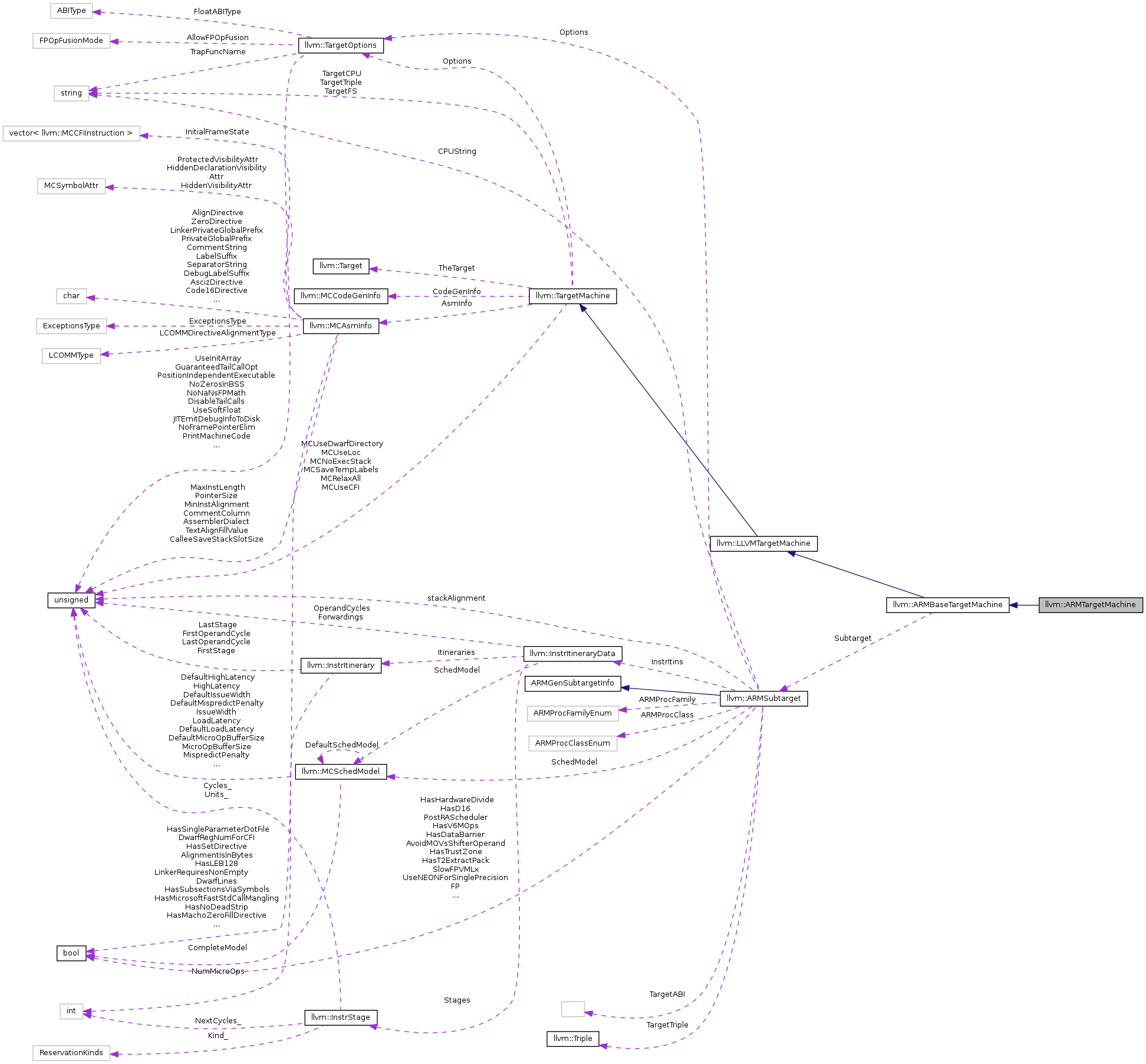

LLVM API Documentation

#include <ARMTargetMachine.h>

Public Member Functions | |

| ARMTargetMachine (const Target &T, StringRef TT, StringRef CPU, StringRef FS, const TargetOptions &Options, Reloc::Model RM, CodeModel::Model CM, CodeGenOpt::Level OL) | |

| virtual const ARMRegisterInfo * | getRegisterInfo () const |

| virtual const ARMTargetLowering * | getTargetLowering () const |

| virtual const ARMSelectionDAGInfo * | getSelectionDAGInfo () const |

| virtual const ARMFrameLowering * | getFrameLowering () const |

| virtual const ARMInstrInfo * | getInstrInfo () const |

| virtual const DataLayout * | getDataLayout () const |

Public Member Functions inherited from llvm::ARMBaseTargetMachine Public Member Functions inherited from llvm::ARMBaseTargetMachine | |

| ARMBaseTargetMachine (const Target &T, StringRef TT, StringRef CPU, StringRef FS, const TargetOptions &Options, Reloc::Model RM, CodeModel::Model CM, CodeGenOpt::Level OL) | |

| virtual ARMJITInfo * | getJITInfo () |

| virtual const ARMSubtarget * | getSubtargetImpl () const |

| virtual const InstrItineraryData * | getInstrItineraryData () const |

| virtual void | addAnalysisPasses (PassManagerBase &PM) |

| Register ARM analysis passes with a pass manager. More... | |

| virtual TargetPassConfig * | createPassConfig (PassManagerBase &PM) |

| virtual bool | addCodeEmitter (PassManagerBase &PM, JITCodeEmitter &MCE) |

Public Member Functions inherited from llvm::LLVMTargetMachine Public Member Functions inherited from llvm::LLVMTargetMachine | |

| virtual bool | addPassesToEmitFile (PassManagerBase &PM, formatted_raw_ostream &Out, CodeGenFileType FileType, bool DisableVerify=true, AnalysisID StartAfter=0, AnalysisID StopAfter=0) |

| virtual bool | addPassesToEmitMachineCode (PassManagerBase &PM, JITCodeEmitter &MCE, bool DisableVerify=true) |

| virtual bool | addPassesToEmitMC (PassManagerBase &PM, MCContext *&Ctx, raw_ostream &OS, bool DisableVerify=true) |

Public Member Functions inherited from llvm::TargetMachine Public Member Functions inherited from llvm::TargetMachine | |

| virtual | ~TargetMachine () |

| const Target & | getTarget () const |

| const StringRef | getTargetTriple () const |

| const StringRef | getTargetCPU () const |

| const StringRef | getTargetFeatureString () const |

| void | resetTargetOptions (const MachineFunction *MF) const |

| Reset the target options based on the function's attributes. More... | |

| const MCAsmInfo * | getMCAsmInfo () const |

| template<typename STC > | |

| const STC & | getSubtarget () const |

| virtual const TargetIntrinsicInfo * | getIntrinsicInfo () const |

| bool | hasMCRelaxAll () const |

| void | setMCRelaxAll (bool Value) |

| bool | hasMCSaveTempLabels () const |

| void | setMCSaveTempLabels (bool Value) |

| bool | hasMCNoExecStack () const |

| hasMCNoExecStack - Check whether an executable stack is not needed. More... | |

| void | setMCNoExecStack (bool Value) |

| setMCNoExecStack - Set whether an executabel stack is not needed. More... | |

| bool | hasMCUseLoc () const |

| hasMCUseLoc - Check whether we should use dwarf's .loc directive. More... | |

| void | setMCUseLoc (bool Value) |

| setMCUseLoc - Set whether all we should use dwarf's .loc directive. More... | |

| bool | hasMCUseCFI () const |

| hasMCUseCFI - Check whether we should use dwarf's .cfi_* directives. More... | |

| void | setMCUseCFI (bool Value) |

| setMCUseCFI - Set whether all we should use dwarf's .cfi_* directives. More... | |

| bool | hasMCUseDwarfDirectory () const |

| void | setMCUseDwarfDirectory (bool Value) |

| Reloc::Model | getRelocationModel () const |

| CodeModel::Model | getCodeModel () const |

| TLSModel::Model | getTLSModel (const GlobalValue *GV) const |

| CodeGenOpt::Level | getOptLevel () const |

| void | setOptLevel (CodeGenOpt::Level Level) const |

| Overrides the optimization level. More... | |

| void | setFastISel (bool Enable) |

| bool | shouldPrintMachineCode () const |

ARMTargetMachine - ARM target machine.

Definition at line 68 of file ARMTargetMachine.h.

| ARMTargetMachine::ARMTargetMachine | ( | const Target & | T, |

| StringRef | TT, | ||

| StringRef | CPU, | ||

| StringRef | FS, | ||

| const TargetOptions & | Options, | ||

| Reloc::Model | RM, | ||

| CodeModel::Model | CM, | ||

| CodeGenOpt::Level | OL | ||

| ) |

Definition at line 70 of file ARMTargetMachine.cpp.

References llvm::ARMSubtarget::getCPUString(), llvm::ARMSubtarget::hasARMOps(), llvm::LLVMTargetMachine::initAsmInfo(), llvm::report_fatal_error(), and llvm::ARMBaseTargetMachine::Subtarget.

|

inlinevirtual |

Reimplemented from llvm::TargetMachine.

Definition at line 97 of file ARMTargetMachine.h.

|

inlinevirtual |

Reimplemented from llvm::TargetMachine.

Definition at line 93 of file ARMTargetMachine.h.

|

inlinevirtual |

Reimplemented from llvm::TargetMachine.

Definition at line 96 of file ARMTargetMachine.h.

|

inlinevirtual |

getRegisterInfo - If register information is available, return it. If not, return null. This is kept separate from RegInfo until RegInfo has details of graph coloring register allocation removed from it.

Reimplemented from llvm::TargetMachine.

Definition at line 82 of file ARMTargetMachine.h.

References llvm::ARMInstrInfo::getRegisterInfo().

|

inlinevirtual |

Reimplemented from llvm::TargetMachine.

Definition at line 90 of file ARMTargetMachine.h.

|

inlinevirtual |

Reimplemented from llvm::ARMBaseTargetMachine.

Definition at line 86 of file ARMTargetMachine.h.