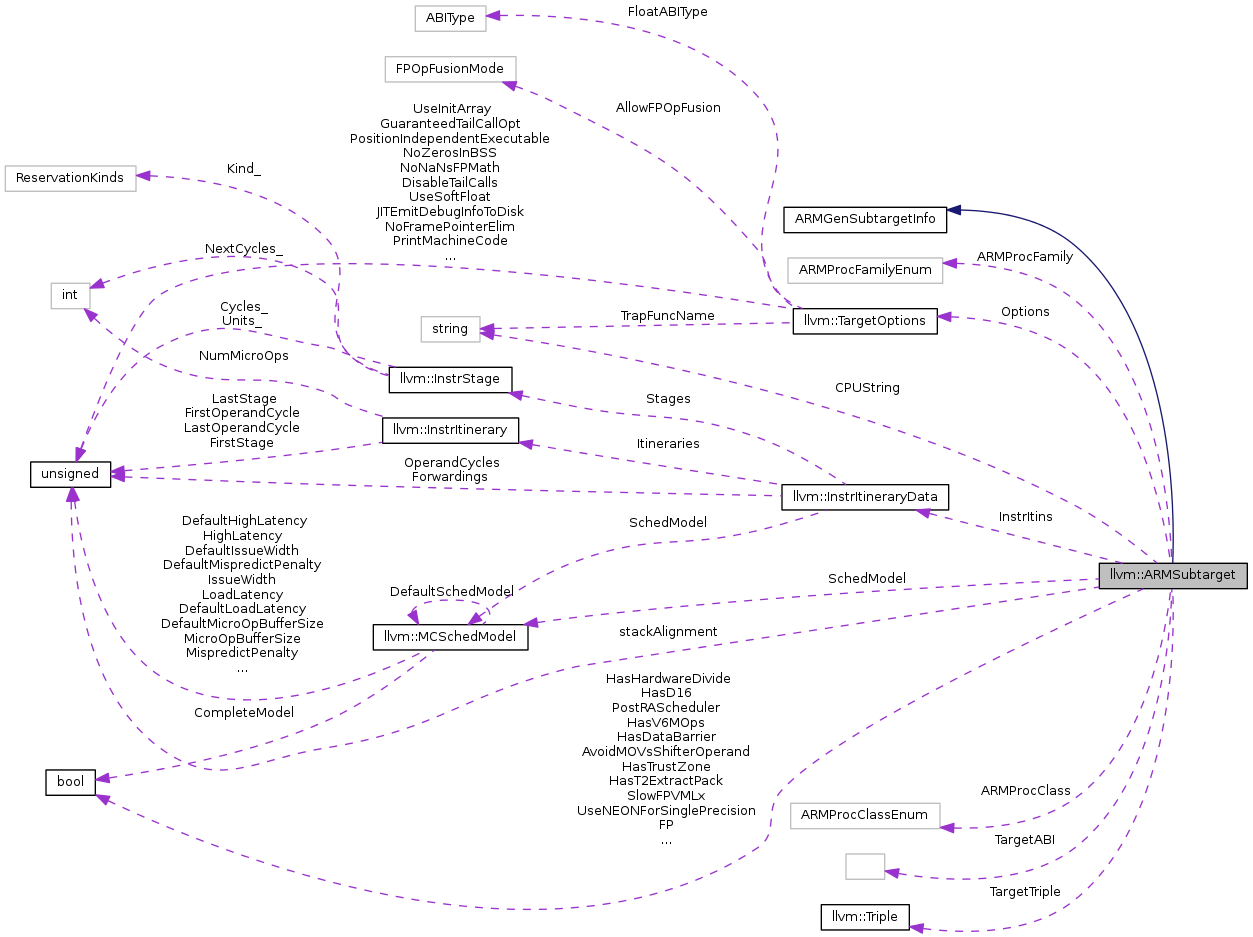

LLVM API Documentation

#include <ARMSubtarget.h>

Public Types | |

| enum | { ARM_ABI_APCS, ARM_ABI_AAPCS } |

Public Attributes | |

| enum llvm::ARMSubtarget:: { ... } | TargetABI |

Protected Types | |

| enum | ARMProcFamilyEnum { Others, CortexA5, CortexA8, CortexA9, CortexA15, CortexR5, Swift, CortexA53, CortexA57 } |

| enum | ARMProcClassEnum { None, AClass, RClass, MClass } |

Protected Attributes | |

| ARMProcFamilyEnum | ARMProcFamily |

| ARMProcFamily - ARM processor family: Cortex-A8, Cortex-A9, and others. More... | |

| ARMProcClassEnum | ARMProcClass |

| ARMProcClass - ARM processor class: None, AClass, RClass or MClass. More... | |

| bool | HasV4TOps |

| bool | HasV5TOps |

| bool | HasV5TEOps |

| bool | HasV6Ops |

| bool | HasV6MOps |

| bool | HasV6T2Ops |

| bool | HasV7Ops |

| bool | HasV8Ops |

| bool | HasVFPv2 |

| bool | HasVFPv3 |

| bool | HasVFPv4 |

| bool | HasFPARMv8 |

| bool | HasNEON |

| bool | UseNEONForSinglePrecisionFP |

| bool | UseMulOps |

| bool | SlowFPVMLx |

| bool | HasVMLxForwarding |

| bool | SlowFPBrcc |

| SlowFPBrcc - True if floating point compare + branch is slow. More... | |

| bool | InThumbMode |

| InThumbMode - True if compiling for Thumb, false for ARM. More... | |

| bool | HasThumb2 |

| HasThumb2 - True if Thumb2 instructions are supported. More... | |

| bool | NoARM |

| NoARM - True if subtarget does not support ARM mode execution. More... | |

| bool | PostRAScheduler |

| PostRAScheduler - True if using post-register-allocation scheduler. More... | |

| bool | IsR9Reserved |

| IsR9Reserved - True if R9 is a not available as general purpose register. More... | |

| bool | UseMovt |

| bool | SupportsTailCall |

| bool | HasFP16 |

| bool | HasD16 |

| bool | HasHardwareDivide |

| HasHardwareDivide - True if subtarget supports [su]div. More... | |

| bool | HasHardwareDivideInARM |

| HasHardwareDivideInARM - True if subtarget supports [su]div in ARM mode. More... | |

| bool | HasT2ExtractPack |

| bool | HasDataBarrier |

| bool | Pref32BitThumb |

| bool | AvoidCPSRPartialUpdate |

| bool | AvoidMOVsShifterOperand |

| bool | HasRAS |

| bool | HasMPExtension |

| bool | HasVirtualization |

| bool | FPOnlySP |

| bool | HasPerfMon |

| bool | HasTrustZone |

| HasTrustZone - if true, processor supports TrustZone security extensions. More... | |

| bool | HasCrypto |

| HasCrypto - if true, processor supports Cryptography extensions. More... | |

| bool | HasCRC |

| HasCRC - if true, processor supports CRC instructions. More... | |

| bool | AllowsUnalignedMem |

| bool | RestrictIT |

| bool | Thumb2DSP |

| bool | UseNaClTrap |

| NaCl TRAP instruction is generated instead of the regular TRAP. More... | |

| bool | UnsafeFPMath |

| Target machine allowed unsafe FP math (such as use of NEON fp) More... | |

| unsigned | stackAlignment |

| std::string | CPUString |

| CPUString - String name of used CPU. More... | |

| Triple | TargetTriple |

| TargetTriple - What processor and OS we're targeting. More... | |

| const MCSchedModel * | SchedModel |

| SchedModel - Processor specific instruction costs. More... | |

| InstrItineraryData | InstrItins |

| Selected instruction itineraries (one entry per itinerary class.) More... | |

| const TargetOptions & | Options |

| Options passed via command line that could influence the target. More... | |

Definition at line 31 of file ARMSubtarget.h.

| anonymous enum |

| Enumerator | |

|---|---|

| ARM_ABI_APCS | |

| ARM_ABI_AAPCS | |

Definition at line 214 of file ARMSubtarget.h.

|

protected |

| Enumerator | |

|---|---|

| None | |

| AClass | |

| RClass | |

| MClass | |

Definition at line 36 of file ARMSubtarget.h.

|

protected |

| Enumerator | |

|---|---|

| Others | |

| CortexA5 | |

| CortexA8 | |

| CortexA9 | |

| CortexA15 | |

| CortexR5 | |

| Swift | |

| CortexA53 | |

| CortexA57 | |

Definition at line 33 of file ARMSubtarget.h.

| ARMSubtarget::ARMSubtarget | ( | const std::string & | TT, |

| const std::string & | CPU, | ||

| const std::string & | FS, | ||

| const TargetOptions & | Options | ||

| ) |

This constructor initializes the data members to match that of the specified triple.

Definition at line 77 of file ARMSubtarget.cpp.

References resetSubtargetFeatures().

|

inline |

Definition at line 332 of file ARMSubtarget.h.

References AllowsUnalignedMem.

Referenced by llvm::ARMTargetLowering::allowsUnalignedMemoryAccesses().

|

inline |

Definition at line 290 of file ARMSubtarget.h.

References AvoidCPSRPartialUpdate.

|

inline |

Definition at line 291 of file ARMSubtarget.h.

References AvoidMOVsShifterOperand.

| void llvm::ARMSubtarget::computeIssueWidth | ( | ) |

| bool ARMSubtarget::enablePostRAScheduler | ( | CodeGenOpt::Level | OptLevel, |

| TargetSubtargetInfo::AntiDepBreakMode & | Mode, | ||

| RegClassVector & | CriticalPathRCs | ||

| ) | const |

enablePostRAScheduler - True at 'More' optimization.

Definition at line 318 of file ARMSubtarget.cpp.

References llvm::TargetSubtargetInfo::ANTIDEP_NONE, llvm::CodeGenOpt::Default, and PostRAScheduler.

|

inline |

Definition at line 336 of file ARMSubtarget.h.

References CPUString.

Referenced by llvm::ARMTargetMachine::ARMTargetMachine().

|

inline |

getInstrItins - Return the instruction itineraies based on subtarget selection.

Definition at line 351 of file ARMSubtarget.h.

References InstrItins.

|

inline |

getMaxInlineSizeThreshold - Returns the maximum memset / memcpy size that still makes it profitable to inline the call.

Definition at line 227 of file ARMSubtarget.h.

References isThumb1Only().

Referenced by llvm::ARMSelectionDAGInfo::EmitTargetCodeForMemcpy().

| unsigned ARMSubtarget::getMispredictionPenalty | ( | ) | const |

Definition at line 309 of file ARMSubtarget.cpp.

References llvm::MCSchedModel::MispredictPenalty, and SchedModel.

Referenced by llvm::ARMBaseInstrInfo::isProfitableToIfCvt().

|

inline |

getStackAlignment - Returns the minimum alignment known to hold of the stack frame on entry to the function and which must be maintained by every function for this subtarget.

Definition at line 356 of file ARMSubtarget.h.

References stackAlignment.

|

inline |

Definition at line 300 of file ARMSubtarget.h.

References TargetTriple.

Referenced by llvm::ARMTargetLowering::ARMTargetLowering(), and hasSinCos().

| bool ARMSubtarget::GVIsIndirectSymbol | ( | const GlobalValue * | GV, |

| Reloc::Model | RelocM | ||

| ) | const |

GVIsIndirectSymbol - true if the GV will be accessed via an indirect symbol.

GVIsIndirectSymbol - true if the GV will be accessed via an indirect symbol.

Definition at line 258 of file ARMSubtarget.cpp.

References llvm::GlobalValue::hasAvailableExternallyLinkage(), llvm::GlobalValue::hasCommonLinkage(), llvm::GlobalValue::hasHiddenVisibility(), llvm::GlobalValue::hasLocalLinkage(), llvm::GlobalValue::isDeclaration(), llvm::GlobalValue::isMaterializable(), isTargetDarwin(), llvm::GlobalValue::isWeakForLinker(), llvm::Reloc::PIC_, and llvm::Reloc::Static.

|

inline |

Definition at line 279 of file ARMSubtarget.h.

References HasDataBarrier, hasV6Ops(), and isThumb().

Referenced by llvm::ARMTargetLowering::ARMTargetLowering().

|

inline |

Definition at line 262 of file ARMSubtarget.h.

References NoARM.

Referenced by llvm::ARMTargetLowering::ARMTargetLowering(), and llvm::ARMTargetMachine::ARMTargetMachine().

|

inline |

Definition at line 270 of file ARMSubtarget.h.

References HasCRC.

|

inline |

Definition at line 269 of file ARMSubtarget.h.

References HasCrypto.

|

inline |

Definition at line 298 of file ARMSubtarget.h.

References HasD16.

Referenced by llvm::ARMBaseRegisterInfo::getReservedRegs().

|

inline |

Definition at line 278 of file ARMSubtarget.h.

References HasDataBarrier.

Referenced by LowerATOMIC_FENCE().

|

inline |

Definition at line 275 of file ARMSubtarget.h.

References HasHardwareDivide.

Referenced by llvm::ARMTargetLowering::ARMTargetLowering().

|

inline |

Definition at line 276 of file ARMSubtarget.h.

References HasHardwareDivideInARM.

Referenced by llvm::ARMTargetLowering::ARMTargetLowering().

|

inline |

Definition at line 297 of file ARMSubtarget.h.

References HasFP16.

Referenced by llvm::ARMTargetLowering::ARMTargetLowering().

|

inline |

Definition at line 267 of file ARMSubtarget.h.

References HasFPARMv8.

|

inline |

Definition at line 293 of file ARMSubtarget.h.

References HasMPExtension.

Referenced by LowerPREFETCH().

|

inline |

Definition at line 268 of file ARMSubtarget.h.

References HasNEON.

Referenced by AddCombineToVPADDL(), llvm::ARMTargetLowering::allowsUnalignedMemoryAccesses(), llvm::ARMTargetLowering::ARMTargetLowering(), llvm::ARMTargetLowering::getOptimalMemOpType(), llvm::ARMTargetLowering::getRegClassFor(), LowerCTPOP(), LowerShift(), PerformExtendCombine(), PerformORCombine(), PerformSELECT_CCCombine(), PerformShiftCombine(), PerformVCVTCombine(), PerformVDIVCombine(), and useNEONForSinglePrecisionFP().

|

inline |

Definition at line 287 of file ARMSubtarget.h.

References HasPerfMon.

Referenced by ReplaceREADCYCLECOUNTER().

|

inline |

Definition at line 292 of file ARMSubtarget.h.

References HasRAS.

| bool ARMSubtarget::hasSinCos | ( | ) | const |

This function returns true if the target has sincos() routine in its compiler runtime or math libraries.

Definition at line 313 of file ARMSubtarget.cpp.

References llvm::Triple::getOS(), getTargetTriple(), llvm::Triple::IOS, and llvm::Triple::isOSVersionLT().

Referenced by llvm::ARMTargetLowering::ARMTargetLowering().

|

inline |

Definition at line 277 of file ARMSubtarget.h.

References HasT2ExtractPack.

Referenced by PerformORCombine().

|

inline |

Definition at line 322 of file ARMSubtarget.h.

References HasThumb2.

|

inline |

Definition at line 294 of file ARMSubtarget.h.

References Thumb2DSP.

Referenced by llvm::ARMTargetLowering::ARMTargetLowering(), and getArchForCPU().

|

inline |

Definition at line 288 of file ARMSubtarget.h.

References HasTrustZone.

|

inline |

|

inline |

Definition at line 246 of file ARMSubtarget.h.

References HasV5TEOps.

Referenced by getArchForCPU(), llvm::ARMBaseInstrInfo::loadRegFromStackSlot(), LowerPREFETCH(), and llvm::ARMBaseInstrInfo::storeRegToStackSlot().

|

inline |

Definition at line 245 of file ARMSubtarget.h.

References HasV5TOps.

Referenced by llvm::ARMTargetLowering::ARMTargetLowering(), and getArchForCPU().

|

inline |

|

inline |

Definition at line 247 of file ARMSubtarget.h.

References HasV6Ops.

Referenced by llvm::ARMTargetLowering::ARMTargetLowering(), llvm::ARMTargetLowering::ExpandInlineAsm(), getArchForCPU(), hasAnyDataBarrier(), LowerATOMIC_FENCE(), and PerformShiftCombine().

|

inline |

Definition at line 249 of file ARMSubtarget.h.

References HasV6T2Ops.

Referenced by getArchForCPU(), llvm::ARMTargetLowering::LowerAsmOperandForConstraint(), LowerCTTZ(), PerformORCombine(), and useMovt().

|

inline |

Definition at line 250 of file ARMSubtarget.h.

References HasV7Ops.

Referenced by llvm::ARMTargetLowering::allowsUnalignedMemoryAccesses(), getArchForCPU(), and LowerPREFETCH().

|

inline |

Definition at line 251 of file ARMSubtarget.h.

References HasV8Ops.

Referenced by llvm::ARMTargetLowering::ARMTargetLowering(), and getArchForCPU().

|

inline |

Definition at line 264 of file ARMSubtarget.h.

References HasVFPv2.

Referenced by llvm::ARMTargetLowering::ARMTargetLowering(), llvm::ARMBaseInstrInfo::CreateTargetPostRAHazardRecognizer(), isLegalAddressImmediate(), and isLegalT2AddressImmediate().

|

inline |

Definition at line 265 of file ARMSubtarget.h.

References HasVFPv3.

Referenced by llvm::ARMBaseRegisterInfo::getReservedRegs(), and llvm::ARMTargetLowering::isFPImmLegal().

|

inline |

Definition at line 266 of file ARMSubtarget.h.

References HasVFPv4.

Referenced by llvm::ARMTargetLowering::ARMTargetLowering().

|

inline |

Definition at line 271 of file ARMSubtarget.h.

References HasVirtualization.

|

inline |

Definition at line 284 of file ARMSubtarget.h.

References HasVMLxForwarding.

Referenced by PerformVMULCombine().

|

inline |

Definition at line 317 of file ARMSubtarget.h.

References ARM_ABI_AAPCS, and TargetABI.

Referenced by llvm::ARMTargetLowering::ARMTargetLowering(), llvm::ARMSelectionDAGInfo::EmitTargetCodeForMemset(), llvm::ARMBaseRegisterInfo::getCalleeSavedRegs(), llvm::ARMBaseRegisterInfo::getCallPreservedMask(), and llvm::ARMBaseRegisterInfo::getThisReturnPreservedMask().

|

inline |

Definition at line 325 of file ARMSubtarget.h.

References AClass, and ARMProcClass.

|

inline |

Definition at line 316 of file ARMSubtarget.h.

References ARM_ABI_APCS, and TargetABI.

|

inline |

Definition at line 256 of file ARMSubtarget.h.

References ARMProcFamily, and CortexA15.

Referenced by llvm::ARMBaseInstrInfo::expandPostRAPseudo(), llvm::ARMBaseInstrInfo::getPartialRegUpdateClearance(), and isLikeA9().

|

inline |

Definition at line 253 of file ARMSubtarget.h.

References ARMProcFamily, and CortexA5.

|

inline |

Definition at line 254 of file ARMSubtarget.h.

References ARMProcFamily, and CortexA8.

Referenced by adjustDefLatency(), llvm::ARMBaseInstrInfo::getExecutionDomain(), llvm::ARMBaseInstrInfo::getNumMicroOps(), and llvm::ARMBaseInstrInfo::getOperandLatency().

|

inline |

Definition at line 255 of file ARMSubtarget.h.

References ARMProcFamily, and CortexA9.

Referenced by llvm::ARMBaseInstrInfo::getExecutionDomain(), and isLikeA9().

|

inline |

Definition at line 258 of file ARMSubtarget.h.

References CPUString.

|

inline |

Definition at line 260 of file ARMSubtarget.h.

References ARMProcFamily, and CortexR5.

|

inline |

Definition at line 285 of file ARMSubtarget.h.

References SlowFPBrcc.

Referenced by canChangeToInt().

|

inline |

Definition at line 286 of file ARMSubtarget.h.

References FPOnlySP.

Referenced by llvm::ARMTargetLowering::ARMTargetLowering().

|

inline |

Definition at line 259 of file ARMSubtarget.h.

References isCortexA15(), and isCortexA9().

Referenced by adjustDefLatency(), llvm::ARMTargetLowering::ARMTargetLowering(), llvm::ARMBaseRegisterInfo::avoidWriteAfterWrite(), llvm::ARMHazardRecognizer::getHazardType(), llvm::ARMBaseInstrInfo::getNumMicroOps(), and llvm::ARMBaseInstrInfo::getOperandLatency().

|

inline |

Definition at line 323 of file ARMSubtarget.h.

References ARMProcClass, and MClass.

Referenced by getArchForCPU(), llvm::ARMBaseRegisterInfo::getCalleeSavedRegs(), and LowerATOMIC_FENCE().

|

inline |

Definition at line 327 of file ARMSubtarget.h.

References IsR9Reserved.

Referenced by llvm::ARMBaseRegisterInfo::getRegPressureLimit(), and llvm::ARMBaseRegisterInfo::getReservedRegs().

|

inline |

Definition at line 324 of file ARMSubtarget.h.

References ARMProcClass, and RClass.

|

inline |

Definition at line 257 of file ARMSubtarget.h.

References ARMProcFamily, and Swift.

Referenced by adjustDefLatency(), llvm::ARMBaseInstrInfo::getNumMicroOps(), llvm::ARMBaseInstrInfo::getOperandLatency(), llvm::ARMBaseInstrInfo::getPartialRegUpdateClearance(), llvm::ARMBaseInstrInfo::isProfitableToUnpredicate(), and LowerATOMIC_FENCE().

|

inline |

Definition at line 312 of file ARMSubtarget.h.

References llvm::Triple::EABI, llvm::Triple::getEnvironment(), and TargetTriple.

Referenced by llvm::ARMTargetLowering::ARMTargetLowering().

|

inline |

Definition at line 303 of file ARMSubtarget.h.

References llvm::Triple::isOSDarwin(), and TargetTriple.

Referenced by llvm::ARMTargetLowering::ARMTargetLowering(), createTLOF(), llvm::ARMAsmPrinter::EmitEndOfAsmFile(), llvm::ARMAsmPrinter::EmitInstruction(), llvm::ARMAsmPrinter::EmitStartOfAsmFile(), llvm::ARMSelectionDAGInfo::EmitTargetCodeForMemset(), llvm::ARMAsmPrinter::EmitXXStructor(), GVIsIndirectSymbol(), isTargetELF(), and llvm::ARMTargetLowering::LowerOperation().

|

inline |

Definition at line 306 of file ARMSubtarget.h.

References isTargetDarwin().

Referenced by llvm::Thumb1FrameLowering::emitPrologue(), llvm::ARMFrameLowering::emitPrologue(), and llvm::ARMAsmPrinter::EmitStartOfAsmFile().

|

inline |

Definition at line 302 of file ARMSubtarget.h.

References llvm::Triple::isiOS(), and TargetTriple.

Referenced by llvm::ARMTargetLowering::ARMTargetLowering(), llvm::ARM::createFastISel(), llvm::ARMFrameLowering::emitEpilogue(), llvm::Thumb1FrameLowering::emitPrologue(), llvm::ARMFrameLowering::emitPrologue(), llvm::ARMBaseRegisterInfo::getCalleeSavedRegs(), llvm::ARMBaseRegisterInfo::getCallPreservedMask(), llvm::ARMBaseRegisterInfo::getThisReturnPreservedMask(), llvm::ARMFrameLowering::hasFP(), and llvm::ARMFrameLowering::processFunctionBeforeCalleeSavedScan().

|

inline |

Definition at line 305 of file ARMSubtarget.h.

References llvm::Triple::isOSLinux(), and TargetTriple.

Referenced by llvm::ARM::createFastISel().

|

inline |

Definition at line 304 of file ARMSubtarget.h.

References llvm::Triple::isOSNaCl(), and TargetTriple.

Referenced by llvm::ARM::createFastISel().

|

inline |

Definition at line 319 of file ARMSubtarget.h.

References InThumbMode.

Referenced by llvm::ARMTargetLowering::ARMTargetLowering(), llvm::ARM::createFastISel(), llvm::ARMFrameLowering::emitEpilogue(), llvm::ARMTargetLowering::getRegForInlineAsmConstraint(), llvm::ARMTargetLowering::getSingleConstraintMatchWeight(), hasAnyDataBarrier(), llvm::ARMTargetLowering::isLegalAddImmediate(), llvm::ARMTargetLowering::isLegalICmpImmediate(), llvm::ARMTargetLowering::LowerAsmOperandForConstraint(), LowerATOMIC_FENCE(), and LowerPREFETCH().

|

inline |

Definition at line 320 of file ARMSubtarget.h.

References HasThumb2, and InThumbMode.

Referenced by AddCombineTo64bitMLAL(), llvm::ARMBaseInstrInfo::areLoadsFromSameBasePtr(), llvm::ARMTargetLowering::ARMTargetLowering(), llvm::ARM::createFastISel(), Expand64BitShift(), llvm::ARMTargetLowering::getMaximalGlobalOffset(), getMaxInlineSizeThreshold(), llvm::ARMTargetLowering::getPostIndexedAddressParts(), llvm::ARMTargetLowering::getPreIndexedAddressParts(), isLegalAddressImmediate(), llvm::ARMTargetLowering::isLegalAddressingMode(), IsSingleInstrConstant(), llvm::ARMTargetLowering::LowerAsmOperandForConstraint(), LowerPREFETCH(), PerformANDCombine(), PerformMULCombine(), PerformORCombine(), PerformXORCombine(), and llvm::ARMBaseInstrInfo::shouldScheduleLoadsNear().

|

inline |

Definition at line 321 of file ARMSubtarget.h.

References HasThumb2, and InThumbMode.

Referenced by llvm::ARMTargetLowering::ARMTargetLowering(), llvm::ARMBaseInstrInfo::copyPhysReg(), llvm::ARMBaseInstrInfo::CreateTargetPostRAHazardRecognizer(), llvm::ARMTargetLowering::EmitInstrWithCustomInserter(), llvm::ARMBaseInstrInfo::getOperandLatency(), llvm::ARMTargetLowering::getPostIndexedAddressParts(), llvm::ARMTargetLowering::getPreIndexedAddressParts(), llvm::ARMTargetLowering::isLegalAddImmediate(), isLegalAddressImmediate(), llvm::ARMTargetLowering::isLegalAddressingMode(), llvm::ARMTargetLowering::isLegalICmpImmediate(), llvm::ARMTargetLowering::LowerAsmOperandForConstraint(), and LowerPREFETCH().

ParseSubtargetFeatures - Parses features string setting specified subtarget options. Definition of function is auto generated by tblgen.

|

inline |

Definition at line 289 of file ARMSubtarget.h.

References Pref32BitThumb.

|

virtual |

Reset the features for the ARM target.

Definition at line 140 of file ARMSubtarget.cpp.

References llvm::X86II::FS, llvm::AttributeSet::getAttribute(), llvm::Function::getAttributes(), llvm::MachineFunction::getFunction(), llvm::Attribute::getValueAsString(), llvm::Attribute::hasAttribute(), and llvm::Attribute::None.

Referenced by ARMSubtarget().

|

inline |

Definition at line 334 of file ARMSubtarget.h.

References RestrictIT.

Referenced by llvm::ARMBaseInstrInfo::isPredicable().

|

inline |

Definition at line 330 of file ARMSubtarget.h.

References SupportsTailCall.

|

inline |

Definition at line 283 of file ARMSubtarget.h.

References SlowFPVMLx.

|

inline |

Definition at line 329 of file ARMSubtarget.h.

References hasV6T2Ops(), and UseMovt.

|

inline |

Definition at line 282 of file ARMSubtarget.h.

References UseMulOps.

|

inline |

Definition at line 295 of file ARMSubtarget.h.

References UseNaClTrap.

|

inline |

Definition at line 272 of file ARMSubtarget.h.

References hasNEON(), and UseNEONForSinglePrecisionFP.

Referenced by llvm::ARMTargetLowering::findRepresentativeClass(), and PerformSELECT_CCCombine().

|

protected |

AllowsUnalignedMem - If true, the subtarget allows unaligned memory accesses for some types. For details, see ARMTargetLowering::allowsUnalignedMemoryAccesses().

Definition at line 178 of file ARMSubtarget.h.

Referenced by allowsUnalignedMem().

|

protected |

ARMProcClass - ARM processor class: None, AClass, RClass or MClass.

Definition at line 44 of file ARMSubtarget.h.

Referenced by isAClass(), isMClass(), and isRClass().

|

protected |

ARMProcFamily - ARM processor family: Cortex-A8, Cortex-A9, and others.

Definition at line 41 of file ARMSubtarget.h.

Referenced by isCortexA15(), isCortexA5(), isCortexA8(), isCortexA9(), isCortexR5(), and isSwift().

|

protected |

AvoidCPSRPartialUpdate - If true, codegen would avoid using instructions that partially update CPSR and add false dependency on the previous CPSR setting instruction.

Definition at line 139 of file ARMSubtarget.h.

Referenced by avoidCPSRPartialUpdate().

|

protected |

AvoidMOVsShifterOperand - If true, codegen should avoid using flag setting movs with shifter operand (i.e. asr, lsl, lsr).

Definition at line 143 of file ARMSubtarget.h.

Referenced by avoidMOVsShifterOperand().

|

protected |

CPUString - String name of used CPU.

Definition at line 199 of file ARMSubtarget.h.

Referenced by getCPUString(), and isCortexM3().

|

protected |

FPOnlySP - If true, the floating point unit only supports single precision.

Definition at line 159 of file ARMSubtarget.h.

Referenced by isFPOnlySP().

|

protected |

HasCRC - if true, processor supports CRC instructions.

Definition at line 173 of file ARMSubtarget.h.

Referenced by hasCRC().

|

protected |

HasCrypto - if true, processor supports Cryptography extensions.

Definition at line 170 of file ARMSubtarget.h.

Referenced by hasCrypto().

|

protected |

HasD16 - True if subtarget is limited to 16 double precision FP registers for VFPv3.

Definition at line 116 of file ARMSubtarget.h.

Referenced by hasD16().

|

protected |

HasDataBarrier - True if the subtarget supports DMB / DSB data barrier instructions.

Definition at line 130 of file ARMSubtarget.h.

Referenced by hasAnyDataBarrier(), and hasDataBarrier().

|

protected |

HasFP16 - True if subtarget supports half-precision FP (We support VFP+HF only so far)

Definition at line 112 of file ARMSubtarget.h.

Referenced by hasFP16().

|

protected |

Definition at line 63 of file ARMSubtarget.h.

Referenced by hasFPARMv8().

|

protected |

HasHardwareDivide - True if subtarget supports [su]div.

Definition at line 119 of file ARMSubtarget.h.

Referenced by hasDivide().

|

protected |

HasHardwareDivideInARM - True if subtarget supports [su]div in ARM mode.

Definition at line 122 of file ARMSubtarget.h.

Referenced by hasDivideInARMMode().

|

protected |

HasMPExtension - True if the subtarget supports Multiprocessing extension (ARMv7 only).

Definition at line 151 of file ARMSubtarget.h.

Referenced by hasMPExtension().

|

protected |

Definition at line 64 of file ARMSubtarget.h.

Referenced by hasNEON().

|

protected |

If true, the processor supports the Performance Monitor Extensions. These include a generic cycle-counter as well as more fine-grained (often implementation-specific) events.

Definition at line 164 of file ARMSubtarget.h.

Referenced by hasPerfMon().

|

protected |

HasRAS - Some processors perform return stack prediction. CodeGen should avoid issue "normal" call instructions to callees which do not return.

Definition at line 147 of file ARMSubtarget.h.

Referenced by hasRAS().

|

protected |

HasT2ExtractPack - True if subtarget supports thumb2 extract/pack instructions.

Definition at line 126 of file ARMSubtarget.h.

Referenced by hasT2ExtractPack().

|

protected |

HasThumb2 - True if Thumb2 instructions are supported.

Definition at line 90 of file ARMSubtarget.h.

Referenced by hasThumb2(), isThumb1Only(), and isThumb2().

|

protected |

HasTrustZone - if true, processor supports TrustZone security extensions.

Definition at line 167 of file ARMSubtarget.h.

Referenced by hasTrustZone().

|

protected |

HasV4TOps, HasV5TOps, HasV5TEOps, HasV6Ops, HasV6MOps, HasV6T2Ops, HasV7Ops, HasV8Ops - Specify whether target support specific ARM ISA variants.

Definition at line 49 of file ARMSubtarget.h.

Referenced by hasV4TOps().

|

protected |

Definition at line 51 of file ARMSubtarget.h.

Referenced by hasV5TEOps().

|

protected |

Definition at line 50 of file ARMSubtarget.h.

Referenced by hasV5TOps().

|

protected |

Definition at line 53 of file ARMSubtarget.h.

Referenced by hasV6MOps().

|

protected |

Definition at line 52 of file ARMSubtarget.h.

Referenced by hasV6Ops().

|

protected |

Definition at line 54 of file ARMSubtarget.h.

Referenced by hasV6T2Ops().

|

protected |

Definition at line 55 of file ARMSubtarget.h.

Referenced by hasV7Ops().

|

protected |

Definition at line 56 of file ARMSubtarget.h.

Referenced by hasV8Ops().

|

protected |

HasVFPv2, HasVFPv3, HasVFPv4, HasFPARMv8, HasNEON - Specify what floating point ISAs are supported.

Definition at line 60 of file ARMSubtarget.h.

Referenced by hasVFP2().

|

protected |

Definition at line 61 of file ARMSubtarget.h.

Referenced by hasVFP3().

|

protected |

Definition at line 62 of file ARMSubtarget.h.

Referenced by hasVFP4().

|

protected |

HasVirtualization - True if the subtarget supports the Virtualization extension.

Definition at line 155 of file ARMSubtarget.h.

Referenced by hasVirtualization().

|

protected |

HasVMLxForwarding - If true, NEON has special multiplier accumulator forwarding to allow mul + mla being issued back to back.

Definition at line 81 of file ARMSubtarget.h.

Referenced by hasVMLxForwarding().

|

protected |

Selected instruction itineraries (one entry per itinerary class.)

Definition at line 208 of file ARMSubtarget.h.

Referenced by getInstrItineraryData().

|

protected |

InThumbMode - True if compiling for Thumb, false for ARM.

Definition at line 87 of file ARMSubtarget.h.

Referenced by isThumb(), isThumb1Only(), and isThumb2().

|

protected |

IsR9Reserved - True if R9 is a not available as general purpose register.

Definition at line 99 of file ARMSubtarget.h.

Referenced by isR9Reserved().

|

protected |

NoARM - True if subtarget does not support ARM mode execution.

Definition at line 93 of file ARMSubtarget.h.

Referenced by hasARMOps().

|

protected |

Options passed via command line that could influence the target.

Definition at line 211 of file ARMSubtarget.h.

|

protected |

PostRAScheduler - True if using post-register-allocation scheduler.

Definition at line 96 of file ARMSubtarget.h.

Referenced by enablePostRAScheduler().

|

protected |

Pref32BitThumb - If true, codegen would prefer 32-bit Thumb instructions over 16-bit ones.

Definition at line 134 of file ARMSubtarget.h.

Referenced by prefers32BitThumb().

|

protected |

RestrictIT - If true, the subtarget disallows generation of deprecated IT blocks to conform to ARMv8 rule.

Definition at line 182 of file ARMSubtarget.h.

Referenced by restrictIT().

|

protected |

SchedModel - Processor specific instruction costs.

Definition at line 205 of file ARMSubtarget.h.

Referenced by getMispredictionPenalty().

|

protected |

SlowFPBrcc - True if floating point compare + branch is slow.

Definition at line 84 of file ARMSubtarget.h.

Referenced by isFPBrccSlow().

|

protected |

SlowFPVMLx - If the VFP2 / NEON instructions are available, indicates whether the FP VML[AS] instructions are slow (if so, don't use them).

Definition at line 77 of file ARMSubtarget.h.

Referenced by useFPVMLx().

|

protected |

stackAlignment - The minimum alignment known to hold of the stack frame on entry to the function and which must be maintained by every function.

Definition at line 196 of file ARMSubtarget.h.

Referenced by getStackAlignment().

|

protected |

SupportsTailCall - True if the OS supports tail call. The dynamic linker must be able to synthesize call stubs for interworking between ARM and Thumb.

Definition at line 108 of file ARMSubtarget.h.

Referenced by supportsTailCall().

| enum { ... } llvm::ARMSubtarget::TargetABI |

Referenced by isAAPCS_ABI(), and isAPCS_ABI().

|

protected |

TargetTriple - What processor and OS we're targeting.

Definition at line 202 of file ARMSubtarget.h.

Referenced by getTargetTriple(), isTargetAEABI(), isTargetDarwin(), isTargetIOS(), isTargetLinux(), and isTargetNaCl().

|

protected |

Thumb2DSP - If true, the subtarget supports the v7 DSP (saturating arith and such) instructions in Thumb2 code.

Definition at line 186 of file ARMSubtarget.h.

Referenced by hasThumb2DSP().

|

protected |

Target machine allowed unsafe FP math (such as use of NEON fp)

Definition at line 192 of file ARMSubtarget.h.

|

protected |

UseMovt - True if MOVT / MOVW pairs are used for materialization of 32-bit imms (including global addresses).

Definition at line 103 of file ARMSubtarget.h.

Referenced by useMovt().

|

protected |

UseMulOps - True if non-microcoded fused integer multiply-add and multiply-subtract instructions should be used.

Definition at line 73 of file ARMSubtarget.h.

Referenced by useMulOps().

|

protected |

NaCl TRAP instruction is generated instead of the regular TRAP.

Definition at line 189 of file ARMSubtarget.h.

Referenced by useNaClTrap().

|

protected |

UseNEONForSinglePrecisionFP - if the NEONFP attribute has been specified. Use the method useNEONForSinglePrecisionFP() to determine if NEON should actually be used.

Definition at line 69 of file ARMSubtarget.h.

Referenced by useNEONForSinglePrecisionFP().