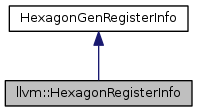

LLVM API Documentation

#include <HexagonRegisterInfo.h>

Public Member Functions | |

| HexagonRegisterInfo (HexagonSubtarget &st) | |

| const uint16_t * | getCalleeSavedRegs (const MachineFunction *MF=0) const |

| Code Generation virtual methods... More... | |

| const TargetRegisterClass *const * | getCalleeSavedRegClasses (const MachineFunction *MF=0) const |

| BitVector | getReservedRegs (const MachineFunction &MF) const |

| void | eliminateFrameIndex (MachineBasicBlock::iterator II, int SPAdj, unsigned FIOperandNum, RegScavenger *RS=NULL) const |

| void | determineFrameLayout (MachineFunction &MF) const |

| bool | requiresRegisterScavenging (const MachineFunction &MF) const |

| bool | trackLivenessAfterRegAlloc (const MachineFunction &MF) const |

| unsigned | getRARegister () const |

| unsigned | getFrameRegister (const MachineFunction &MF) const |

| unsigned | getFrameRegister () const |

| unsigned | getStackRegister () const |

Public Attributes | |

| HexagonSubtarget & | Subtarget |

Definition at line 45 of file HexagonRegisterInfo.h.

| HexagonRegisterInfo::HexagonRegisterInfo | ( | HexagonSubtarget & | st | ) |

Definition at line 41 of file HexagonRegisterInfo.cpp.

| void llvm::HexagonRegisterInfo::determineFrameLayout | ( | MachineFunction & | MF | ) | const |

determineFrameLayout - Determine the size of the frame and maximum call frame size.

| void HexagonRegisterInfo::eliminateFrameIndex | ( | MachineBasicBlock::iterator | II, |

| int | SPAdj, | ||

| unsigned | FIOperandNum, | ||

| RegScavenger * | RS = NULL |

||

| ) | const |

Definition at line 119 of file HexagonRegisterInfo.cpp.

References llvm::MachineInstrBuilder::addImm(), llvm::MachineInstrBuilder::addReg(), llvm::BuildMI(), llvm::MachineOperand::ChangeToImmediate(), llvm::MachineOperand::ChangeToRegister(), llvm::HexagonISD::CONST32_Int_Real, llvm::ISD::FrameIndex, llvm::MachineInstr::getDebugLoc(), llvm::MachineFunction::getFrameInfo(), llvm::TargetMachine::getFrameLowering(), getFrameRegister(), llvm::MachineOperand::getIndex(), llvm::TargetMachine::getInstrInfo(), llvm::MachineFrameInfo::getObjectOffset(), llvm::MachineInstr::getOpcode(), llvm::MachineInstr::getOperand(), llvm::MachineInstr::getParent(), llvm::MachineBasicBlock::getParent(), llvm::MachineOperand::getReg(), getStackRegister(), llvm::MachineFrameInfo::getStackSize(), llvm::MachineFunction::getTarget(), llvm::TargetFrameLowering::hasFP(), llvm::HexagonSubtarget::hasV4TOps(), llvm::MachineFrameInfo::hasVarSizedObjects(), HEXAGON_RESERVED_REG_1, Hexagon_WordSize, llvm::HexagonInstrInfo::immediateExtend(), llvm::HexagonInstrInfo::isConstExtended(), llvm::HexagonInstrInfo::isMemOp(), llvm::HexagonInstrInfo::isSpillPredRegOp(), llvm::HexagonInstrInfo::isValidOffset(), llvm_unreachable, llvm::A64CC::MI, Subtarget, and TII.

| const TargetRegisterClass *const * HexagonRegisterInfo::getCalleeSavedRegClasses | ( | const MachineFunction * | MF = 0 | ) | const |

Definition at line 91 of file HexagonRegisterInfo.cpp.

References llvm::HexagonSubtarget::getHexagonArchVersion(), llvm_unreachable, Subtarget, llvm::HexagonSubtarget::V1, llvm::HexagonSubtarget::V2, llvm::HexagonSubtarget::V3, llvm::HexagonSubtarget::V4, and llvm::HexagonSubtarget::V5.

| const uint16_t * HexagonRegisterInfo::getCalleeSavedRegs | ( | const MachineFunction * | MF = 0 | ) | const |

Code Generation virtual methods...

Definition at line 46 of file HexagonRegisterInfo.cpp.

References llvm::HexagonSubtarget::getHexagonArchVersion(), llvm_unreachable, Subtarget, llvm::HexagonSubtarget::V1, llvm::HexagonSubtarget::V2, llvm::HexagonSubtarget::V3, llvm::HexagonSubtarget::V4, and llvm::HexagonSubtarget::V5.

| unsigned HexagonRegisterInfo::getFrameRegister | ( | const MachineFunction & | MF | ) | const |

Definition at line 280 of file HexagonRegisterInfo.cpp.

References llvm::TargetMachine::getFrameLowering(), llvm::MachineFunction::getTarget(), and llvm::TargetFrameLowering::hasFP().

Referenced by llvm::HexagonTargetLowering::LowerFRAMEADDR().

| unsigned HexagonRegisterInfo::getFrameRegister | ( | ) | const |

Definition at line 290 of file HexagonRegisterInfo.cpp.

Referenced by eliminateFrameIndex().

| unsigned HexagonRegisterInfo::getRARegister | ( | ) | const |

Definition at line 276 of file HexagonRegisterInfo.cpp.

Referenced by llvm::HexagonTargetLowering::LowerINLINEASM().

| BitVector HexagonRegisterInfo::getReservedRegs | ( | const MachineFunction & | MF | ) | const |

Definition at line 72 of file HexagonRegisterInfo.cpp.

References HEXAGON_RESERVED_REG_1, HEXAGON_RESERVED_REG_2, and llvm::BitVector::set().

| unsigned HexagonRegisterInfo::getStackRegister | ( | ) | const |

|

inline |

requiresRegisterScavenging - returns true since we may need scavenging for a temporary register when generating hardware loop instructions.

Definition at line 68 of file HexagonRegisterInfo.h.

|

inline |

Definition at line 72 of file HexagonRegisterInfo.h.

| HexagonSubtarget& llvm::HexagonRegisterInfo::Subtarget |

Definition at line 46 of file HexagonRegisterInfo.h.

Referenced by areCombinableOperations(), eliminateFrameIndex(), getCalleeSavedRegClasses(), getCalleeSavedRegs(), llvm::HexagonTargetLowering::HexagonTargetLowering(), llvm::HexagonInstrInfo::isConditionalALU32(), llvm::HexagonInstrInfo::isConditionalLoad(), llvm::HexagonInstrInfo::isConditionalStore(), llvm::HexagonTargetLowering::isFPImmLegal(), and llvm::HexagonInstrInfo::mayBeNewStore().