|

| static cl::opt< bool > | DisablePostRA ("disable-post-ra", cl::Hidden, cl::desc("Disable Post Regalloc")) |

| |

| static cl::opt< bool > | DisableBranchFold ("disable-branch-fold", cl::Hidden, cl::desc("Disable branch folding")) |

| |

| static cl::opt< bool > | DisableTailDuplicate ("disable-tail-duplicate", cl::Hidden, cl::desc("Disable tail duplication")) |

| |

| static cl::opt< bool > | DisableEarlyTailDup ("disable-early-taildup", cl::Hidden, cl::desc("Disable pre-register allocation tail duplication")) |

| |

| static cl::opt< bool > | DisableBlockPlacement ("disable-block-placement", cl::Hidden, cl::desc("Disable probability-driven block placement")) |

| |

| static cl::opt< bool > | EnableBlockPlacementStats ("enable-block-placement-stats", cl::Hidden, cl::desc("Collect probability-driven block placement stats")) |

| |

| static cl::opt< bool > | DisableSSC ("disable-ssc", cl::Hidden, cl::desc("Disable Stack Slot Coloring")) |

| |

| static cl::opt< bool > | DisableMachineDCE ("disable-machine-dce", cl::Hidden, cl::desc("Disable Machine Dead Code Elimination")) |

| |

| static cl::opt< bool > | DisableEarlyIfConversion ("disable-early-ifcvt", cl::Hidden, cl::desc("Disable Early If-conversion")) |

| |

| static cl::opt< bool > | DisableMachineLICM ("disable-machine-licm", cl::Hidden, cl::desc("Disable Machine LICM")) |

| |

| static cl::opt< bool > | DisableMachineCSE ("disable-machine-cse", cl::Hidden, cl::desc("Disable Machine Common Subexpression Elimination")) |

| |

| static cl::opt< cl::boolOrDefault > | OptimizeRegAlloc ("optimize-regalloc", cl::Hidden, cl::desc("Enable optimized register allocation compilation path.")) |

| |

| static cl::opt< cl::boolOrDefault > | EnableMachineSched ("enable-misched", cl::Hidden, cl::desc("Enable the machine instruction scheduling pass.")) |

| |

| static cl::opt< bool > | DisablePostRAMachineLICM ("disable-postra-machine-licm", cl::Hidden, cl::desc("Disable Machine LICM")) |

| |

| static cl::opt< bool > | DisableMachineSink ("disable-machine-sink", cl::Hidden, cl::desc("Disable Machine Sinking")) |

| |

| static cl::opt< bool > | DisableLSR ("disable-lsr", cl::Hidden, cl::desc("Disable Loop Strength Reduction Pass")) |

| |

| static cl::opt< bool > | DisableCGP ("disable-cgp", cl::Hidden, cl::desc("Disable Codegen Prepare")) |

| |

| static cl::opt< bool > | DisableCopyProp ("disable-copyprop", cl::Hidden, cl::desc("Disable Copy Propagation pass")) |

| |

| static cl::opt< bool > | PrintLSR ("print-lsr-output", cl::Hidden, cl::desc("Print LLVM IR produced by the loop-reduce pass")) |

| |

| static cl::opt< bool > | PrintISelInput ("print-isel-input", cl::Hidden, cl::desc("Print LLVM IR input to isel pass")) |

| |

| static cl::opt< bool > | PrintGCInfo ("print-gc", cl::Hidden, cl::desc("Dump garbage collector data")) |

| |

| static cl::opt< bool > | VerifyMachineCode ("verify-machineinstrs", cl::Hidden, cl::desc("Verify generated machine code"), cl::init(getenv("LLVM_VERIFY_MACHINEINSTRS")!=NULL)) |

| |

| static cl::opt< std::string > | PrintMachineInstrs ("print-machineinstrs", cl::ValueOptional, cl::desc("Print machine instrs"), cl::value_desc("pass-name"), cl::init("option-unspecified")) |

| |

| static cl::opt< bool > | EarlyLiveIntervals ("early-live-intervals", cl::Hidden, cl::desc("Run live interval analysis earlier in the pipeline")) |

| |

| static RegisterRegAlloc | defaultRegAlloc ("default","pick register allocator based on -O option", useDefaultRegisterAllocator) |

| |

static cl::opt

< RegisterRegAlloc::FunctionPassCtor,

false, RegisterPassParser

< RegisterRegAlloc > > | RegAlloc ("regalloc", cl::init(&useDefaultRegisterAllocator), cl::desc("Register allocator to use")) |

| | -regalloc=... command line option. More...

|

| |

Allow standard passes to be disabled by the command line, regardless of who is adding the pass.

StandardID is the pass identified in the standard pass pipeline and provided to addPass(). It may be a target-specific ID in the case that the target directly adds its own pass, but in that case we harmlessly fall through.

TargetID is the pass that the target has configured to override StandardID.

StandardID may be a pseudo ID. In that case TargetID is the name of the real pass to run. This allows multiple options to control a single pass depending on where in the pipeline that pass is added.

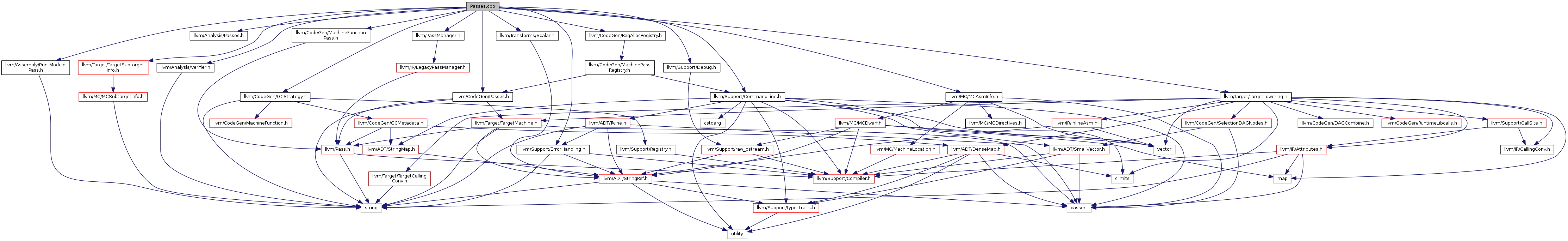

Definition at line 135 of file Passes.cpp.

References applyDisable(), applyOverride(), llvm::BranchFolderPassID, llvm::DeadMachineInstructionElimID, DisableBlockPlacement, DisableBranchFold, DisableCopyProp, DisableEarlyIfConversion, DisableEarlyTailDup, DisableMachineCSE, DisableMachineDCE, DisableMachineLICM, DisableMachineSink, DisablePostRA, DisablePostRAMachineLICM, DisableSSC, DisableTailDuplicate, llvm::EarlyIfConverterID, llvm::TargetPassConfig::EarlyTailDuplicateID, EnableMachineSched, llvm::MachineBlockPlacementID, llvm::MachineCopyPropagationID, llvm::MachineCSEID, llvm::MachineLICMID, llvm::MachineSchedulerID, llvm::MachineSinkingID, llvm::TargetPassConfig::PostRAMachineLICMID, llvm::PostRASchedulerID, llvm::StackSlotColoringID, and llvm::TailDuplicateID.

Referenced by llvm::TargetPassConfig::addPass().