LLVM API Documentation

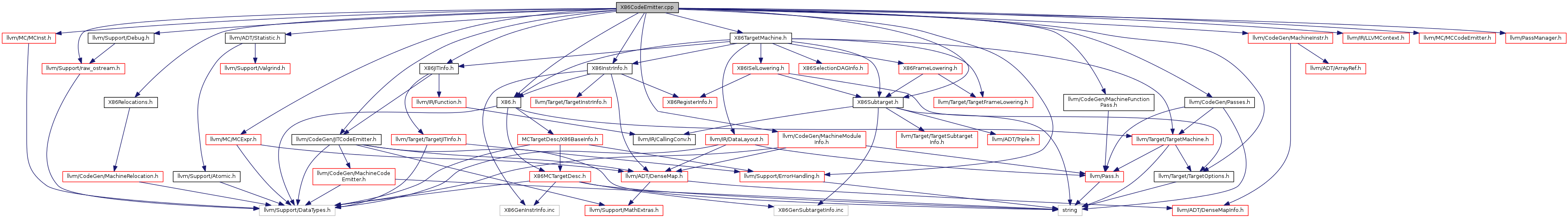

#include "X86.h"#include "X86InstrInfo.h"#include "X86JITInfo.h"#include "X86Relocations.h"#include "X86Subtarget.h"#include "X86TargetMachine.h"#include "llvm/ADT/Statistic.h"#include "llvm/CodeGen/JITCodeEmitter.h"#include "llvm/CodeGen/MachineFunctionPass.h"#include "llvm/CodeGen/MachineInstr.h"#include "llvm/CodeGen/MachineModuleInfo.h"#include "llvm/CodeGen/Passes.h"#include "llvm/IR/LLVMContext.h"#include "llvm/MC/MCCodeEmitter.h"#include "llvm/MC/MCExpr.h"#include "llvm/MC/MCInst.h"#include "llvm/PassManager.h"#include "llvm/Support/Debug.h"#include "llvm/Support/ErrorHandling.h"#include "llvm/Support/raw_ostream.h"#include "llvm/Target/TargetOptions.h"

Go to the source code of this file.

Macros | |

| #define | DEBUG_TYPE "x86-emitter" |

Functions | |

| STATISTIC (NumEmitted,"Number of machine instructions emitted") | |

| static unsigned | determineREX (const MachineInstr &MI) |

| static unsigned char | ModRMByte (unsigned Mod, unsigned RegOpcode, unsigned RM) |

| static bool | isDisp8 (int Value) |

| static bool | gvNeedsNonLazyPtr (const MachineOperand &GVOp, const TargetMachine &TM) |

| static const MCInstrDesc * | UpdateOp (MachineInstr &MI, const X86InstrInfo *II, unsigned Opcode) |

| static bool | Is16BitMemOperand (const MachineInstr &MI, unsigned Op) |

| static bool | Is32BitMemOperand (const MachineInstr &MI, unsigned Op) |

| static bool | Is64BitMemOperand (const MachineInstr &MI, unsigned Op) |

| #define DEBUG_TYPE "x86-emitter" |

Definition at line 15 of file X86CodeEmitter.cpp.

|

static |

determineREX - Determine if the MachineInstr has to be encoded with a X86-64 REX prefix which specifies 1) 64-bit instructions, 2) non-default operand size, and 3) use of X86-64 extended registers.

Definition at line 162 of file X86CodeEmitter.cpp.

References llvm::X86::AddrNumOperands, llvm::tgtok::Bit, llvm::X86II::FormMask, llvm::MachineInstr::getDesc(), llvm::MCInstrDesc::getNumOperands(), llvm::MachineInstr::getOperand(), llvm::MCInstrDesc::getOperandConstraint(), llvm::MachineOperand::getReg(), llvm::MachineOperand::isReg(), llvm::X86InstrInfo::isX86_64ExtendedReg(), llvm::X86II::isX86_64NonExtLowByteReg(), llvm::X86II::MRM0m, llvm::X86II::MRM1m, llvm::X86II::MRM2m, llvm::X86II::MRM3m, llvm::X86II::MRM4m, llvm::X86II::MRM5m, llvm::X86II::MRM6m, llvm::X86II::MRM7m, llvm::X86II::MRMDestMem, llvm::X86II::MRMInitReg, llvm::X86II::MRMSrcMem, llvm::X86II::MRMSrcReg, llvm::X86II::Pseudo, llvm::X86II::REX_W, llvm::MCOI::TIED_TO, and llvm::MCInstrDesc::TSFlags.

|

static |

Definition at line 400 of file X86CodeEmitter.cpp.

References llvm::TargetMachine::getSubtarget(), llvm::MachineOperand::getTargetFlags(), llvm::X86Subtarget::is64Bit(), and llvm::isGlobalStubReference().

|

static |

Is16BitMemOperand - Return true if the specified instruction has a 16-bit memory operand. Op specifies the operand # of the memoperand.

Definition at line 614 of file X86CodeEmitter.cpp.

References llvm::X86::AddrBaseReg, llvm::X86::AddrIndexReg, llvm::MachineInstr::getOperand(), and llvm::MachineOperand::getReg().

|

static |

Is32BitMemOperand - Return true if the specified instruction has a 32-bit memory operand. Op specifies the operand # of the memoperand.

Definition at line 628 of file X86CodeEmitter.cpp.

References llvm::X86::AddrBaseReg, llvm::X86::AddrIndexReg, llvm::MachineInstr::getOperand(), and llvm::MachineOperand::getReg().

|

static |

Is64BitMemOperand - Return true if the specified instruction has a 64-bit memory operand. Op specifies the operand # of the memoperand.

Definition at line 643 of file X86CodeEmitter.cpp.

References llvm::X86::AddrBaseReg, llvm::X86::AddrIndexReg, llvm::MachineInstr::getOperand(), and llvm::MachineOperand::getReg().

|

static |

isDisp8 - Return true if this signed displacement fits in a 8-bit sign-extended field.

Definition at line 396 of file X86CodeEmitter.cpp.

Definition at line 360 of file X86CodeEmitter.cpp.

| STATISTIC | ( | NumEmitted | , |

| "Number of machine instructions emitted" | |||

| ) |

|

static |

Definition at line 605 of file X86CodeEmitter.cpp.

References llvm::MachineInstr::setDesc().