LLVM API Documentation

#include <MCInstrDesc.h>

Public Member Functions | |

| int | getOperandConstraint (unsigned OpNum, MCOI::OperandConstraint Constraint) const |

| Returns the value of the specific constraint if it is set. Returns -1 if it is not set. More... | |

| bool | getDeprecatedInfo (MCInst &MI, MCSubtargetInfo &STI, std::string &Info) const |

Returns true if a certain instruction is deprecated and if so returns the reason in Info. More... | |

| unsigned | getOpcode () const |

| Return the opcode number for this descriptor. More... | |

| unsigned | getNumOperands () const |

| Return the number of declared MachineOperands for this MachineInstruction. Note that variadic (isVariadic() returns true) instructions may have additional operands at the end of the list, and note that the machine instruction may include implicit register def/uses as well. More... | |

| unsigned | getNumDefs () const |

| Return the number of MachineOperands that are register definitions. Register definitions always occur at the start of the machine operand list. This is the number of "outs" in the .td file, and does not include implicit defs. More... | |

| unsigned | getFlags () const |

| Return flags of this instruction. More... | |

| bool | isVariadic () const |

| Return true if this instruction can have a variable number of operands. In this case, the variable operands will be after the normal operands but before the implicit definitions and uses (if any are present). More... | |

| bool | hasOptionalDef () const |

| Set if this instruction has an optional definition, e.g. ARM instructions which can set condition code if 's' bit is set. More... | |

| bool | isPseudo () const |

| Return true if this is a pseudo instruction that doesn't correspond to a real machine instruction. More... | |

| bool | isReturn () const |

| Return true if the instruction is a return. More... | |

| bool | isCall () const |

| Return true if the instruction is a call. More... | |

| bool | isBarrier () const |

| Returns true if the specified instruction stops control flow from executing the instruction immediately following it. Examples include unconditional branches and return instructions. More... | |

| bool | isTerminator () const |

| Returns true if this instruction part of the terminator for a basic block. Typically this is things like return and branch instructions. More... | |

| bool | isBranch () const |

| Returns true if this is a conditional, unconditional, or indirect branch. Predicates below can be used to discriminate between these cases, and the TargetInstrInfo::AnalyzeBranch method can be used to get more information. More... | |

| bool | isIndirectBranch () const |

| Return true if this is an indirect branch, such as a branch through a register. More... | |

| bool | isConditionalBranch () const |

| Return true if this is a branch which may fall through to the next instruction or may transfer control flow to some other block. The TargetInstrInfo::AnalyzeBranch method can be used to get more information about this branch. More... | |

| bool | isUnconditionalBranch () const |

| Return true if this is a branch which always transfers control flow to some other block. The TargetInstrInfo::AnalyzeBranch method can be used to get more information about this branch. More... | |

| bool | mayAffectControlFlow (const MCInst &MI, const MCRegisterInfo &RI) const |

| Return true if this is a branch or an instruction which directly writes to the program counter. Considered 'may' affect rather than 'does' affect as things like predication are not taken into account. More... | |

| bool | isPredicable () const |

| Return true if this instruction has a predicate operand that controls execution. It may be set to 'always', or may be set to other values. There are various methods in TargetInstrInfo that can be used to control and modify the predicate in this instruction. More... | |

| bool | isCompare () const |

| Return true if this instruction is a comparison. More... | |

| bool | isMoveImmediate () const |

| Return true if this instruction is a move immediate (including conditional moves) instruction. More... | |

| bool | isBitcast () const |

| Return true if this instruction is a bitcast instruction. More... | |

| bool | isSelect () const |

| Return true if this is a select instruction. More... | |

| bool | isNotDuplicable () const |

| Return true if this instruction cannot be safely duplicated. For example, if the instruction has a unique labels attached to it, duplicating it would cause multiple definition errors. More... | |

| bool | hasDelaySlot () const |

| bool | canFoldAsLoad () const |

| bool | mayLoad () const |

| Return true if this instruction could possibly read memory. Instructions with this flag set are not necessarily simple load instructions, they may load a value and modify it, for example. More... | |

| bool | mayStore () const |

| Return true if this instruction could possibly modify memory. Instructions with this flag set are not necessarily simple store instructions, they may store a modified value based on their operands, or may not actually modify anything, for example. More... | |

| bool | hasUnmodeledSideEffects () const |

| bool | isCommutable () const |

| bool | isConvertibleTo3Addr () const |

| bool | usesCustomInsertionHook () const |

| bool | hasPostISelHook () const |

| bool | isRematerializable () const |

| bool | isAsCheapAsAMove () const |

| bool | hasExtraSrcRegAllocReq () const |

| bool | hasExtraDefRegAllocReq () const |

| const uint16_t * | getImplicitUses () const |

| unsigned | getNumImplicitUses () const |

| Return the number of implicit uses this instruction has. More... | |

| const uint16_t * | getImplicitDefs () const |

| unsigned | getNumImplicitDefs () const |

| Return the number of implicit defs this instruct has. More... | |

| bool | hasImplicitUseOfPhysReg (unsigned Reg) const |

| Return true if this instruction implicitly uses the specified physical register. More... | |

| bool | hasImplicitDefOfPhysReg (unsigned Reg, const MCRegisterInfo *MRI=0) const |

| Return true if this instruction implicitly defines the specified physical register. More... | |

| bool | hasDefOfPhysReg (const MCInst &MI, unsigned Reg, const MCRegisterInfo &RI) const |

| Return true if this instruction defines the specified physical register, either explicitly or implicitly. More... | |

| unsigned | getSchedClass () const |

| Return the scheduling class for this instruction. The scheduling class is an index into the InstrItineraryData table. This returns zero if there is no known scheduling information for the instruction. More... | |

| unsigned | getSize () const |

| Return the number of bytes in the encoding of this instruction, or zero if the encoding size cannot be known from the opcode. More... | |

| int | findFirstPredOperandIdx () const |

| Find the index of the first operand in the operand list that is used to represent the predicate. It returns -1 if none is found. More... | |

Public Attributes | |

| unsigned short | Opcode |

| unsigned short | NumOperands |

| unsigned short | NumDefs |

| unsigned short | SchedClass |

| unsigned short | Size |

| unsigned | Flags |

| uint64_t | TSFlags |

| const uint16_t * | ImplicitUses |

| const uint16_t * | ImplicitDefs |

| const MCOperandInfo * | OpInfo |

| uint64_t | DeprecatedFeatureMask |

| bool(* | ComplexDeprecationInfo )(MCInst &, MCSubtargetInfo &, std::string &) |

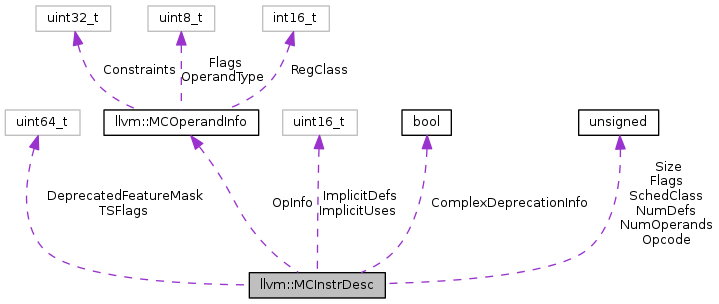

MCInstrDesc - Describe properties that are true of each instruction in the target description file. This captures information about side effects, register use and many other things. There is one instance of this struct for each target instruction class, and the MachineInstr class points to this struct directly to describe itself.

Definition at line 137 of file MCInstrDesc.h.

|

inline |

canFoldAsLoad - Return true for instructions that can be folded as memory operands in other instructions. The most common use for this is instructions that are simple loads from memory that don't modify the loaded value in any way, but it can also be used for instructions that can be expressed as constant-pool loads, such as V_SETALLONES on x86, to allow them to be folded when it is beneficial. This should only be set on instructions that return a value in their only virtual register definition.

Definition at line 356 of file MCInstrDesc.h.

References Flags, and llvm::MCID::FoldableAsLoad.

|

inline |

Find the index of the first operand in the operand list that is used to represent the predicate. It returns -1 if none is found.

Definition at line 583 of file MCInstrDesc.h.

References getNumOperands(), isPredicable(), and OpInfo.

|

inline |

Returns true if a certain instruction is deprecated and if so returns the reason in Info.

Definition at line 168 of file MCInstrDesc.h.

References ComplexDeprecationInfo, DeprecatedFeatureMask, and llvm::MCSubtargetInfo::getFeatureBits().

|

inline |

Return flags of this instruction.

Definition at line 203 of file MCInstrDesc.h.

References Flags.

Referenced by llvm::MachineInstr::hasProperty().

|

inline |

getImplicitDefs - Return a list of registers that are potentially written by any instance of this machine instruction. For example, on X86, many instructions implicitly set the flags register. In this case, they are marked as setting the FLAGS. Likewise, many instructions always deposit their result in a physical register. For example, the X86 divide instruction always deposits the quotient and remainder in the EAX/EDX registers. For that instruction, this will return a list containing the EAX/EDX/EFLAGS registers.

This method returns null if the instruction has no implicit defs.

Definition at line 523 of file MCInstrDesc.h.

References ImplicitDefs.

Referenced by getPhysicalRegisterVT(), HasImplicitCPSRDef(), and llvm::PPCInstrInfo::optimizeCompareInstr().

|

inline |

getImplicitUses - Return a list of registers that are potentially read by any instance of this machine instruction. For example, on X86, the "adc" instruction adds two register operands and adds the carry bit in from the flags register. In this case, the instruction is marked as implicitly reading the flags. Likewise, the variable shift instruction on X86 is marked as implicitly reading the 'CL' register, which it always does.

This method returns null if the instruction has no implicit uses.

Definition at line 501 of file MCInstrDesc.h.

References ImplicitUses.

Referenced by llvm::PPCInstrInfo::optimizeCompareInstr().

|

inline |

Return the number of MachineOperands that are register definitions. Register definitions always occur at the start of the machine operand list. This is the number of "outs" in the .td file, and does not include implicit defs.

Definition at line 198 of file MCInstrDesc.h.

References NumDefs.

Referenced by CheckForPhysRegDependency(), llvm::TargetInstrInfo::commuteInstruction(), llvm::FastISel::FastEmitInst_i(), llvm::FastISel::FastEmitInst_ii(), llvm::FastISel::FastEmitInst_r(), llvm::FastISel::FastEmitInst_rf(), llvm::FastISel::FastEmitInst_ri(), llvm::FastISel::FastEmitInst_rii(), llvm::FastISel::FastEmitInst_rr(), llvm::FastISel::FastEmitInst_rri(), llvm::FastISel::FastEmitInst_rrii(), llvm::FastISel::FastEmitInst_rrr(), getCopyOrBitcastDefUseIdx(), getPhysicalRegisterVT(), llvm::ARMTargetLowering::getSchedulingPreference(), llvm::ResourcePriorityQueue::initNumRegDefsLeft(), and llvm::X86InstrInfo::unfoldMemoryOperand().

|

inline |

Return the number of implicit defs this instruct has.

Definition at line 528 of file MCInstrDesc.h.

References ImplicitDefs.

|

inline |

Return the number of implicit uses this instruction has.

Definition at line 506 of file MCInstrDesc.h.

References ImplicitUses.

|

inline |

Return the number of declared MachineOperands for this MachineInstruction. Note that variadic (isVariadic() returns true) instructions may have additional operands at the end of the list, and note that the machine instruction may include implicit register def/uses as well.

Definition at line 190 of file MCInstrDesc.h.

References NumOperands.

Referenced by llvm::ARMTargetLowering::AdjustInstrPostInstrSelection(), llvm::X86InstrInfo::canFoldMemoryOperand(), llvm::ARMBaseInstrInfo::convertToThreeAddress(), llvm::MachineInstr::copyImplicitOps(), llvm::PPCInstrInfo::copyPhysReg(), determineREX(), Expand2AddrUndef(), findFirstPredOperandIdx(), llvm::PPCInstrInfo::FoldImmediate(), llvm::ARMBaseInstrInfo::FoldImmediate(), llvm::X86InstrInfo::foldMemoryOperandImpl(), FuseTwoAddrInst(), getCopyOrBitcastDefUseIdx(), llvm::ARMBaseInstrInfo::GetInstSizeInBytes(), getLSMultipleTransferSize(), getMemoryOpOffset(), llvm::ARMBaseInstrInfo::getNumMicroOps(), llvm::X86II::getOperandBias(), llvm::SIInstrInfo::getOpRegClass(), llvm::TargetInstrInfo::getRegClass(), getTargetMBB(), llvm::X86InstrInfo::optimizeLoadInstr(), and llvm::ARMBaseInstrInfo::setExecutionDomain().

|

inline |

Return the opcode number for this descriptor.

Definition at line 181 of file MCInstrDesc.h.

References Opcode.

Referenced by adjustDefLatency(), llvm::MSP430InstrInfo::GetInstSizeInBytes(), llvm::ARMBaseInstrInfo::getOperandLatency(), and hasRAWHazard().

|

inline |

Returns the value of the specific constraint if it is set. Returns -1 if it is not set.

Definition at line 156 of file MCInstrDesc.h.

References llvm::MCOperandInfo::Constraints, NumOperands, and OpInfo.

Referenced by llvm::X86InstrInfo::canFoldMemoryOperand(), llvm::PPCInstrInfo::commuteInstruction(), llvm::TargetInstrInfo::commuteInstruction(), determineREX(), DetermineREXPrefix(), llvm::X86InstrInfo::foldMemoryOperandImpl(), and llvm::X86II::getOperandBias().

|

inline |

Return the scheduling class for this instruction. The scheduling class is an index into the InstrItineraryData table. This returns zero if there is no known scheduling information for the instruction.

Definition at line 570 of file MCInstrDesc.h.

References SchedClass.

Referenced by llvm::DFAPacketizer::canReserveResources(), llvm::TargetSchedModel::computeOperandLatency(), llvm::TargetInstrInfo::computeOperandLatency(), llvm::ScoreboardHazardRecognizer::EmitInstruction(), llvm::ScoreboardHazardRecognizer::getHazardType(), llvm::TargetInstrInfo::getInstrLatency(), getItineraryLatency(), getLatency(), llvm::TargetSchedModel::getNumMicroOps(), llvm::ARMBaseInstrInfo::getNumMicroOps(), llvm::TargetInstrInfo::getNumMicroOps(), getNumMicroOpsSwiftLdSt(), llvm::ARMBaseInstrInfo::getOperandLatency(), llvm::TargetInstrInfo::getOperandLatency(), llvm::ARMTargetLowering::getSchedulingPreference(), llvm::TargetInstrInfo::hasLowDefLatency(), llvm::DFAPacketizer::reserveResources(), and llvm::TargetSchedModel::resolveSchedClass().

|

inline |

Return the number of bytes in the encoding of this instruction, or zero if the encoding size cannot be known from the opcode.

Definition at line 576 of file MCInstrDesc.h.

References Size.

Referenced by llvm::AArch64InstrInfo::getInstSizeInBytes(), llvm::MipsInstrInfo::GetInstSizeInBytes(), llvm::ARMBaseInstrInfo::GetInstSizeInBytes(), and llvm::SystemZInstrInfo::getInstSizeInBytes().

|

inline |

Return true if this instruction defines the specified physical register, either explicitly or implicitly.

Definition at line 557 of file MCInstrDesc.h.

References llvm::MCInst::getOperand(), llvm::MCOperand::getReg(), hasImplicitDefOfPhysReg(), llvm::MCOperand::isReg(), llvm::MCRegisterInfo::isSubRegisterEq(), and NumDefs.

Referenced by mayAffectControlFlow().

|

inline |

hasDelaySlot - Returns true if the specified instruction has a delay slot which must be filled by the code generator.

Definition at line 344 of file MCInstrDesc.h.

References llvm::MCID::DelaySlot, and Flags.

|

inline |

hasExtraDefRegAllocReq - Returns true if this instruction def operands have special register allocation requirements that are not captured by the operand register classes. e.g. ARM::LDRD's two def registers must be an even / odd pair, ARM::LDM registers have to be in ascending order. Post-register allocation passes should not attempt to change allocations for definitions of instructions with this flag.

Definition at line 487 of file MCInstrDesc.h.

References llvm::MCID::ExtraDefRegAllocReq, and Flags.

|

inline |

hasExtraSrcRegAllocReq - Returns true if this instruction source operands have special register allocation requirements that are not captured by the operand register classes. e.g. ARM::STRD's two source registers must be an even / odd pair, ARM::STM registers have to be in ascending order. Post-register allocation passes should not attempt to change allocations for sources of instructions with this flag.

Definition at line 477 of file MCInstrDesc.h.

References llvm::MCID::ExtraSrcRegAllocReq, and Flags.

|

inline |

Return true if this instruction implicitly defines the specified physical register.

Definition at line 546 of file MCInstrDesc.h.

References ImplicitDefs, and MRI.

Referenced by hasDefOfPhysReg().

Return true if this instruction implicitly uses the specified physical register.

Definition at line 537 of file MCInstrDesc.h.

References ImplicitUses.

|

inline |

Set if this instruction has an optional definition, e.g. ARM instructions which can set condition code if 's' bit is set.

Definition at line 215 of file MCInstrDesc.h.

References Flags, and llvm::MCID::HasOptionalDef.

Referenced by llvm::ARMBaseInstrInfo::FoldImmediate().

|

inline |

hasPostISelHook - Return true if this instruction requires adjustment after instruction selection by calling a target hook. For example, this can be used to fill in ARM 's' optional operand depending on whether the conditional flag register is used.

Definition at line 449 of file MCInstrDesc.h.

References Flags, and llvm::MCID::HasPostISelHook.

|

inline |

hasUnmodeledSideEffects - Return true if this instruction has side effects that are not modeled by other flags. This does not return true for instructions whose effects are captured by:

Examples of side effects would be modifying 'invisible' machine state like a control register, flushing a cache, modifying a register invisible to LLVM, etc.

Definition at line 393 of file MCInstrDesc.h.

References Flags, and llvm::MCID::UnmodeledSideEffects.

|

inline |

isAsCheapAsAMove - Returns true if this instruction has the same cost (or less) than a move instruction. This is useful during certain types of optimizations (e.g., remat during two-address conversion or machine licm) where we would like to remat or hoist the instruction, but not if it costs more than moving the instruction into the appropriate register. Note, we are not marking copies from and to the same register class with this flag.

Definition at line 467 of file MCInstrDesc.h.

References llvm::MCID::CheapAsAMove, and Flags.

|

inline |

Returns true if the specified instruction stops control flow from executing the instruction immediately following it. Examples include unconditional branches and return instructions.

Definition at line 239 of file MCInstrDesc.h.

References llvm::MCID::Barrier, and Flags.

Referenced by isConditionalBranch(), and isUnconditionalBranch().

|

inline |

Return true if this instruction is a bitcast instruction.

Definition at line 326 of file MCInstrDesc.h.

References llvm::MCID::Bitcast, and Flags.

|

inline |

Returns true if this is a conditional, unconditional, or indirect branch. Predicates below can be used to discriminate between these cases, and the TargetInstrInfo::AnalyzeBranch method can be used to get more information.

Definition at line 257 of file MCInstrDesc.h.

References llvm::MCID::Branch, and Flags.

Referenced by llvm::HexagonInstrInfo::isBranch(), isConditionalBranch(), isUnconditionalBranch(), and mayAffectControlFlow().

|

inline |

Return true if the instruction is a call.

Definition at line 232 of file MCInstrDesc.h.

References llvm::MCID::Call, and Flags.

Referenced by IsControlFlow(), mayAffectControlFlow(), llvm::SelectionDAGISel::runOnMachineFunction(), and llvm::ResourcePriorityQueue::SUSchedulingCost().

|

inline |

isCommutable - Return true if this may be a 2- or 3-address instruction (of the form "X = op Y, Z, ..."), which produces the same result if Y and Z are exchanged. If this flag is set, then the TargetInstrInfo::commuteInstruction method may be used to hack on the instruction.

Note that this flag may be set on instructions that are only commutable sometimes. In these cases, the call to commuteInstruction will fail. Also note that some instructions require non-trivial modification to commute them.

Definition at line 411 of file MCInstrDesc.h.

References llvm::MCID::Commutable, and Flags.

|

inline |

Return true if this instruction is a comparison.

Definition at line 315 of file MCInstrDesc.h.

References llvm::MCID::Compare, and Flags.

|

inline |

Return true if this is a branch which may fall through to the next instruction or may transfer control flow to some other block. The TargetInstrInfo::AnalyzeBranch method can be used to get more information about this branch.

Definition at line 271 of file MCInstrDesc.h.

References isBarrier(), isBranch(), and isIndirectBranch().

|

inline |

isConvertibleTo3Addr - Return true if this is a 2-address instruction which can be changed into a 3-address instruction if needed. Doing this transformation can be profitable in the register allocator, because it means that the instruction can use a 2-address form if possible, but degrade into a less efficient form if the source and dest register cannot be assigned to the same register. For example, this allows the x86 backend to turn a "shl reg, 3" instruction into an LEA instruction, which is the same speed as the shift but has bigger code size.

If this returns true, then the target must implement the TargetInstrInfo::convertToThreeAddress method for this instruction, which is allowed to fail if the transformation isn't valid for this specific instruction (e.g. shl reg, 4 on x86).

Definition at line 429 of file MCInstrDesc.h.

References llvm::MCID::ConvertibleTo3Addr, and Flags.

|

inline |

Return true if this is an indirect branch, such as a branch through a register.

Definition at line 263 of file MCInstrDesc.h.

References Flags, and llvm::MCID::IndirectBranch.

Referenced by isConditionalBranch(), isUnconditionalBranch(), and mayAffectControlFlow().

|

inline |

Return true if this instruction is a move immediate (including conditional moves) instruction.

Definition at line 321 of file MCInstrDesc.h.

References Flags, and llvm::MCID::MoveImm.

|

inline |

Return true if this instruction cannot be safely duplicated. For example, if the instruction has a unique labels attached to it, duplicating it would cause multiple definition errors.

Definition at line 338 of file MCInstrDesc.h.

References Flags, and llvm::MCID::NotDuplicable.

|

inline |

Return true if this instruction has a predicate operand that controls execution. It may be set to 'always', or may be set to other values. There are various methods in TargetInstrInfo that can be used to control and modify the predicate in this instruction.

Definition at line 310 of file MCInstrDesc.h.

References Flags, and llvm::MCID::Predicable.

Referenced by findFirstPredOperandIdx(), llvm::MachineInstr::findFirstPredOperandIdx(), llvm::HexagonInstrInfo::isPredicable(), llvm::AMDGPUInstrInfo::isPredicable(), and llvm::TargetInstrInfo::isPredicable().

|

inline |

Return true if this is a pseudo instruction that doesn't correspond to a real machine instruction.

Definition at line 222 of file MCInstrDesc.h.

References Flags, and llvm::MCID::Pseudo.

Referenced by llvm::PPCInstrInfo::FoldImmediate(), and llvm::HexagonMCInst::isCanon().

|

inline |

isRematerializable - Returns true if this instruction is a candidate for remat. This flag is deprecated, please don't use it anymore. If this flag is set, the isReallyTriviallyReMaterializable() method is called to verify the instruction is really rematable.

Definition at line 457 of file MCInstrDesc.h.

References Flags, and llvm::MCID::Rematerializable.

Referenced by llvm::TargetInstrInfo::isTriviallyReMaterializable().

|

inline |

Return true if the instruction is a return.

Definition at line 227 of file MCInstrDesc.h.

References Flags, and llvm::MCID::Return.

Referenced by mayAffectControlFlow(), and llvm::SelectionDAGISel::runOnMachineFunction().

|

inline |

Return true if this is a select instruction.

Definition at line 331 of file MCInstrDesc.h.

References Flags, and llvm::MCID::Select.

Referenced by llvm::TargetInstrInfo::analyzeSelect().

|

inline |

Returns true if this instruction part of the terminator for a basic block. Typically this is things like return and branch instructions.

Various passes use this to insert code into the bottom of a basic block, but before control flow occurs.

Definition at line 249 of file MCInstrDesc.h.

References Flags, and llvm::MCID::Terminator.

Referenced by IsControlFlow(), and llvm::HexagonInstrInfo::isSchedulingBoundary().

|

inline |

Return true if this is a branch which always transfers control flow to some other block. The TargetInstrInfo::AnalyzeBranch method can be used to get more information about this branch.

Definition at line 279 of file MCInstrDesc.h.

References isBarrier(), isBranch(), and isIndirectBranch().

|

inline |

Return true if this instruction can have a variable number of operands. In this case, the variable operands will be after the normal operands but before the implicit definitions and uses (if any are present).

Definition at line 209 of file MCInstrDesc.h.

References Flags, and llvm::MCID::Variadic.

|

inline |

Return true if this is a branch or an instruction which directly writes to the program counter. Considered 'may' affect rather than 'does' affect as things like predication are not taken into account.

Definition at line 286 of file MCInstrDesc.h.

References llvm::MCInst::getNumOperands(), llvm::MCInst::getOperand(), llvm::MCRegisterInfo::getProgramCounter(), llvm::MCOperand::getReg(), hasDefOfPhysReg(), isBranch(), isCall(), isIndirectBranch(), llvm::MCOperand::isReg(), isReturn(), llvm::MCRegisterInfo::isSubRegisterEq(), and NumOperands.

|

inline |

Return true if this instruction could possibly read memory. Instructions with this flag set are not necessarily simple load instructions, they may load a value and modify it, for example.

Definition at line 367 of file MCInstrDesc.h.

References Flags, and llvm::MCID::MayLoad.

Referenced by llvm::addFrameReference(), llvm::HexagonInstrInfo::getNonExtOpcode(), llvm::ARMBaseInstrInfo::getNumMicroOps(), llvm::ARMBaseInstrInfo::getOperandLatency(), GetPostIncrementOperand(), llvm::HexagonInstrInfo::NonExtEquivalentExists(), and llvm::SelectionDAGISel::SelectCodeCommon().

|

inline |

Return true if this instruction could possibly modify memory. Instructions with this flag set are not necessarily simple store instructions, they may store a modified value based on their operands, or may not actually modify anything, for example.

Definition at line 376 of file MCInstrDesc.h.

References Flags, and llvm::MCID::MayStore.

Referenced by llvm::addFrameReference(), llvm::HexagonInstrInfo::getNonExtOpcode(), llvm::ARMBaseInstrInfo::getNumMicroOps(), GetPostIncrementOperand(), llvm::HexagonInstrInfo::NonExtEquivalentExists(), and llvm::SelectionDAGISel::SelectCodeCommon().

|

inline |

usesCustomInsertionHook - Return true if this instruction requires custom insertion support when the DAG scheduler is inserting it into a machine basic block. If this is true for the instruction, it basically means that it is a pseudo instruction used at SelectionDAG time that is expanded out into magic code by the target when MachineInstrs are formed.

If this is true, the TargetLoweringInfo::InsertAtEndOfBasicBlock method is used to insert this into the MachineBasicBlock.

Definition at line 441 of file MCInstrDesc.h.

References Flags, and llvm::MCID::UsesCustomInserter.

| bool(* llvm::MCInstrDesc::ComplexDeprecationInfo)(MCInst &, MCSubtargetInfo &, std::string &) |

Definition at line 152 of file MCInstrDesc.h.

Referenced by getDeprecatedInfo().

| uint64_t llvm::MCInstrDesc::DeprecatedFeatureMask |

Definition at line 149 of file MCInstrDesc.h.

Referenced by getDeprecatedInfo().

| unsigned llvm::MCInstrDesc::Flags |

Definition at line 144 of file MCInstrDesc.h.

Referenced by canFoldAsLoad(), getFlags(), hasDelaySlot(), hasExtraDefRegAllocReq(), hasExtraSrcRegAllocReq(), hasOptionalDef(), hasPostISelHook(), hasUnmodeledSideEffects(), isAsCheapAsAMove(), isBarrier(), isBitcast(), isBranch(), isCall(), isCommutable(), isCompare(), isConvertibleTo3Addr(), isIndirectBranch(), isMoveImmediate(), isNotDuplicable(), isPredicable(), isPseudo(), isRematerializable(), isReturn(), isSelect(), isTerminator(), isVariadic(), mayLoad(), mayStore(), and usesCustomInsertionHook().

| const uint16_t* llvm::MCInstrDesc::ImplicitDefs |

Definition at line 147 of file MCInstrDesc.h.

Referenced by CheckForPhysRegDependency(), llvm::FastISel::FastEmitInst_i(), llvm::FastISel::FastEmitInst_ii(), llvm::FastISel::FastEmitInst_r(), llvm::FastISel::FastEmitInst_rf(), llvm::FastISel::FastEmitInst_ri(), llvm::FastISel::FastEmitInst_rii(), llvm::FastISel::FastEmitInst_rr(), llvm::FastISel::FastEmitInst_rri(), llvm::FastISel::FastEmitInst_rrii(), llvm::FastISel::FastEmitInst_rrr(), getImplicitDefs(), getNumImplicitDefs(), getPhysicalRegisterVT(), hasImplicitDefOfPhysReg(), llvm::SIInstrInfo::moveToVALU(), and llvm::PPCInstrInfo::optimizeCompareInstr().

| const uint16_t* llvm::MCInstrDesc::ImplicitUses |

Definition at line 146 of file MCInstrDesc.h.

Referenced by getImplicitUses(), getNumImplicitUses(), hasImplicitUseOfPhysReg(), llvm::SIInstrInfo::moveToVALU(), and llvm::PPCInstrInfo::optimizeCompareInstr().

| unsigned short llvm::MCInstrDesc::NumDefs |

Definition at line 141 of file MCInstrDesc.h.

Referenced by getNumDefs(), hasDefOfPhysReg(), and llvm::X86InstrInfo::unfoldMemoryOperand().

| unsigned short llvm::MCInstrDesc::NumOperands |

Definition at line 140 of file MCInstrDesc.h.

Referenced by AddThumb1SBit(), getNumOperands(), getOperandConstraint(), and mayAffectControlFlow().

| unsigned short llvm::MCInstrDesc::Opcode |

Definition at line 139 of file MCInstrDesc.h.

Referenced by llvm::ScoreboardHazardRecognizer::EmitInstruction(), getOpcode(), llvm::MachineInstr::getOpcode(), and llvm::ARMBaseInstrInfo::getOperandLatency().

| const MCOperandInfo* llvm::MCInstrDesc::OpInfo |

Definition at line 148 of file MCInstrDesc.h.

Referenced by AddThumb1SBit(), llvm::ARMTargetLowering::AdjustInstrPostInstrSelection(), llvm::TargetSchedModel::computeOperandLatency(), findFirstPredOperandIdx(), llvm::MachineInstr::findFirstPredOperandIdx(), llvm::PPCInstrInfo::FoldImmediate(), getOperandConstraint(), llvm::SIInstrInfo::getOpRegClass(), and llvm::TargetInstrInfo::getRegClass().

| unsigned short llvm::MCInstrDesc::SchedClass |

Definition at line 142 of file MCInstrDesc.h.

Referenced by getSchedClass().

| unsigned short llvm::MCInstrDesc::Size |

Definition at line 143 of file MCInstrDesc.h.

Referenced by getSize().

| uint64_t llvm::MCInstrDesc::TSFlags |

Definition at line 145 of file MCInstrDesc.h.

Referenced by llvm::ARMBaseInstrInfo::convertToThreeAddress(), determineREX(), llvm::ARMBaseRegisterInfo::eliminateFrameIndex(), llvm::SystemZInstrInfo::foldMemoryOperandImpl(), llvm::HexagonInstrInfo::getAddrMode(), llvm::HexagonMCInst::getBitCount(), llvm::HexagonMCInst::getCExtOpNum(), llvm::HexagonInstrInfo::getCExtOpNum(), llvm::ARMBaseInstrInfo::getExecutionDomain(), llvm::X86InstrInfo::getExecutionDomain(), llvm::ARMBaseRegisterInfo::getFrameIndexInstrOffset(), llvm::ARMHazardRecognizer::getHazardType(), llvm::MSP430InstrInfo::GetInstSizeInBytes(), llvm::HexagonInstrInfo::getMaxValue(), llvm::HexagonInstrInfo::getMinValue(), llvm::HexagonMCInst::getNewValue(), llvm::SystemZInstrInfo::getOpcodeForOffset(), getTruncatedShiftCount(), llvm::HexagonMCInst::getType(), llvm::HexagonMCInst::hasNewValue(), hasRAWHazard(), llvm::HexagonInstrInfo::isConstExtended(), llvm::HexagonInstrInfo::isExtendable(), llvm::HexagonInstrInfo::isExtended(), llvm::ARMBaseRegisterInfo::isFrameOffsetLegal(), llvm::NVPTXInstrInfo::isLoadInstr(), llvm::NVPTXInstrInfo::isMoveInstr(), llvm::HexagonMCInst::isNewValue(), llvm::HexagonInstrInfo::isNewValue(), llvm::HexagonInstrInfo::isNewValueStore(), llvm::HexagonInstrInfo::isOperandExtended(), llvm::ARMBaseInstrInfo::isPredicable(), llvm::HexagonInstrInfo::isPredicated(), llvm::HexagonInstrInfo::isPredicatedNew(), llvm::HexagonInstrInfo::isPredicatedTrue(), isSimpleBD12Move(), isSimpleMove(), llvm::HexagonMCInst::isSolo(), llvm::NVPTXInstrInfo::isStoreInstr(), llvm::HexagonInstrInfo::mayBeNewStore(), llvm::SystemZInstrInfo::optimizeCompareInstr(), llvm::X86ATTInstPrinter::printInst(), llvm::X86IntelInstPrinter::printInst(), llvm::rewriteARMFrameIndex(), llvm::Thumb1RegisterInfo::rewriteFrameIndex(), llvm::rewriteT2FrameIndex(), and llvm::X86InstrInfo::setExecutionDomain().