LLVM API Documentation

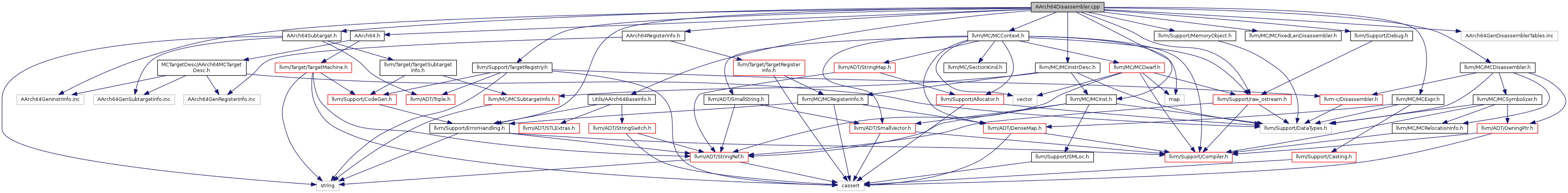

#include "AArch64.h"#include "AArch64RegisterInfo.h"#include "AArch64Subtarget.h"#include "Utils/AArch64BaseInfo.h"#include "llvm/MC/MCInst.h"#include "llvm/MC/MCInstrDesc.h"#include "llvm/MC/MCExpr.h"#include "llvm/MC/MCContext.h"#include "llvm/MC/MCDisassembler.h"#include "llvm/MC/MCFixedLenDisassembler.h"#include "llvm/Support/Debug.h"#include "llvm/Support/MemoryObject.h"#include "llvm/Support/ErrorHandling.h"#include "llvm/Support/TargetRegistry.h"#include "llvm/Support/raw_ostream.h"#include "AArch64GenDisassemblerTables.inc"#include "AArch64GenInstrInfo.inc"

Go to the source code of this file.

Macros | |

| #define | DEBUG_TYPE "arm-disassembler" |

Typedefs | |

| typedef MCDisassembler::DecodeStatus | DecodeStatus |

Functions | |

| static DecodeStatus | DecodeGPR64RegisterClass (llvm::MCInst &Inst, unsigned RegNo, uint64_t Address, const void *Decoder) |

| static DecodeStatus | DecodeGPR64xspRegisterClass (llvm::MCInst &Inst, unsigned RegNo, uint64_t Address, const void *Decoder) |

| static DecodeStatus | DecodeGPR32RegisterClass (llvm::MCInst &Inst, unsigned RegNo, uint64_t Address, const void *Decoder) |

| static DecodeStatus | DecodeGPR32wspRegisterClass (llvm::MCInst &Inst, unsigned RegNo, uint64_t Address, const void *Decoder) |

| static DecodeStatus | DecodeFPR8RegisterClass (llvm::MCInst &Inst, unsigned RegNo, uint64_t Address, const void *Decoder) |

| static DecodeStatus | DecodeFPR16RegisterClass (llvm::MCInst &Inst, unsigned RegNo, uint64_t Address, const void *Decoder) |

| static DecodeStatus | DecodeFPR32RegisterClass (llvm::MCInst &Inst, unsigned RegNo, uint64_t Address, const void *Decoder) |

| static DecodeStatus | DecodeFPR64RegisterClass (llvm::MCInst &Inst, unsigned RegNo, uint64_t Address, const void *Decoder) |

| static DecodeStatus | DecodeFPR64LoRegisterClass (llvm::MCInst &Inst, unsigned RegNo, uint64_t Address, const void *Decoder) |

| static DecodeStatus | DecodeFPR128RegisterClass (llvm::MCInst &Inst, unsigned RegNo, uint64_t Address, const void *Decoder) |

| static DecodeStatus | DecodeFPR128LoRegisterClass (llvm::MCInst &Inst, unsigned RegNo, uint64_t Address, const void *Decoder) |

| static DecodeStatus | DecodeGPR64noxzrRegisterClass (llvm::MCInst &Inst, unsigned RegNo, uint64_t Address, const void *Decoder) |

| static DecodeStatus | DecodeDPairRegisterClass (llvm::MCInst &Inst, unsigned RegNo, uint64_t Address, const void *Decoder) |

| static DecodeStatus | DecodeQPairRegisterClass (llvm::MCInst &Inst, unsigned RegNo, uint64_t Address, const void *Decoder) |

| static DecodeStatus | DecodeDTripleRegisterClass (llvm::MCInst &Inst, unsigned RegNo, uint64_t Address, const void *Decoder) |

| static DecodeStatus | DecodeQTripleRegisterClass (llvm::MCInst &Inst, unsigned RegNo, uint64_t Address, const void *Decoder) |

| static DecodeStatus | DecodeDQuadRegisterClass (llvm::MCInst &Inst, unsigned RegNo, uint64_t Address, const void *Decoder) |

| static DecodeStatus | DecodeQQuadRegisterClass (llvm::MCInst &Inst, unsigned RegNo, uint64_t Address, const void *Decoder) |

| static DecodeStatus | DecodeAddrRegExtendOperand (llvm::MCInst &Inst, unsigned OptionHiS, uint64_t Address, const void *Decoder) |

| static DecodeStatus | DecodeBitfield32ImmOperand (llvm::MCInst &Inst, unsigned Imm6Bits, uint64_t Address, const void *Decoder) |

| static DecodeStatus | DecodeCVT32FixedPosOperand (llvm::MCInst &Inst, unsigned Imm6Bits, uint64_t Address, const void *Decoder) |

| static DecodeStatus | DecodeFPZeroOperand (llvm::MCInst &Inst, unsigned RmBits, uint64_t Address, const void *Decoder) |

| static DecodeStatus | DecodeShiftRightImm8 (MCInst &Inst, unsigned Val, uint64_t Address, const void *Decoder) |

| static DecodeStatus | DecodeShiftRightImm16 (MCInst &Inst, unsigned Val, uint64_t Address, const void *Decoder) |

| static DecodeStatus | DecodeShiftRightImm32 (MCInst &Inst, unsigned Val, uint64_t Address, const void *Decoder) |

| static DecodeStatus | DecodeShiftRightImm64 (MCInst &Inst, unsigned Val, uint64_t Address, const void *Decoder) |

| static DecodeStatus | DecodeShiftLeftImm8 (MCInst &Inst, unsigned Val, uint64_t Address, const void *Decoder) |

| static DecodeStatus | DecodeShiftLeftImm16 (MCInst &Inst, unsigned Val, uint64_t Address, const void *Decoder) |

| static DecodeStatus | DecodeShiftLeftImm32 (MCInst &Inst, unsigned Val, uint64_t Address, const void *Decoder) |

| static DecodeStatus | DecodeShiftLeftImm64 (MCInst &Inst, unsigned Val, uint64_t Address, const void *Decoder) |

| template<int RegWidth> | |

| static DecodeStatus | DecodeMoveWideImmOperand (llvm::MCInst &Inst, unsigned FullImm, uint64_t Address, const void *Decoder) |

| template<int RegWidth> | |

| static DecodeStatus | DecodeLogicalImmOperand (llvm::MCInst &Inst, unsigned Bits, uint64_t Address, const void *Decoder) |

| static DecodeStatus | DecodeRegExtendOperand (llvm::MCInst &Inst, unsigned ShiftAmount, uint64_t Address, const void *Decoder) |

| template<A64SE::ShiftExtSpecifiers Ext, bool IsHalf> | |

| static DecodeStatus | DecodeNeonMovImmShiftOperand (llvm::MCInst &Inst, unsigned ShiftAmount, uint64_t Address, const void *Decoder) |

| static DecodeStatus | Decode32BitShiftOperand (llvm::MCInst &Inst, unsigned ShiftAmount, uint64_t Address, const void *Decoder) |

| static DecodeStatus | DecodeBitfieldInstruction (llvm::MCInst &Inst, unsigned Insn, uint64_t Address, const void *Decoder) |

| static DecodeStatus | DecodeFMOVLaneInstruction (llvm::MCInst &Inst, unsigned Insn, uint64_t Address, const void *Decoder) |

| static DecodeStatus | DecodeLDSTPairInstruction (llvm::MCInst &Inst, unsigned Insn, uint64_t Address, const void *Decoder) |

| static DecodeStatus | DecodeLoadPairExclusiveInstruction (llvm::MCInst &Inst, unsigned Val, uint64_t Address, const void *Decoder) |

| template<typename SomeNamedImmMapper > | |

| static DecodeStatus | DecodeNamedImmOperand (llvm::MCInst &Inst, unsigned Val, uint64_t Address, const void *Decoder) |

| static DecodeStatus | DecodeSysRegOperand (const A64SysReg::SysRegMapper &InstMapper, llvm::MCInst &Inst, unsigned Val, uint64_t Address, const void *Decoder) |

| static DecodeStatus | DecodeMRSOperand (llvm::MCInst &Inst, unsigned Val, uint64_t Address, const void *Decoder) |

| static DecodeStatus | DecodeMSROperand (llvm::MCInst &Inst, unsigned Val, uint64_t Address, const void *Decoder) |

| static DecodeStatus | DecodeSingleIndexedInstruction (llvm::MCInst &Inst, unsigned Val, uint64_t Address, const void *Decoder) |

| static DecodeStatus | DecodeVLDSTPostInstruction (MCInst &Inst, unsigned Val, uint64_t Address, const void *Decoder) |

| static DecodeStatus | DecodeVLDSTLanePostInstruction (MCInst &Inst, unsigned Insn, uint64_t Address, const void *Decoder) |

| static bool | Check (DecodeStatus &Out, DecodeStatus In) |

| static unsigned | getReg (const void *D, unsigned RC, unsigned RegNo) |

| static DecodeStatus | DecodeRegisterClassByID (llvm::MCInst &Inst, unsigned RegNo, unsigned RegID, const void *Decoder) |

| static DecodeStatus | DecodeLoadPairExclusiveInstruction (llvm::MCInst &Inst, uint32_t Val, uint64_t Address, const void *Decoder) |

| static MCDisassembler * | createAArch64Disassembler (const Target &T, const MCSubtargetInfo &STI) |

| void | LLVMInitializeAArch64Disassembler () |

| #define DEBUG_TYPE "arm-disassembler" |

Definition at line 16 of file AArch64Disassembler.cpp.

Definition at line 36 of file AArch64Disassembler.cpp.

|

static |

Definition at line 246 of file AArch64Disassembler.cpp.

References llvm::MCDisassembler::Fail, llvm::tgtok::In, llvm_unreachable, llvm::MCDisassembler::SoftFail, and llvm::MCDisassembler::Success.

Referenced by DecodeLoadPairExclusiveInstruction(), llvm::RuntimeDyldImpl::emitSection(), llvm::RuntimeDyldImpl::loadObject(), and llvm::RuntimeDyldELF::processRelocationRef().

|

static |

Definition at line 990 of file AArch64Disassembler.cpp.

References llvm::Target::createMCRegInfo().

Referenced by LLVMInitializeAArch64Disassembler().

|

static |

Definition at line 639 of file AArch64Disassembler.cpp.

References llvm::MCInst::addOperand(), llvm::MCOperand::CreateImm(), llvm::MCDisassembler::Fail, and llvm::MCDisassembler::Success.

|

static |

Definition at line 482 of file AArch64Disassembler.cpp.

References llvm::MCInst::addOperand(), llvm::MCOperand::CreateImm(), llvm::MCDisassembler::Fail, and llvm::MCDisassembler::Success.

|

static |

Definition at line 495 of file AArch64Disassembler.cpp.

References llvm::MCInst::addOperand(), llvm::MCOperand::CreateImm(), llvm::MCDisassembler::Fail, and llvm::MCDisassembler::Success.

|

static |

Definition at line 651 of file AArch64Disassembler.cpp.

References llvm::MCInst::addOperand(), llvm::MCOperand::CreateImm(), DecodeGPR32RegisterClass(), DecodeGPR64RegisterClass(), llvm::MCDisassembler::Fail, llvm_unreachable, llvm::MCInst::setOpcode(), llvm::MCDisassembler::Success, and llvm::RegState::Undef.

|

static |

Definition at line 508 of file AArch64Disassembler.cpp.

References llvm::MCInst::addOperand(), llvm::MCOperand::CreateImm(), llvm::MCDisassembler::Fail, and llvm::MCDisassembler::Success.

|

static |

Definition at line 440 of file AArch64Disassembler.cpp.

References DecodeRegisterClassByID().

Referenced by DecodeVLDSTLanePostInstruction(), and DecodeVLDSTPostInstruction().

|

static |

Definition at line 468 of file AArch64Disassembler.cpp.

References DecodeRegisterClassByID().

Referenced by DecodeVLDSTLanePostInstruction(), and DecodeVLDSTPostInstruction().

|

static |

Definition at line 454 of file AArch64Disassembler.cpp.

References DecodeRegisterClassByID().

Referenced by DecodeVLDSTLanePostInstruction(), and DecodeVLDSTPostInstruction().

|

static |

Definition at line 743 of file AArch64Disassembler.cpp.

References llvm::MCInst::addOperand(), llvm::MCOperand::CreateImm(), DecodeFPR128RegisterClass(), DecodeGPR64RegisterClass(), and llvm::MCDisassembler::Success.

|

static |

Definition at line 409 of file AArch64Disassembler.cpp.

References DecodeFPR128RegisterClass(), and llvm::MCDisassembler::Fail.

|

static |

Definition at line 398 of file AArch64Disassembler.cpp.

References llvm::MCInst::addOperand(), llvm::MCOperand::CreateReg(), llvm::MCDisassembler::Fail, getReg(), Register, and llvm::MCDisassembler::Success.

Referenced by DecodeFMOVLaneInstruction(), DecodeFPR128LoRegisterClass(), DecodeLDSTPairInstruction(), DecodeSingleIndexedInstruction(), DecodeVLDSTLanePostInstruction(), and DecodeVLDSTPostInstruction().

|

static |

Definition at line 355 of file AArch64Disassembler.cpp.

References llvm::MCInst::addOperand(), llvm::MCOperand::CreateReg(), llvm::MCDisassembler::Fail, getReg(), Register, and llvm::MCDisassembler::Success.

Referenced by DecodeSingleIndexedInstruction().

|

static |

Definition at line 367 of file AArch64Disassembler.cpp.

References llvm::MCInst::addOperand(), llvm::MCOperand::CreateReg(), llvm::MCDisassembler::Fail, getReg(), Register, and llvm::MCDisassembler::Success.

Referenced by DecodeLDSTPairInstruction(), and DecodeSingleIndexedInstruction().

|

static |

Definition at line 389 of file AArch64Disassembler.cpp.

References DecodeFPR64RegisterClass(), and llvm::MCDisassembler::Fail.

|

static |

Definition at line 378 of file AArch64Disassembler.cpp.

References llvm::MCInst::addOperand(), llvm::MCOperand::CreateReg(), llvm::MCDisassembler::Fail, getReg(), Register, and llvm::MCDisassembler::Success.

Referenced by DecodeFPR64LoRegisterClass(), DecodeLDSTPairInstruction(), DecodeSingleIndexedInstruction(), DecodeVLDSTLanePostInstruction(), and DecodeVLDSTPostInstruction().

|

static |

Definition at line 344 of file AArch64Disassembler.cpp.

References llvm::MCInst::addOperand(), llvm::MCOperand::CreateReg(), llvm::MCDisassembler::Fail, getReg(), Register, and llvm::MCDisassembler::Success.

Referenced by DecodeSingleIndexedInstruction().

|

static |

Definition at line 520 of file AArch64Disassembler.cpp.

References llvm::MCInst::addOperand(), llvm::MCOperand::CreateImm(), and llvm::MCDisassembler::Success.

|

static |

Definition at line 321 of file AArch64Disassembler.cpp.

References llvm::MCInst::addOperand(), llvm::MCOperand::CreateReg(), llvm::MCDisassembler::Fail, getReg(), Register, and llvm::MCDisassembler::Success.

Referenced by DecodeBitfieldInstruction(), DecodeLDSTPairInstruction(), DecodeLoadPairExclusiveInstruction(), and DecodeSingleIndexedInstruction().

|

static |

Definition at line 333 of file AArch64Disassembler.cpp.

References llvm::MCInst::addOperand(), llvm::MCOperand::CreateReg(), llvm::MCDisassembler::Fail, getReg(), Register, and llvm::MCDisassembler::Success.

|

static |

Definition at line 417 of file AArch64Disassembler.cpp.

References llvm::MCInst::addOperand(), llvm::MCOperand::CreateReg(), llvm::MCDisassembler::Fail, getReg(), Register, and llvm::MCDisassembler::Success.

Referenced by DecodeVLDSTLanePostInstruction(), and DecodeVLDSTPostInstruction().

|

static |

Definition at line 300 of file AArch64Disassembler.cpp.

References llvm::MCInst::addOperand(), llvm::MCOperand::CreateReg(), llvm::MCDisassembler::Fail, getReg(), Register, and llvm::MCDisassembler::Success.

Referenced by DecodeBitfieldInstruction(), DecodeFMOVLaneInstruction(), DecodeLDSTPairInstruction(), DecodeLoadPairExclusiveInstruction(), and DecodeSingleIndexedInstruction().

|

static |

Definition at line 311 of file AArch64Disassembler.cpp.

References llvm::MCInst::addOperand(), llvm::MCOperand::CreateReg(), llvm::MCDisassembler::Fail, getReg(), Register, and llvm::MCDisassembler::Success.

Referenced by DecodeLDSTPairInstruction(), DecodeLoadPairExclusiveInstruction(), DecodeSingleIndexedInstruction(), DecodeVLDSTLanePostInstruction(), and DecodeVLDSTPostInstruction().

|

static |

Definition at line 767 of file AArch64Disassembler.cpp.

References llvm::MCInst::addOperand(), llvm::MCOperand::CreateImm(), DecodeFPR128RegisterClass(), DecodeFPR32RegisterClass(), DecodeFPR64RegisterClass(), DecodeGPR32RegisterClass(), DecodeGPR64RegisterClass(), DecodeGPR64xspRegisterClass(), llvm::MCDisassembler::Fail, llvm::MCDisassembler::SoftFail, and llvm::MCDisassembler::Success.

|

static |

|

static |

Definition at line 851 of file AArch64Disassembler.cpp.

References Check(), DecodeGPR32RegisterClass(), DecodeGPR64RegisterClass(), DecodeGPR64xspRegisterClass(), llvm::MCDisassembler::Fail, llvm_unreachable, llvm::MCDisassembler::SoftFail, and llvm::MCDisassembler::Success.

|

static |

Definition at line 614 of file AArch64Disassembler.cpp.

References llvm::MCInst::addOperand(), llvm::MCOperand::CreateImm(), llvm::MCDisassembler::Fail, llvm::A64Imms::isLogicalImmBits(), and llvm::MCDisassembler::Success.

|

static |

Definition at line 599 of file AArch64Disassembler.cpp.

References llvm::MCInst::addOperand(), llvm::MCOperand::CreateImm(), llvm::MCDisassembler::Fail, llvm::X86II::Imm16, and llvm::MCDisassembler::Success.

|

static |

Definition at line 915 of file AArch64Disassembler.cpp.

References DecodeSysRegOperand().

|

static |

Definition at line 923 of file AArch64Disassembler.cpp.

References DecodeSysRegOperand().

|

static |

Definition at line 887 of file AArch64Disassembler.cpp.

References llvm::MCInst::addOperand(), llvm::MCOperand::CreateImm(), llvm::MCDisassembler::Fail, and llvm::MCDisassembler::Success.

|

static |

Definition at line 1002 of file AArch64Disassembler.cpp.

References llvm::MCInst::addOperand(), llvm::MCOperand::CreateImm(), llvm::MipsISD::Ext, llvm::MCDisassembler::Fail, llvm::A64SE::LSL, llvm::A64SE::MSL, and llvm::MCDisassembler::Success.

|

static |

Definition at line 447 of file AArch64Disassembler.cpp.

References DecodeRegisterClassByID().

Referenced by DecodeVLDSTLanePostInstruction(), and DecodeVLDSTPostInstruction().

|

static |

Definition at line 475 of file AArch64Disassembler.cpp.

References DecodeRegisterClassByID().

Referenced by DecodeVLDSTLanePostInstruction(), and DecodeVLDSTPostInstruction().

|

static |

Definition at line 461 of file AArch64Disassembler.cpp.

References DecodeRegisterClassByID().

Referenced by DecodeVLDSTLanePostInstruction(), and DecodeVLDSTPostInstruction().

|

static |

Definition at line 627 of file AArch64Disassembler.cpp.

References llvm::MCInst::addOperand(), llvm::MCOperand::CreateImm(), llvm::MCDisassembler::Fail, and llvm::MCDisassembler::Success.

|

static |

Definition at line 429 of file AArch64Disassembler.cpp.

References llvm::MCInst::addOperand(), llvm::MCOperand::CreateReg(), llvm::MCDisassembler::Fail, getReg(), Register, and llvm::MCDisassembler::Success.

Referenced by DecodeDPairRegisterClass(), DecodeDQuadRegisterClass(), DecodeDTripleRegisterClass(), DecodeQPairRegisterClass(), DecodeQQuadRegisterClass(), and DecodeQTripleRegisterClass().

|

static |

Definition at line 568 of file AArch64Disassembler.cpp.

References llvm::MCInst::addOperand(), llvm::MCOperand::CreateImm(), llvm::MCDisassembler::Fail, and llvm::MCDisassembler::Success.

|

static |

Definition at line 578 of file AArch64Disassembler.cpp.

References llvm::MCInst::addOperand(), llvm::MCOperand::CreateImm(), llvm::MCDisassembler::Fail, and llvm::MCDisassembler::Success.

|

static |

Definition at line 588 of file AArch64Disassembler.cpp.

References llvm::MCInst::addOperand(), llvm::MCOperand::CreateImm(), llvm::MCDisassembler::Fail, and llvm::MCDisassembler::Success.

|

static |

Definition at line 558 of file AArch64Disassembler.cpp.

References llvm::MCInst::addOperand(), llvm::MCOperand::CreateImm(), llvm::MCDisassembler::Fail, and llvm::MCDisassembler::Success.

|

static |

Definition at line 537 of file AArch64Disassembler.cpp.

References llvm::MCInst::addOperand(), llvm::MCOperand::CreateImm(), and llvm::MCDisassembler::Success.

|

static |

Definition at line 544 of file AArch64Disassembler.cpp.

References llvm::MCInst::addOperand(), llvm::MCOperand::CreateImm(), and llvm::MCDisassembler::Success.

|

static |

Definition at line 551 of file AArch64Disassembler.cpp.

References llvm::MCInst::addOperand(), llvm::MCOperand::CreateImm(), and llvm::MCDisassembler::Success.

|

static |

Definition at line 530 of file AArch64Disassembler.cpp.

References llvm::MCInst::addOperand(), llvm::MCOperand::CreateImm(), and llvm::MCDisassembler::Success.

|

static |

Definition at line 931 of file AArch64Disassembler.cpp.

References llvm::MCInst::addOperand(), llvm::MCOperand::CreateImm(), DecodeFPR128RegisterClass(), DecodeFPR16RegisterClass(), DecodeFPR32RegisterClass(), DecodeFPR64RegisterClass(), DecodeFPR8RegisterClass(), DecodeGPR32RegisterClass(), DecodeGPR64RegisterClass(), DecodeGPR64xspRegisterClass(), llvm::MCDisassembler::SoftFail, and llvm::MCDisassembler::Success.

|

static |

Definition at line 902 of file AArch64Disassembler.cpp.

References llvm::MCInst::addOperand(), llvm::MCOperand::CreateImm(), llvm::MCDisassembler::Fail, llvm::MCDisassembler::Success, and llvm::A64SysReg::SysRegMapper::toString().

Referenced by DecodeMRSOperand(), and DecodeMSROperand().

|

static |

Definition at line 1114 of file AArch64Disassembler.cpp.

References llvm::MCInst::addOperand(), llvm::MCOperand::CreateImm(), DecodeDPairRegisterClass(), DecodeDQuadRegisterClass(), DecodeDTripleRegisterClass(), DecodeFPR128RegisterClass(), DecodeFPR64RegisterClass(), DecodeGPR64noxzrRegisterClass(), DecodeGPR64xspRegisterClass(), DecodeQPairRegisterClass(), DecodeQQuadRegisterClass(), DecodeQTripleRegisterClass(), llvm::MCDisassembler::Fail, llvm::MCInst::getOpcode(), and llvm::MCDisassembler::Success.

|

static |

Definition at line 1026 of file AArch64Disassembler.cpp.

References llvm::MCInst::addOperand(), llvm::MCOperand::CreateImm(), DecodeDPairRegisterClass(), DecodeDQuadRegisterClass(), DecodeDTripleRegisterClass(), DecodeFPR128RegisterClass(), DecodeFPR64RegisterClass(), DecodeGPR64noxzrRegisterClass(), DecodeGPR64xspRegisterClass(), DecodeQPairRegisterClass(), DecodeQQuadRegisterClass(), DecodeQTripleRegisterClass(), llvm_unreachable, and llvm::MCDisassembler::Success.

Definition at line 295 of file AArch64Disassembler.cpp.

Referenced by AddNodeIDCustom(), llvm::PPCInstrInfo::canInsertSelect(), CC_Hexagon32_VarArgs(), CheckForPhysRegDependency(), llvm::ScheduleDAGSDNodes::computeOperandLatency(), llvm::SelectionDAGBuilder::CopyValueToVirtualRegister(), DecodeFPR128RegisterClass(), DecodeFPR16RegisterClass(), DecodeFPR32RegisterClass(), DecodeFPR64RegisterClass(), DecodeFPR8RegisterClass(), DecodeGPR32RegisterClass(), DecodeGPR32wspRegisterClass(), DecodeGPR64noxzrRegisterClass(), DecodeGPR64RegisterClass(), DecodeGPR64xspRegisterClass(), DecodeRegisterClassByID(), emitAlignedDPRCS2Restores(), llvm::AArch64FrameLowering::emitFrameMemOps(), GetCostForDef(), getTruncatedArgReg(), HasNoSignedComparisonUses(), hasOnlyLiveInOpers(), hasOnlyLiveOutUses(), llvm::XCoreInstrInfo::InsertBranch(), llvm::ARMBaseInstrInfo::InsertBranch(), llvm::HexagonInstrInfo::InsertBranch(), llvm::NVPTXInstrInfo::InsertBranch(), llvm::PPCInstrInfo::InsertBranch(), llvm::PPCInstrInfo::insertSelect(), llvm::HexagonTargetLowering::LowerINLINEASM(), MatchingStackOffset(), llvm::ARMBaseInstrInfo::PredicateInstruction(), llvm::R600InstrInfo::PredicateInstruction(), llvm::PPCInstrInfo::PredicateInstruction(), llvm::TargetInstrInfo::PredicateInstruction(), llvm::HexagonFrameLowering::restoreCalleeSavedRegisters(), RetCC_Hexagon32_VarArgs(), llvm::PPCInstrInfo::ReverseBranchCondition(), llvm::rewriteT2FrameIndex(), llvm::HexagonFrameLowering::spillCalleeSavedRegisters(), and llvm::PPCInstrInfo::SubsumesPredicate().

| void LLVMInitializeAArch64Disassembler | ( | ) |

Definition at line 995 of file AArch64Disassembler.cpp.

References createAArch64Disassembler(), llvm::TargetRegistry::RegisterMCDisassembler(), and llvm::TheAArch64Target.