LLVM API Documentation

#include <TargetSubtargetInfo.h>

Public Types | |

| enum | AntiDepBreakMode { ANTIDEP_NONE, ANTIDEP_CRITICAL, ANTIDEP_ALL } |

| typedef SmallVectorImpl< const TargetRegisterClass * > | RegClassVector |

Public Member Functions | |

| virtual | ~TargetSubtargetInfo () |

| virtual unsigned | resolveSchedClass (unsigned SchedClass, const MachineInstr *MI, const TargetSchedModel *SchedModel) const |

| bool | useMachineScheduler () const |

| Temporary API to test migration to MI scheduler. More... | |

| virtual bool | enableMachineScheduler () const |

| True if the subtarget should run MachineScheduler after aggressive coalescing. More... | |

| virtual void | overrideSchedPolicy (MachineSchedPolicy &Policy, MachineInstr *begin, MachineInstr *end, unsigned NumRegionInstrs) const |

| Override generic scheduling policy within a region. More... | |

| virtual bool | enablePostRAScheduler (CodeGenOpt::Level OptLevel, AntiDepBreakMode &Mode, RegClassVector &CriticalPathRCs) const |

| virtual void | adjustSchedDependency (SUnit *def, SUnit *use, SDep &dep) const |

| virtual bool | useAA () const |

| Enable use of alias analysis during code generation (during MI scheduling, DAGCombine, etc.). More... | |

| virtual void | resetSubtargetFeatures (const MachineFunction *MF) |

| Reset the features for the subtarget. More... | |

Public Member Functions inherited from llvm::MCSubtargetInfo Public Member Functions inherited from llvm::MCSubtargetInfo | |

| void | InitMCSubtargetInfo (StringRef TT, StringRef CPU, StringRef FS, const SubtargetFeatureKV *PF, const SubtargetFeatureKV *PD, const SubtargetInfoKV *ProcSched, const MCWriteProcResEntry *WPR, const MCWriteLatencyEntry *WL, const MCReadAdvanceEntry *RA, const InstrStage *IS, const unsigned *OC, const unsigned *FP, unsigned NF, unsigned NP) |

| StringRef | getTargetTriple () const |

| getTargetTriple - Return the target triple string. More... | |

| uint64_t | getFeatureBits () const |

| void | InitMCProcessorInfo (StringRef CPU, StringRef FS) |

| void | InitCPUSchedModel (StringRef CPU) |

| InitCPUSchedModel - Recompute scheduling model based on CPU. More... | |

| uint64_t | ToggleFeature (uint64_t FB) |

| uint64_t | ToggleFeature (StringRef FS) |

| const MCSchedModel * | getSchedModelForCPU (StringRef CPU) const |

| const MCSchedModel * | getSchedModel () const |

| const MCWriteProcResEntry * | getWriteProcResBegin (const MCSchedClassDesc *SC) const |

| const MCWriteProcResEntry * | getWriteProcResEnd (const MCSchedClassDesc *SC) const |

| const MCWriteLatencyEntry * | getWriteLatencyEntry (const MCSchedClassDesc *SC, unsigned DefIdx) const |

| int | getReadAdvanceCycles (const MCSchedClassDesc *SC, unsigned UseIdx, unsigned WriteResID) const |

| InstrItineraryData | getInstrItineraryForCPU (StringRef CPU) const |

| void | initInstrItins (InstrItineraryData &InstrItins) const |

| Initialize an InstrItineraryData instance. More... | |

Protected Member Functions | |

| TargetSubtargetInfo () | |

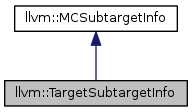

TargetSubtargetInfo - Generic base class for all target subtargets. All Target-specific options that control code generation and printing should be exposed through a TargetSubtargetInfo-derived class.

Definition at line 37 of file TargetSubtargetInfo.h.

Definition at line 46 of file TargetSubtargetInfo.h.

| Enumerator | |

|---|---|

| ANTIDEP_NONE | |

| ANTIDEP_CRITICAL | |

| ANTIDEP_ALL | |

Definition at line 45 of file TargetSubtargetInfo.h.

|

protected |

Definition at line 22 of file TargetSubtargetInfo.cpp.

|

virtual |

Definition at line 24 of file TargetSubtargetInfo.cpp.

|

inlinevirtual |

Definition at line 89 of file TargetSubtargetInfo.h.

Referenced by llvm::ScheduleDAGInstrs::addVRegUseDeps().

|

virtual |

True if the subtarget should run MachineScheduler after aggressive coalescing.

This currently replaces the SelectionDAG scheduler with the "source" order scheduler. It does not yet disable the postRA scheduler.

Definition at line 41 of file TargetSubtargetInfo.cpp.

Referenced by useMachineScheduler().

|

virtual |

Definition at line 45 of file TargetSubtargetInfo.cpp.

References ANTIDEP_NONE, and llvm::SmallVectorImpl< T >::clear().

|

inlinevirtual |

Override generic scheduling policy within a region.

This is a convenient way for targets that don't provide any custom scheduling heuristics (no custom MachineSchedStrategy) to make changes to the generic scheduling policy.

Definition at line 74 of file TargetSubtargetInfo.h.

|

inlinevirtual |

Reset the features for the subtarget.

Definition at line 97 of file TargetSubtargetInfo.h.

Referenced by llvm::SelectionDAGISel::runOnMachineFunction().

|

inlinevirtual |

Resolve a SchedClass at runtime, where SchedClass identifies an MCSchedClassDesc with the isVariant property. This may return the ID of another variant SchedClass, but repeated invocation must quickly terminate in a nonvariant SchedClass.

Definition at line 54 of file TargetSubtargetInfo.h.

Referenced by llvm::TargetSchedModel::resolveSchedClass().

|

virtual |

Enable use of alias analysis during code generation (during MI scheduling, DAGCombine, etc.).

Definition at line 54 of file TargetSubtargetInfo.cpp.

Referenced by llvm::ScheduleDAGInstrs::buildSchedGraph().

| bool TargetSubtargetInfo::useMachineScheduler | ( | ) | const |

Temporary API to test migration to MI scheduler.

Definition at line 35 of file TargetSubtargetInfo.cpp.

References BenchMachineSched, and enableMachineScheduler().

Referenced by llvm::createDefaultScheduler(), and llvm::TargetPassConfig::TargetPassConfig().