LLVM API Documentation

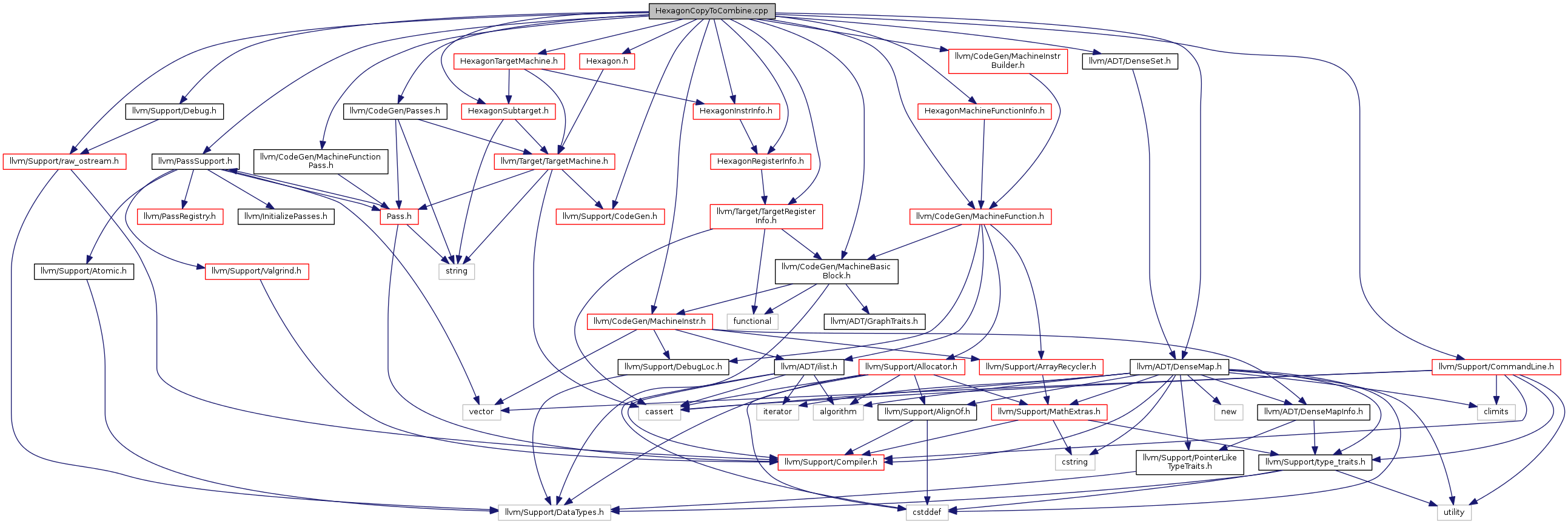

#include "llvm/PassSupport.h"#include "llvm/ADT/DenseSet.h"#include "llvm/ADT/DenseMap.h"#include "llvm/CodeGen/Passes.h"#include "llvm/CodeGen/MachineBasicBlock.h"#include "llvm/CodeGen/MachineFunction.h"#include "llvm/CodeGen/MachineFunctionPass.h"#include "llvm/CodeGen/MachineInstr.h"#include "llvm/CodeGen/MachineInstrBuilder.h"#include "llvm/Target/TargetRegisterInfo.h"#include "llvm/Support/CodeGen.h"#include "llvm/Support/CommandLine.h"#include "llvm/Support/Debug.h"#include "llvm/Support/raw_ostream.h"#include "Hexagon.h"#include "HexagonInstrInfo.h"#include "HexagonRegisterInfo.h"#include "HexagonSubtarget.h"#include "HexagonTargetMachine.h"#include "HexagonMachineFunctionInfo.h"

Go to the source code of this file.

Namespaces | |

| llvm | |

| List of target independent CodeGen pass IDs. | |

Macros | |

| #define | DEBUG_TYPE "hexagon-copy-combine" |

Functions | |

| void | llvm::initializeHexagonCopyToCombinePass (PassRegistry &) |

| INITIALIZE_PASS (HexagonCopyToCombine,"hexagon-copy-combine","Hexagon Copy-To-Combine Pass", false, false) static bool isCombinableInstType(MachineInstr *MI | |

| const HexagonInstrInfo bool ShouldCombineAggressively | switch (MI->getOpcode()) |

| static bool | isGreaterThan8BitTFRI (MachineInstr *I) |

| static bool | isGreaterThan6BitTFRI (MachineInstr *I) |

| static bool | areCombinableOperations (const TargetRegisterInfo *TRI, MachineInstr *HighRegInst, MachineInstr *LowRegInst) |

| static bool | isEvenReg (unsigned Reg) |

| static void | removeKillInfo (MachineInstr *MI, unsigned RegNotKilled) |

| static bool | isUnsafeToMoveAcross (MachineInstr *I, unsigned UseReg, unsigned DestReg, const TargetRegisterInfo *TRI) |

Variables | |

| static cl::opt< bool > | IsCombinesDisabled ("disable-merge-into-combines", cl::Hidden, cl::ZeroOrMore, cl::init(false), cl::desc("Disable merging into combines")) |

| static cl::opt< unsigned > | MaxNumOfInstsBetweenNewValueStoreAndTFR ("max-num-inst-between-tfr-and-nv-store", cl::Hidden, cl::init(4), cl::desc("Maximum distance between a tfr feeding a store we ""consider the store still to be newifiable")) |

| const HexagonInstrInfo * | TII |

| return | false |

| #define DEBUG_TYPE "hexagon-copy-combine" |

Definition at line 14 of file HexagonCopyToCombine.cpp.

|

static |

areCombinableOperations - Returns true if the two instruction can be merge into a combine (ignoring register constraints).

Definition at line 172 of file HexagonCopyToCombine.cpp.

References llvm::MachineInstr::getOpcode(), llvm::HexagonSubtarget::hasV4TOps(), isGreaterThan6BitTFRI(), isGreaterThan8BitTFRI(), and llvm::HexagonRegisterInfo::Subtarget.

| INITIALIZE_PASS | ( | HexagonCopyToCombine | , |

| "hexagon-copy-combine" | , | ||

| "Hexagon Copy-To-Combine Pass" | , | ||

| false | , | ||

| false | |||

| ) |

Definition at line 205 of file HexagonCopyToCombine.cpp.

References llvm::TargetRegisterInfo::isPhysicalRegister().

|

static |

Definition at line 165 of file HexagonCopyToCombine.cpp.

References llvm::MachineOperand::getImm(), llvm::MachineInstr::getOpcode(), and llvm::MachineInstr::getOperand().

Referenced by areCombinableOperations().

|

static |

Definition at line 161 of file HexagonCopyToCombine.cpp.

References llvm::MachineOperand::getImm(), llvm::MachineInstr::getOpcode(), llvm::MachineInstr::getOperand(), and llvm::isInt< 8 >().

Referenced by areCombinableOperations().

|

static |

isUnsafeToMoveAcross - Returns true if it is unsafe to move a copy instruction from UseReg to DestReg over the instruction I.

Definition at line 222 of file HexagonCopyToCombine.cpp.

References llvm::MachineInstr::hasUnmodeledSideEffects(), llvm::MachineInstr::isDebugValue(), llvm::MachineInstr::isInlineAsm(), llvm::MachineInstr::modifiesRegister(), and llvm::MachineInstr::readsRegister().

|

static |

Definition at line 211 of file HexagonCopyToCombine.cpp.

References llvm::MachineInstr::getNumOperands(), llvm::MachineInstr::getOperand(), llvm::MachineOperand::getReg(), I, llvm::MachineOperand::isKill(), llvm::MachineOperand::isReg(), and llvm::MachineOperand::setIsKill().

| const HexagonInstrInfo bool ShouldCombineAggressively switch | ( | MI-> | getOpcode() | ) |

Definition at line 117 of file HexagonCopyToCombine.cpp.

References llvm::isInt< 8 >(), and llvm::HexagonII::MO_NO_FLAG.

| return false |

Definition at line 158 of file HexagonCopyToCombine.cpp.

|

static |

|

static |

| const HexagonInstrInfo* TII |

Definition at line 115 of file HexagonCopyToCombine.cpp.

Referenced by llvm::MachineBasicBlock::addLiveIn(), llvm::X86FrameLowering::adjustForHiPEPrologue(), llvm::X86FrameLowering::adjustForSegmentedStacks(), llvm::MachineBasicBlock::canFallThrough(), llvm::createBURRListDAGScheduler(), llvm::createHybridListDAGScheduler(), llvm::createILPListDAGScheduler(), llvm::createSourceListDAGScheduler(), llvm::Mips16FrameLowering::eliminateCallFramePseudoInstr(), llvm::SparcFrameLowering::eliminateCallFramePseudoInstr(), llvm::MSP430FrameLowering::eliminateCallFramePseudoInstr(), llvm::XCoreFrameLowering::eliminateCallFramePseudoInstr(), llvm::Thumb1FrameLowering::eliminateCallFramePseudoInstr(), llvm::PPCFrameLowering::eliminateCallFramePseudoInstr(), llvm::X86FrameLowering::eliminateCallFramePseudoInstr(), llvm::AArch64FrameLowering::eliminateCallFramePseudoInstr(), llvm::AArch64RegisterInfo::eliminateFrameIndex(), llvm::SparcRegisterInfo::eliminateFrameIndex(), llvm::MSP430RegisterInfo::eliminateFrameIndex(), llvm::XCoreRegisterInfo::eliminateFrameIndex(), llvm::HexagonRegisterInfo::eliminateFrameIndex(), llvm::SystemZRegisterInfo::eliminateFrameIndex(), llvm::PPCRegisterInfo::eliminateFrameIndex(), llvm::ARMBaseRegisterInfo::eliminateFrameIndex(), llvm::AArch64TargetLowering::emitAtomicBinary(), llvm::PPCTargetLowering::EmitAtomicBinary(), llvm::AArch64TargetLowering::emitAtomicBinaryMinMax(), llvm::AArch64TargetLowering::emitAtomicCmpSwap(), llvm::PPCTargetLowering::emitEHSjLjLongJmp(), llvm::PPCTargetLowering::emitEHSjLjSetJmp(), llvm::Mips16FrameLowering::emitEpilogue(), llvm::XCoreFrameLowering::emitEpilogue(), llvm::HexagonFrameLowering::emitEpilogue(), llvm::SparcFrameLowering::emitEpilogue(), llvm::MSP430FrameLowering::emitEpilogue(), llvm::Thumb1FrameLowering::emitEpilogue(), llvm::ARMFrameLowering::emitEpilogue(), llvm::PPCFrameLowering::emitEpilogue(), llvm::X86FrameLowering::emitEpilogue(), llvm::AArch64FrameLowering::emitEpilogue(), llvm::AArch64TargetLowering::EmitF128CSEL(), llvm::AArch64FrameLowering::emitFrameMemOps(), llvm::R600TargetLowering::EmitInstrWithCustomInserter(), llvm::SITargetLowering::EmitInstrWithCustomInserter(), llvm::SparcTargetLowering::EmitInstrWithCustomInserter(), llvm::XCoreTargetLowering::EmitInstrWithCustomInserter(), llvm::MSP430TargetLowering::EmitInstrWithCustomInserter(), llvm::PPCTargetLowering::EmitInstrWithCustomInserter(), llvm::Thumb2RegisterInfo::emitLoadConstPool(), llvm::Thumb1RegisterInfo::emitLoadConstPool(), llvm::ARMBaseRegisterInfo::emitLoadConstPool(), llvm::PPCTargetLowering::EmitPartwordAtomicBinary(), llvm::Mips16FrameLowering::emitPrologue(), llvm::XCoreFrameLowering::emitPrologue(), llvm::HexagonFrameLowering::emitPrologue(), llvm::SparcFrameLowering::emitPrologue(), llvm::MSP430FrameLowering::emitPrologue(), llvm::Thumb1FrameLowering::emitPrologue(), llvm::ARMFrameLowering::emitPrologue(), llvm::PPCFrameLowering::emitPrologue(), llvm::X86FrameLowering::emitPrologue(), llvm::AArch64FrameLowering::emitPrologue(), llvm::MSP430TargetLowering::EmitShiftInstr(), llvm::finalizeBundle(), FindCallSeqStart(), FoldOperand(), llvm::ARMHazardRecognizer::getHazardType(), llvm::MSP430InstrInfo::GetInstSizeInBytes(), llvm::SDNode::getOperationName(), llvm::SIRegisterInfo::getReservedRegs(), llvm::R600RegisterInfo::getReservedRegs(), llvm::ARMTargetLowering::getSchedulingPreference(), INITIALIZE_PASS(), IsChainDependent(), llvm::PPCRegisterInfo::lowerCRRestore(), llvm::PPCRegisterInfo::lowerCRSpilling(), llvm::PPCRegisterInfo::lowerDynamicAlloc(), llvm::R600TargetLowering::LowerOperation(), llvm::PPCRegisterInfo::lowerVRSAVERestore(), llvm::PPCRegisterInfo::lowerVRSAVESpilling(), llvm::PPCRegisterInfo::materializeFrameBaseRegister(), llvm::ARMBaseRegisterInfo::materializeFrameBaseRegister(), llvm::AArch64FrameLowering::processFunctionBeforeCalleeSavedScan(), llvm::MachineRegisterInfo::recomputeRegClass(), replaceFI(), llvm::ARMBaseRegisterInfo::resolveFrameIndex(), llvm::XCoreFrameLowering::restoreCalleeSavedRegisters(), llvm::Thumb1FrameLowering::restoreCalleeSavedRegisters(), llvm::HexagonFrameLowering::restoreCalleeSavedRegisters(), llvm::SystemZFrameLowering::restoreCalleeSavedRegisters(), llvm::MSP430FrameLowering::restoreCalleeSavedRegisters(), llvm::X86FrameLowering::restoreCalleeSavedRegisters(), llvm::PPCFrameLowering::restoreCalleeSavedRegisters(), restoreCRs(), llvm::SelectionDAGISel::runOnMachineFunction(), llvm::VirtRegMap::runOnMachineFunction(), llvm::MachineTraceMetrics::runOnMachineFunction(), llvm::Mips16RegisterInfo::saveScavengerRegister(), llvm::FunctionLoweringInfo::set(), llvm::XCoreFrameLowering::spillCalleeSavedRegisters(), llvm::HexagonFrameLowering::spillCalleeSavedRegisters(), llvm::Thumb1FrameLowering::spillCalleeSavedRegisters(), llvm::SystemZFrameLowering::spillCalleeSavedRegisters(), llvm::MSP430FrameLowering::spillCalleeSavedRegisters(), llvm::X86FrameLowering::spillCalleeSavedRegisters(), llvm::PPCFrameLowering::spillCalleeSavedRegisters(), llvm::MachineBasicBlock::SplitCriticalEdge(), and llvm::MachineBasicBlock::updateTerminator().