LLVM API Documentation

#include <MCInstrInfo.h>

Public Member Functions | |

| void | InitMCInstrInfo (const MCInstrDesc *D, const unsigned *NI, const char *ND, unsigned NO) |

| unsigned | getNumOpcodes () const |

| const MCInstrDesc & | get (unsigned Opcode) const |

| const char * | getName (unsigned Opcode) const |

| getName - Returns the name for the instructions with the given opcode. More... | |

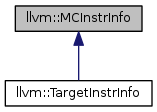

MCInstrInfo - Interface to description of machine instruction set

Definition at line 26 of file MCInstrInfo.h.

|

inline |

get - Return the machine instruction descriptor that corresponds to the specified instruction opcode.

Definition at line 48 of file MCInstrInfo.h.

Referenced by llvm::MachineBasicBlock::addLiveIn(), canClobberPhysRegDefs(), canClobberReachingPhysRegUse(), CheckForPhysRegDependency(), combineRestoreADD(), combineRestoreOR(), combineRestoreSETHIi(), llvm::ScheduleDAGSDNodes::computeOperandLatency(), llvm::SparcRegisterInfo::eliminateFrameIndex(), llvm::MSP430RegisterInfo::eliminateFrameIndex(), llvm::XCoreRegisterInfo::eliminateFrameIndex(), llvm::PPCRegisterInfo::eliminateFrameIndex(), emitAlignedDPRCS2Restores(), emitAlignedDPRCS2Spills(), llvm::AArch64TargetLowering::emitAtomicBinary(), llvm::PPCTargetLowering::EmitAtomicBinary(), llvm::AArch64TargetLowering::emitAtomicBinaryMinMax(), llvm::AArch64TargetLowering::emitAtomicCmpSwap(), llvm::InstrEmitter::EmitDbgValue(), llvm::PPCTargetLowering::emitEHSjLjLongJmp(), llvm::PPCTargetLowering::emitEHSjLjSetJmp(), llvm::HexagonFrameLowering::emitEpilogue(), llvm::AArch64FrameLowering::emitEpilogue(), llvm::AArch64TargetLowering::EmitF128CSEL(), llvm::AArch64FrameLowering::emitFrameMemOps(), emitIncrement(), llvm::SparcTargetLowering::EmitInstrWithCustomInserter(), llvm::XCoreTargetLowering::EmitInstrWithCustomInserter(), llvm::MSP430TargetLowering::EmitInstrWithCustomInserter(), llvm::ARMTargetLowering::EmitInstrWithCustomInserter(), llvm::PPCTargetLowering::EmitInstrWithCustomInserter(), llvm::X86TargetLowering::EmitInstrWithCustomInserter(), llvm::MachineRegisterInfo::EmitLiveInCopies(), llvm::Thumb2RegisterInfo::emitLoadConstPool(), llvm::Thumb1RegisterInfo::emitLoadConstPool(), llvm::ARMBaseRegisterInfo::emitLoadConstPool(), EmitMonitor(), llvm::PPCTargetLowering::EmitPartwordAtomicBinary(), EmitPCMPSTRI(), EmitPCMPSTRM(), emitPostLd(), emitPostSt(), llvm::HexagonFrameLowering::emitPrologue(), llvm::AArch64FrameLowering::emitPrologue(), llvm::MSP430TargetLowering::EmitShiftInstr(), emitSPUpdate(), emitThumbConstant(), emitThumbRegPlusImmInReg(), EmitXBegin(), llvm::MCInstrAnalysis::evaluateBranch(), expandPseudoDIV(), llvm::FastISel::FastEmitInst_(), llvm::FastISel::FastEmitInst_extractsubreg(), llvm::FastISel::FastEmitInst_i(), llvm::FastISel::FastEmitInst_ii(), llvm::FastISel::FastEmitInst_r(), llvm::FastISel::FastEmitInst_rf(), llvm::FastISel::FastEmitInst_ri(), llvm::FastISel::FastEmitInst_rii(), llvm::FastISel::FastEmitInst_rr(), llvm::FastISel::FastEmitInst_rri(), llvm::FastISel::FastEmitInst_rrii(), llvm::FastISel::FastEmitInst_rrr(), llvm::finalizeBundle(), foldPatchpoint(), FuseInst(), FuseTwoAddrInst(), GetCostForDef(), getItineraryLatency(), getLatency(), getPhysicalRegisterVT(), llvm::ARMTargetLowering::getSchedulingPreference(), HandleVRSaveUpdate(), llvm::ResourcePriorityQueue::initNumRegDefsLeft(), InsertLDR_STR(), InsertNewDef(), llvm::MCInstrAnalysis::isBranch(), llvm::MCInstrAnalysis::isCall(), llvm::MCInstrAnalysis::isConditionalBranch(), llvm::MCInstrAnalysis::isIndirectBranch(), llvm::ResourcePriorityQueue::isResourceAvailable(), llvm::MCInstrAnalysis::isReturn(), llvm::MCInstrAnalysis::isTerminator(), llvm::MCInstrAnalysis::isUnconditionalBranch(), loadFromStack(), llvm::PPCRegisterInfo::lowerCRRestore(), llvm::PPCRegisterInfo::lowerCRSpilling(), llvm::PPCRegisterInfo::lowerDynamicAlloc(), llvm::PPCRegisterInfo::lowerVRSAVERestore(), llvm::PPCRegisterInfo::lowerVRSAVESpilling(), MakeM0Inst(), llvm::PPCRegisterInfo::materializeFrameBaseRegister(), llvm::ARMBaseRegisterInfo::materializeFrameBaseRegister(), llvm::X86ATTInstPrinter::printInst(), llvm::X86IntelInstPrinter::printInst(), replaceFI(), llvm::ResourcePriorityQueue::reserveResources(), llvm::SystemZFrameLowering::restoreCalleeSavedRegisters(), llvm::MSP430FrameLowering::restoreCalleeSavedRegisters(), llvm::X86FrameLowering::restoreCalleeSavedRegisters(), llvm::SelectionDAGISel::runOnMachineFunction(), llvm::Thumb1RegisterInfo::saveScavengerRegister(), llvm::SelectionDAGISel::SelectCodeCommon(), llvm::FunctionLoweringInfo::set(), llvm::XCoreFrameLowering::spillCalleeSavedRegisters(), llvm::Thumb1FrameLowering::spillCalleeSavedRegisters(), llvm::SystemZFrameLowering::spillCalleeSavedRegisters(), llvm::MSP430FrameLowering::spillCalleeSavedRegisters(), llvm::X86FrameLowering::spillCalleeSavedRegisters(), storeToStack(), and llvm::ResourcePriorityQueue::SUSchedulingCost().

|

inline |

getName - Returns the name for the instructions with the given opcode.

Definition at line 54 of file MCInstrInfo.h.

Referenced by llvm::HexagonInstPrinter::getOpcodeName(), llvm::MCInstPrinter::getOpcodeName(), llvm::MachineInstr::print(), and x86DisassemblerGetInstrName().

|

inline |

Definition at line 43 of file MCInstrInfo.h.

|

inline |

InitMCInstrInfo - Initialize MCInstrInfo, called by TableGen auto-generated routines. DO NOT USE.

Definition at line 35 of file MCInstrInfo.h.