LLVM API Documentation

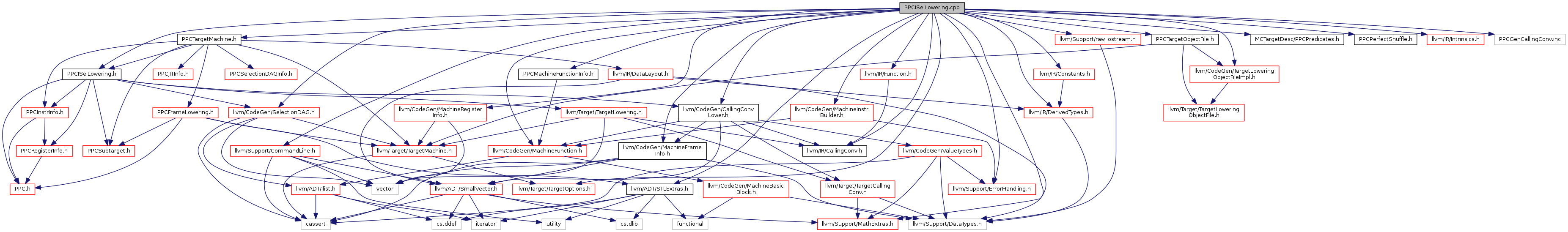

#include "PPCISelLowering.h"#include "MCTargetDesc/PPCPredicates.h"#include "PPCMachineFunctionInfo.h"#include "PPCPerfectShuffle.h"#include "PPCTargetMachine.h"#include "PPCTargetObjectFile.h"#include "llvm/ADT/STLExtras.h"#include "llvm/CodeGen/CallingConvLower.h"#include "llvm/CodeGen/MachineFrameInfo.h"#include "llvm/CodeGen/MachineFunction.h"#include "llvm/CodeGen/MachineInstrBuilder.h"#include "llvm/CodeGen/MachineRegisterInfo.h"#include "llvm/CodeGen/SelectionDAG.h"#include "llvm/CodeGen/TargetLoweringObjectFileImpl.h"#include "llvm/IR/CallingConv.h"#include "llvm/IR/Constants.h"#include "llvm/IR/DerivedTypes.h"#include "llvm/IR/Function.h"#include "llvm/IR/Intrinsics.h"#include "llvm/Support/CommandLine.h"#include "llvm/Support/ErrorHandling.h"#include "llvm/Support/MathExtras.h"#include "llvm/Support/raw_ostream.h"#include "llvm/Target/TargetOptions.h"#include "PPCGenCallingConv.inc"

Go to the source code of this file.

Functions | |

| static TargetLoweringObjectFile * | CreateTLOF (const PPCTargetMachine &TM) |

| static void | getMaxByValAlign (Type *Ty, unsigned &MaxAlign, unsigned MaxMaxAlign) |

| static bool | isFloatingPointZero (SDValue Op) |

| isFloatingPointZero - Return true if this is 0.0 or -0.0. More... | |

| static bool | isConstantOrUndef (int Op, int Val) |

| static bool | isVMerge (ShuffleVectorSDNode *N, unsigned UnitSize, unsigned LHSStart, unsigned RHSStart) |

| static bool | isIntS16Immediate (SDNode *N, short &Imm) |

| static bool | isIntS16Immediate (SDValue Op, short &Imm) |

| static void | fixupFuncForFI (SelectionDAG &DAG, int FrameIdx, EVT VT) |

| static bool | GetLabelAccessInfo (const TargetMachine &TM, unsigned &HiOpFlags, unsigned &LoOpFlags, const GlobalValue *GV=0) |

| static SDValue | LowerLabelRef (SDValue HiPart, SDValue LoPart, bool isPIC, SelectionDAG &DAG) |

| static const uint16_t * | GetFPR () |

| static unsigned | CalculateStackSlotSize (EVT ArgVT, ISD::ArgFlagsTy Flags, unsigned PtrByteSize) |

| static unsigned | CalculateParameterAndLinkageAreaSize (SelectionDAG &DAG, bool isPPC64, bool isVarArg, unsigned CC, const SmallVectorImpl< ISD::OutputArg > &Outs, const SmallVectorImpl< SDValue > &OutVals, unsigned &nAltivecParamsAtEnd) |

| static int | CalculateTailCallSPDiff (SelectionDAG &DAG, bool isTailCall, unsigned ParamSize) |

| static SDNode * | isBLACompatibleAddress (SDValue Op, SelectionDAG &DAG) |

| static void | StoreTailCallArgumentsToStackSlot (SelectionDAG &DAG, SDValue Chain, const SmallVectorImpl< TailCallArgumentInfo > &TailCallArgs, SmallVectorImpl< SDValue > &MemOpChains, SDLoc dl) |

| StoreTailCallArgumentsToStackSlot - Stores arguments to their stack slot. More... | |

| static SDValue | EmitTailCallStoreFPAndRetAddr (SelectionDAG &DAG, MachineFunction &MF, SDValue Chain, SDValue OldRetAddr, SDValue OldFP, int SPDiff, bool isPPC64, bool isDarwinABI, SDLoc dl) |

| static void | CalculateTailCallArgDest (SelectionDAG &DAG, MachineFunction &MF, bool isPPC64, SDValue Arg, int SPDiff, unsigned ArgOffset, SmallVectorImpl< TailCallArgumentInfo > &TailCallArguments) |

| static SDValue | CreateCopyOfByValArgument (SDValue Src, SDValue Dst, SDValue Chain, ISD::ArgFlagsTy Flags, SelectionDAG &DAG, SDLoc dl) |

| static void | LowerMemOpCallTo (SelectionDAG &DAG, MachineFunction &MF, SDValue Chain, SDValue Arg, SDValue PtrOff, int SPDiff, unsigned ArgOffset, bool isPPC64, bool isTailCall, bool isVector, SmallVectorImpl< SDValue > &MemOpChains, SmallVectorImpl< TailCallArgumentInfo > &TailCallArguments, SDLoc dl) |

| static void | PrepareTailCall (SelectionDAG &DAG, SDValue &InFlag, SDValue &Chain, SDLoc dl, bool isPPC64, int SPDiff, unsigned NumBytes, SDValue LROp, SDValue FPOp, bool isDarwinABI, SmallVectorImpl< TailCallArgumentInfo > &TailCallArguments) |

| static unsigned | PrepareCall (SelectionDAG &DAG, SDValue &Callee, SDValue &InFlag, SDValue &Chain, SDLoc dl, int SPDiff, bool isTailCall, SmallVectorImpl< std::pair< unsigned, SDValue > > &RegsToPass, SmallVectorImpl< SDValue > &Ops, std::vector< EVT > &NodeTys, const PPCSubtarget &PPCSubTarget) |

| static bool | isLocalCall (const SDValue &Callee) |

| static SDValue | BuildSplatI (int Val, unsigned SplatSize, EVT VT, SelectionDAG &DAG, SDLoc dl) |

| static SDValue | BuildIntrinsicOp (unsigned IID, SDValue Op, SelectionDAG &DAG, SDLoc dl, EVT DestVT=MVT::Other) |

| static SDValue | BuildIntrinsicOp (unsigned IID, SDValue LHS, SDValue RHS, SelectionDAG &DAG, SDLoc dl, EVT DestVT=MVT::Other) |

| static SDValue | BuildIntrinsicOp (unsigned IID, SDValue Op0, SDValue Op1, SDValue Op2, SelectionDAG &DAG, SDLoc dl, EVT DestVT=MVT::Other) |

| static SDValue | BuildVSLDOI (SDValue LHS, SDValue RHS, unsigned Amt, EVT VT, SelectionDAG &DAG, SDLoc dl) |

| static SDValue | GeneratePerfectShuffle (unsigned PFEntry, SDValue LHS, SDValue RHS, SelectionDAG &DAG, SDLoc dl) |

| static bool | getAltivecCompareInfo (SDValue Intrin, int &CompareOpc, bool &isDot) |

| static bool | isConsecutiveLS (LSBaseSDNode *LS, LSBaseSDNode *Base, unsigned Bytes, int Dist, SelectionDAG &DAG) |

| static bool | findConsecutiveLoad (LoadSDNode *LD, SelectionDAG &DAG) |

Variables | |

| static cl::opt< bool > | DisablePPCPreinc ("disable-ppc-preinc", cl::desc("disable preincrement load/store generation on PPC"), cl::Hidden) |

| static cl::opt< bool > | DisableILPPref ("disable-ppc-ilp-pref", cl::desc("disable setting the node scheduling preference to ILP on PPC"), cl::Hidden) |

| static cl::opt< bool > | DisablePPCUnaligned ("disable-ppc-unaligned", cl::desc("disable unaligned load/store generation on PPC"), cl::Hidden) |

|

static |

BuildIntrinsicOp - Return a unary operator intrinsic node with the specified intrinsic ID.

Definition at line 5174 of file PPCISelLowering.cpp.

References llvm::SelectionDAG::getConstant(), llvm::SelectionDAG::getNode(), llvm::SDValue::getValueType(), llvm::ISD::INTRINSIC_WO_CHAIN, and llvm::MVT::Other.

Referenced by llvm::PPCTargetLowering::PerformDAGCombine().

|

static |

BuildIntrinsicOp - Return a binary operator intrinsic node with the specified intrinsic ID.

Definition at line 5184 of file PPCISelLowering.cpp.

References llvm::SelectionDAG::getConstant(), llvm::SelectionDAG::getNode(), llvm::SDValue::getValueType(), llvm::ISD::INTRINSIC_WO_CHAIN, and llvm::MVT::Other.

|

static |

BuildIntrinsicOp - Return a ternary operator intrinsic node with the specified intrinsic ID.

Definition at line 5194 of file PPCISelLowering.cpp.

References llvm::SelectionDAG::getConstant(), llvm::SelectionDAG::getNode(), llvm::SDValue::getValueType(), llvm::ISD::INTRINSIC_WO_CHAIN, and llvm::MVT::Other.

|

static |

BuildSplatI - Build a canonical splati of Val with an element size of SplatSize. Cast the result to VT.

Definition at line 5147 of file PPCISelLowering.cpp.

References llvm::SmallVectorImpl< T >::assign(), llvm::ISD::BITCAST, llvm::ISD::BUILD_VECTOR, llvm::SelectionDAG::getConstant(), llvm::SelectionDAG::getNode(), llvm::EVT::getVectorNumElements(), llvm::MVT::Other, llvm::SmallVectorTemplateCommon< T >::size(), llvm::MVT::v16i8, llvm::MVT::v4i32, and llvm::MVT::v8i16.

|

static |

BuildVSLDOI - Return a VECTOR_SHUFFLE that is a vsldoi of the specified amount. The result has the specified value type.

Definition at line 5205 of file PPCISelLowering.cpp.

References llvm::ISD::BITCAST, llvm::SelectionDAG::getNode(), llvm::SelectionDAG::getVectorShuffle(), and llvm::MVT::v16i8.

Referenced by GeneratePerfectShuffle().

|

static |

CalculateParameterAndLinkageAreaSize - Get the size of the parameter plus linkage area for the Darwin ABI, or the 64-bit SVR4 ABI.

Definition at line 2864 of file PPCISelLowering.cpp.

References CalculateStackSlotSize(), llvm::CallingConv::Fast, llvm::PPCFrameLowering::getLinkageSize(), llvm::SelectionDAG::getMachineFunction(), llvm::PPCFrameLowering::getMinCallFrameSize(), llvm::MachineFunction::getTarget(), llvm::SelectionDAG::getTarget(), llvm::TargetOptions::GuaranteedTailCallOpt, llvm::TargetMachine::Options, llvm::SmallVectorTemplateCommon< T, typename >::size(), llvm::MVT::v16i8, llvm::MVT::v4f32, llvm::MVT::v4i32, and llvm::MVT::v8i16.

|

static |

CalculateStackSlotSize - Calculates the size reserved for this argument on the stack.

Definition at line 1923 of file PPCISelLowering.cpp.

References llvm::ISD::ArgFlagsTy::getByValSize(), llvm::EVT::getSizeInBits(), and llvm::ISD::ArgFlagsTy::isByVal().

Referenced by CalculateParameterAndLinkageAreaSize().

|

static |

CalculateTailCallArgDest - Remember Argument for later processing. Calculate the position of the argument.

Definition at line 3073 of file PPCISelLowering.cpp.

References llvm::MachineFrameInfo::CreateFixedObject(), llvm::SelectionDAG::getFrameIndex(), llvm::MachineFunction::getFrameInfo(), llvm::EVT::getSizeInBits(), llvm::SDValue::getValueType(), llvm::MVT::i32, llvm::MVT::i64, llvm::X86II::OpSize, and llvm::SmallVectorTemplateBase< T, isPodLike< T >::value >::push_back().

Referenced by LowerMemOpCallTo().

|

static |

CalculateTailCallSPDiff - Get the amount the stack pointer has to be adjusted to accommodate the arguments for the tailcall.

Definition at line 2931 of file PPCISelLowering.cpp.

References llvm::MachineFunction::getInfo(), llvm::SelectionDAG::getMachineFunction(), llvm::PPCFunctionInfo::getMinReservedArea(), and llvm::PPCFunctionInfo::setTailCallSPDelta().

|

static |

CreateCopyOfByValArgument - Make a copy of an aggregate at address specified by "Src" to address "Dst" of size "Size". Alignment information is specified by the specific parameter attribute. The copy will be passed as a byval function parameter. Sometimes what we are copying is the end of a larger object, the part that does not fit in registers.

Definition at line 3125 of file PPCISelLowering.cpp.

References llvm::ISD::ArgFlagsTy::getByValAlign(), llvm::ISD::ArgFlagsTy::getByValSize(), llvm::SelectionDAG::getConstant(), llvm::SelectionDAG::getMemcpy(), and llvm::MVT::i32.

|

static |

Definition at line 49 of file PPCISelLowering.cpp.

References llvm::PPCTargetMachine::getSubtargetImpl(), llvm::PPCSubtarget::isDarwin(), and llvm::PPCSubtarget::isSVR4ABI().

|

static |

EmitTailCallStoreFPAndRetAddr - Move the frame pointer and return address to the appropriate stack slot for the tail call optimized function call.

Definition at line 3032 of file PPCISelLowering.cpp.

References llvm::MachineFrameInfo::CreateFixedObject(), llvm::MachinePointerInfo::getFixedStack(), llvm::SelectionDAG::getFrameIndex(), llvm::MachineFunction::getFrameInfo(), llvm::PPCFrameLowering::getFramePointerSaveOffset(), llvm::PPCFrameLowering::getReturnSaveOffset(), llvm::SelectionDAG::getStore(), llvm::MVT::i32, and llvm::MVT::i64.

Referenced by PrepareTailCall().

|

static |

Definition at line 6919 of file PPCISelLowering.cpp.

References llvm::SmallVectorImpl< T >::clear(), llvm::MemSDNode::getChain(), llvm::MemSDNode::getMemoryVT(), llvm::SDValue::getNode(), llvm::SDNode::getOpcode(), llvm::EVT::getStoreSize(), I, llvm::ARM_PROC::IE, llvm::SmallSet< T, N, C >::insert(), llvm::SmallVectorImpl< T >::insert(), isConsecutiveLS(), llvm::SDNode::op_begin(), llvm::SDNode::op_end(), llvm::ISD::TokenFactor, llvm::SDNode::use_begin(), and llvm::SDNode::use_end().

Referenced by llvm::PPCTargetLowering::PerformDAGCombine().

|

static |

Definition at line 1068 of file PPCISelLowering.cpp.

References Align(), llvm::MachineFunction::getFrameInfo(), llvm::MachineFunction::getInfo(), llvm::SelectionDAG::getMachineFunction(), llvm::MachineFrameInfo::getObjectAlignment(), llvm::MVT::i64, and llvm::PPCFunctionInfo::setHasNonRISpills().

Referenced by llvm::PPCTargetLowering::SelectAddressRegImm().

|

static |

GeneratePerfectShuffle - Given an entry in the perfect-shuffle table, emit the specified operations to build the shuffle.

Definition at line 5379 of file PPCISelLowering.cpp.

References llvm::ISD::BITCAST, BuildVSLDOI(), llvm::SelectionDAG::getNode(), llvm::SDValue::getValueType(), llvm::SelectionDAG::getVectorShuffle(), llvm_unreachable, PerfectShuffleTable, and llvm::MVT::v16i8.

getAltivecCompareInfo - Given an intrinsic, return false if it is not an altivec comparison. If it is, return true and fill in Opc/isDot with information about the intrinsic.

Definition at line 5580 of file PPCISelLowering.cpp.

References llvm::SDValue::getOperand(), llvm::Intrinsic::ppc_altivec_vcmpbfp, llvm::Intrinsic::ppc_altivec_vcmpbfp_p, llvm::Intrinsic::ppc_altivec_vcmpeqfp, llvm::Intrinsic::ppc_altivec_vcmpeqfp_p, llvm::Intrinsic::ppc_altivec_vcmpequb, llvm::Intrinsic::ppc_altivec_vcmpequb_p, llvm::Intrinsic::ppc_altivec_vcmpequh, llvm::Intrinsic::ppc_altivec_vcmpequh_p, llvm::Intrinsic::ppc_altivec_vcmpequw, llvm::Intrinsic::ppc_altivec_vcmpequw_p, llvm::Intrinsic::ppc_altivec_vcmpgefp, llvm::Intrinsic::ppc_altivec_vcmpgefp_p, llvm::Intrinsic::ppc_altivec_vcmpgtfp, llvm::Intrinsic::ppc_altivec_vcmpgtfp_p, llvm::Intrinsic::ppc_altivec_vcmpgtsb, llvm::Intrinsic::ppc_altivec_vcmpgtsb_p, llvm::Intrinsic::ppc_altivec_vcmpgtsh, llvm::Intrinsic::ppc_altivec_vcmpgtsh_p, llvm::Intrinsic::ppc_altivec_vcmpgtsw, llvm::Intrinsic::ppc_altivec_vcmpgtsw_p, llvm::Intrinsic::ppc_altivec_vcmpgtub, llvm::Intrinsic::ppc_altivec_vcmpgtub_p, llvm::Intrinsic::ppc_altivec_vcmpgtuh, llvm::Intrinsic::ppc_altivec_vcmpgtuh_p, llvm::Intrinsic::ppc_altivec_vcmpgtuw, and llvm::Intrinsic::ppc_altivec_vcmpgtuw_p.

Referenced by llvm::PPCTargetLowering::PerformDAGCombine().

|

static |

GetFPR - Get the set of FP registers that should be allocated for arguments, on Darwin.

Definition at line 1912 of file PPCISelLowering.cpp.

|

static |

GetLabelAccessInfo - Return true if we should reference labels using a PICBase, set the HiOpFlags and LoOpFlags to the target MO flags.

Definition at line 1305 of file PPCISelLowering.cpp.

References llvm::TargetMachine::getRelocationModel(), llvm::TargetMachine::getSubtarget(), llvm::PPCSubtarget::hasLazyResolverStub(), llvm::PPCII::MO_HA, llvm::PPCII::MO_LO, llvm::PPCII::MO_NLP_FLAG, llvm::PPCII::MO_NLP_HIDDEN_FLAG, llvm::PPCII::MO_PIC_FLAG, and llvm::Reloc::PIC_.

getMaxByValAlign - Helper for getByValTypeAlignment to determine the desired ByVal argument alignment.

Definition at line 583 of file PPCISelLowering.cpp.

Referenced by llvm::PPCTargetLowering::getByValTypeAlignment().

|

static |

isCallCompatibleAddress - Return the immediate to use if the specified 32-bit value is representable in the immediate field of a BxA instruction.

Definition at line 2987 of file PPCISelLowering.cpp.

References llvm::dyn_cast(), llvm::SelectionDAG::getConstant(), llvm::TargetLoweringBase::getPointerTy(), llvm::SelectionDAG::getTargetLoweringInfo(), and llvm::ConstantSDNode::getZExtValue().

Referenced by PrepareCall().

|

static |

Definition at line 6876 of file PPCISelLowering.cpp.

References llvm::AArch64ISD::BFI, llvm::ISD::FrameIndex, llvm::X86II::FS, llvm::MemSDNode::getBasePtr(), llvm::MachineFunction::getFrameInfo(), llvm::SelectionDAG::getMachineFunction(), llvm::MemSDNode::getMemoryVT(), llvm::SDValue::getNode(), llvm::MachineFrameInfo::getObjectOffset(), llvm::MachineFrameInfo::getObjectSize(), llvm::SDValue::getOpcode(), llvm::SDValue::getOperand(), llvm::EVT::getSizeInBits(), llvm::SelectionDAG::getTargetLoweringInfo(), llvm::SelectionDAG::isBaseWithConstantOffset(), and llvm::TargetLowering::isGAPlusOffset().

Referenced by findConsecutiveLoad().

|

static |

isConstantOrUndef - Op is either an undef node or a ConstantSDNode. Return true if Op is undef or if it matches the specified value.

Definition at line 714 of file PPCISelLowering.cpp.

Referenced by isVMerge(), llvm::PPC::isVPKUHUMShuffleMask(), llvm::PPC::isVPKUWUMShuffleMask(), and llvm::PPC::isVSLDOIShuffleMask().

isFloatingPointZero - Return true if this is 0.0 or -0.0.

Definition at line 700 of file PPCISelLowering.cpp.

References llvm::SDValue::getNode(), llvm::SDValue::getOperand(), llvm::ISD::isEXTLoad(), and llvm::ISD::isNON_EXTLoad().

isIntS16Immediate - This method tests to see if the node is either a 32-bit or 64-bit immediate, and if the value can be accurately represented as a sign extension from a 16-bit value. If so, this returns true and the immediate.

Definition at line 1001 of file PPCISelLowering.cpp.

References llvm::ISD::Constant, llvm::SDNode::getOpcode(), llvm::SDNode::getValueType(), llvm::MVT::i32, and N.

Referenced by isIntS16Immediate(), llvm::PPCTargetLowering::SelectAddressRegImm(), and llvm::PPCTargetLowering::SelectAddressRegReg().

Definition at line 1011 of file PPCISelLowering.cpp.

References llvm::SDValue::getNode(), and isIntS16Immediate().

Definition at line 3365 of file PPCISelLowering.cpp.

References G.

|

static |

isVMerge - Common function, used to match vmrg* shuffles.

Definition at line 755 of file PPCISelLowering.cpp.

References llvm::ShuffleVectorSDNode::getMaskElt(), llvm::SDNode::getValueType(), isConstantOrUndef(), and llvm::MVT::v16i8.

Referenced by llvm::PPC::isVMRGHShuffleMask(), and llvm::PPC::isVMRGLShuffleMask().

|

static |

Definition at line 1334 of file PPCISelLowering.cpp.

References llvm::ISD::ADD, llvm::SelectionDAG::getConstant(), llvm::SelectionDAG::getNode(), llvm::SDValue::getValueType(), llvm::PPCISD::GlobalBaseReg, llvm::HexagonISD::Hi, llvm::PPCISD::Hi, llvm::HexagonISD::Lo, and llvm::PPCISD::Lo.

|

static |

LowerMemOpCallTo - Store the argument to the stack or remember it in case of tail calls.

Definition at line 3137 of file PPCISelLowering.cpp.

References llvm::ISD::ADD, CalculateTailCallArgDest(), llvm::SelectionDAG::getConstant(), llvm::SelectionDAG::getNode(), llvm::TargetLoweringBase::getPointerTy(), llvm::SelectionDAG::getRegister(), llvm::SelectionDAG::getStore(), llvm::SelectionDAG::getTargetLoweringInfo(), llvm::MVT::i64, and llvm::SmallVectorTemplateBase< T, isPodLike< T >::value >::push_back().

|

static |

Definition at line 3190 of file PPCISelLowering.cpp.

References llvm::ISD::ADD, llvm::PPCISD::BCTRL, llvm::PPCISD::CALL, G, llvm::SelectionDAG::getConstant(), llvm::SelectionDAG::getCopyToReg(), llvm::SelectionDAG::getIntPtrConstant(), llvm::SDValue::getNode(), llvm::SelectionDAG::getNode(), llvm::TargetLoweringBase::getPointerTy(), llvm::SelectionDAG::getRegister(), llvm::TargetMachine::getRelocationModel(), llvm::TargetMachine::getSubtarget(), llvm::SelectionDAG::getTarget(), llvm::SelectionDAG::getTargetExternalSymbol(), llvm::SelectionDAG::getTargetGlobalAddress(), llvm::SelectionDAG::getTargetLoweringInfo(), llvm::PPCSubtarget::getTargetTriple(), llvm::SDValue::getValue(), llvm::SDValue::getValueType(), llvm::SelectionDAG::getVTList(), llvm::MVT::Glue, llvm::MVT::i64, isBLACompatibleAddress(), llvm::Triple::isMacOSX(), llvm::Triple::isMacOSXVersionLT(), llvm::PPCSubtarget::isPPC64(), llvm::PPCSubtarget::isSVR4ABI(), llvm::PPCISD::LOAD, llvm::PPCISD::LOAD_TOC, llvm::PPCII::MO_DARWIN_STUB, llvm::PPCISD::MTCTR, llvm::MVT::Other, llvm::SmallVectorTemplateBase< T, isPodLike< T >::value >::push_back(), llvm::SDValue::setNode(), and llvm::Reloc::Static.

|

static |

Definition at line 3162 of file PPCISelLowering.cpp.

References EmitTailCallStoreFPAndRetAddr(), llvm::SmallVectorBase::empty(), llvm::SelectionDAG::getCALLSEQ_END(), llvm::SelectionDAG::getIntPtrConstant(), llvm::SelectionDAG::getMachineFunction(), llvm::SelectionDAG::getNode(), llvm::SDValue::getValue(), llvm::MVT::Other, llvm::SmallVectorTemplateCommon< T >::size(), StoreTailCallArgumentsToStackSlot(), and llvm::ISD::TokenFactor.

|

static |

StoreTailCallArgumentsToStackSlot - Stores arguments to their stack slot.

Definition at line 3014 of file PPCISelLowering.cpp.

References llvm::MachinePointerInfo::getFixedStack(), llvm::SelectionDAG::getStore(), llvm::SmallVectorTemplateBase< T, isPodLike< T >::value >::push_back(), and llvm::SmallVectorTemplateCommon< T >::size().

Referenced by PrepareTailCall().

|

static |

Referenced by llvm::PPCTargetLowering::getSchedulingPreference().

|

static |

Referenced by llvm::PPCTargetLowering::getPreIndexedAddressParts().

|

static |

Referenced by llvm::PPCTargetLowering::allowsUnalignedMemoryAccesses().