LLVM API Documentation

#include <AMDGPUInstrInfo.h>

Protected Member Functions | |

| MachineInstr * | foldMemoryOperandImpl (MachineFunction &MF, MachineInstr *MI, const SmallVectorImpl< unsigned > &Ops, int FrameIndex) const |

| MachineInstr * | foldMemoryOperandImpl (MachineFunction &MF, MachineInstr *MI, const SmallVectorImpl< unsigned > &Ops, MachineInstr *LoadMI) const |

| virtual int | getIndirectIndexBegin (const MachineFunction &MF) const |

| virtual int | getIndirectIndexEnd (const MachineFunction &MF) const |

Protected Attributes | |

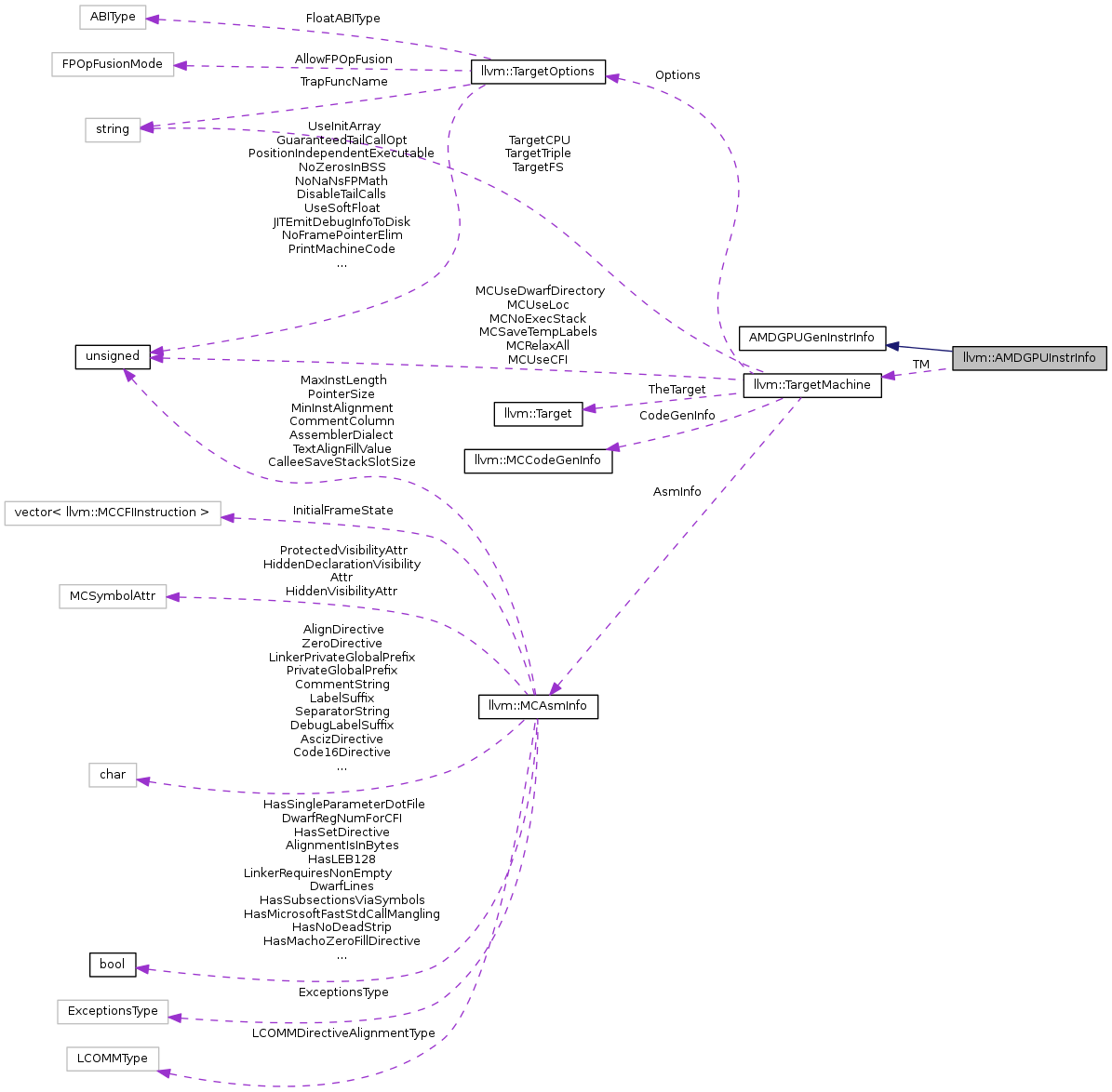

| TargetMachine & | TM |

Definition at line 41 of file AMDGPUInstrInfo.h.

|

explicit |

Definition at line 34 of file AMDGPUInstrInfo.cpp.

|

pure virtual |

Build instruction(s) for an indirect register read.

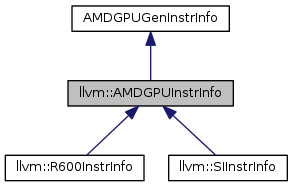

Implemented in llvm::R600InstrInfo, and llvm::SIInstrInfo.

Referenced by expandPostRAPseudo().

|

pure virtual |

Build instruction(s) for an indirect register write.

Implemented in llvm::R600InstrInfo, and llvm::SIInstrInfo.

Referenced by expandPostRAPseudo().

|

pure virtual |

Build a MOV instruction.

Implemented in llvm::R600InstrInfo, and llvm::SIInstrInfo.

Referenced by expandPostRAPseudo().

|

pure virtual |

Calculate the "Indirect Address" for the given RegIndex and Channel.

We model indirect addressing using a virtual address space that can be accesed with loads and stores. The "Indirect Address" is the memory address in this virtual address space that maps to the given RegIndex and Channel.

Implemented in llvm::R600InstrInfo, and llvm::SIInstrInfo.

Referenced by expandPostRAPseudo().

| bool AMDGPUInstrInfo::canFoldMemoryOperand | ( | const MachineInstr * | MI, |

| const SmallVectorImpl< unsigned > & | Ops | ||

| ) | const |

Definition at line 191 of file AMDGPUInstrInfo.cpp.

|

virtual |

Convert the AMDIL MachineInstr to a supported ISA MachineInstr.

Definition at line 331 of file AMDGPUInstrInfo.cpp.

References llvm::AMDGPURegisterInfo::getISARegClass(), llvm::MachineInstr::getNumOperands(), llvm::MachineInstr::getOperand(), llvm::MachineOperand::getReg(), llvm::MachineRegisterInfo::getRegClass(), llvm::MachineFunction::getRegInfo(), getRegisterInfo(), llvm::MachineOperand::isDef(), llvm::MachineOperand::isReg(), llvm::TargetRegisterInfo::isVirtualRegister(), MRI, and llvm::MachineRegisterInfo::setRegClass().

| MachineInstr * AMDGPUInstrInfo::convertToThreeAddress | ( | MachineFunction::iterator & | MFI, |

| MachineBasicBlock::iterator & | MBBI, | ||

| LiveVariables * | LV | ||

| ) | const |

Definition at line 84 of file AMDGPUInstrInfo.cpp.

|

pure virtual |

Implemented in llvm::R600InstrInfo, and llvm::SIInstrInfo.

| bool AMDGPUInstrInfo::DefinesPredicate | ( | MachineInstr * | MI, |

| std::vector< MachineOperand > & | Pred | ||

| ) | const |

Definition at line 254 of file AMDGPUInstrInfo.cpp.

|

virtual |

Definition at line 125 of file AMDGPUInstrInfo.cpp.

References buildIndirectRead(), buildIndirectWrite(), buildMovInstr(), calculateIndirectAddress(), llvm::MachineBasicBlock::erase(), getIndirectAddrRegClass(), llvm::AMDGPU::getNamedOperandIdx(), llvm::MachineBasicBlock::getParent(), llvm::TargetRegisterClass::getRegister(), isRegisterLoad(), and isRegisterStore().

|

protected |

Definition at line 175 of file AMDGPUInstrInfo.cpp.

|

protected |

Definition at line 183 of file AMDGPUInstrInfo.cpp.

|

pure virtual |

Implemented in llvm::R600InstrInfo, and llvm::SIInstrInfo.

|

pure virtual |

Implemented in llvm::R600InstrInfo, and llvm::SIInstrInfo.

Referenced by expandPostRAPseudo(), and getIndirectIndexBegin().

|

protectedvirtual |

Definition at line 279 of file AMDGPUInstrInfo.cpp.

References llvm::TargetRegisterClass::contains(), llvm::MachineFunction::getFrameInfo(), getIndirectAddrRegClass(), llvm::MachineFrameInfo::getNumObjects(), llvm::TargetRegisterClass::getNumRegs(), llvm::MachineFunction::getRegInfo(), llvm::TargetRegisterClass::getRegister(), llvm::TargetRegisterInfo::isVirtualRegister(), llvm::A64CC::LE, LI, llvm::MachineRegisterInfo::livein_begin(), llvm::MachineRegisterInfo::livein_empty(), llvm::MachineRegisterInfo::livein_end(), and MRI.

Referenced by llvm::SIInstrInfo::buildIndirectRead(), llvm::SIInstrInfo::buildIndirectWrite(), getIndirectIndexEnd(), llvm::SIInstrInfo::reserveIndirectRegisters(), and llvm::R600InstrInfo::reserveIndirectRegisters().

|

protectedvirtual |

Definition at line 314 of file AMDGPUInstrInfo.cpp.

References llvm::TargetFrameLowering::getFrameIndexOffset(), llvm::MachineFunction::getFrameInfo(), llvm::TargetMachine::getFrameLowering(), getIndirectIndexBegin(), llvm::MachineFrameInfo::getNumObjects(), llvm::MachineFrameInfo::hasVarSizedObjects(), and TM.

Referenced by llvm::SIInstrInfo::reserveIndirectRegisters(), and llvm::R600InstrInfo::reserveIndirectRegisters().

| int AMDGPUInstrInfo::getMaskedMIMGOp | ( | uint16_t | Opcode, |

| unsigned | Channels | ||

| ) | const |

Given a MIMG Opcode that writes all 4 channels, return the equivalent opcode that writes Channels Channels.

Definition at line 352 of file AMDGPUInstrInfo.cpp.

Referenced by llvm::SITargetLowering::AdjustInstrPostInstrSelection().

| unsigned AMDGPUInstrInfo::getOpcodeAfterMemoryUnfold | ( | unsigned | Opc, |

| bool | UnfoldLoad, | ||

| bool | UnfoldStore, | ||

| unsigned * | LoadRegIndex = 0 |

||

| ) | const |

Definition at line 213 of file AMDGPUInstrInfo.cpp.

|

pure virtual |

Implemented in llvm::R600InstrInfo, and llvm::SIInstrInfo.

Definition at line 37 of file AMDGPUInstrInfo.cpp.

Referenced by convertToISA().

| bool AMDGPUInstrInfo::hasLoadFromStackSlot | ( | const MachineInstr * | MI, |

| const MachineMemOperand *& | MMO, | ||

| int & | FrameIndex | ||

| ) | const |

Definition at line 60 of file AMDGPUInstrInfo.cpp.

| bool AMDGPUInstrInfo::hasStoreFromStackSlot | ( | const MachineInstr * | MI, |

| const MachineMemOperand *& | MMO, | ||

| int & | FrameIndex | ||

| ) | const |

Definition at line 76 of file AMDGPUInstrInfo.cpp.

| void AMDGPUInstrInfo::insertNoop | ( | MachineBasicBlock & | MBB, |

| MachineBasicBlock::iterator | MI | ||

| ) | const |

Definition at line 237 of file AMDGPUInstrInfo.cpp.

| bool llvm::AMDGPUInstrInfo::isAExtLoadInst | ( | llvm::MachineInstr * | MI | ) | const |

| bool AMDGPUInstrInfo::isCoalescableExtInstr | ( | const MachineInstr & | MI, |

| unsigned & | SrcReg, | ||

| unsigned & | DstReg, | ||

| unsigned & | SubIdx | ||

| ) | const |

Definition at line 41 of file AMDGPUInstrInfo.cpp.

| bool llvm::AMDGPUInstrInfo::isExtLoadInst | ( | llvm::MachineInstr * | MI | ) | const |

| unsigned AMDGPUInstrInfo::isLoadFromStackSlot | ( | const MachineInstr * | MI, |

| int & | FrameIndex | ||

| ) | const |

Definition at line 48 of file AMDGPUInstrInfo.cpp.

| unsigned AMDGPUInstrInfo::isLoadFromStackSlotPostFE | ( | const MachineInstr * | MI, |

| int & | FrameIndex | ||

| ) | const |

Definition at line 54 of file AMDGPUInstrInfo.cpp.

| bool llvm::AMDGPUInstrInfo::isLoadInst | ( | llvm::MachineInstr * | MI | ) | const |

Implemented in llvm::R600InstrInfo, and llvm::SIInstrInfo.

| bool AMDGPUInstrInfo::isPredicable | ( | MachineInstr * | MI | ) | const |

Definition at line 260 of file AMDGPUInstrInfo.cpp.

References llvm::MachineInstr::getDesc(), and llvm::MCInstrDesc::isPredicable().

Referenced by llvm::R600InstrInfo::isPredicable().

| bool AMDGPUInstrInfo::isPredicated | ( | const MachineInstr * | MI | ) | const |

Definition at line 242 of file AMDGPUInstrInfo.cpp.

| bool AMDGPUInstrInfo::isRegisterLoad | ( | const MachineInstr & | MI | ) | const |

Definition at line 275 of file AMDGPUInstrInfo.cpp.

References AMDGPU_FLAG_REGISTER_LOAD, and llvm::MachineInstr::getOpcode().

Referenced by expandPostRAPseudo().

| bool AMDGPUInstrInfo::isRegisterStore | ( | const MachineInstr & | MI | ) | const |

Definition at line 271 of file AMDGPUInstrInfo.cpp.

References AMDGPU_FLAG_REGISTER_STORE, and llvm::MachineInstr::getOpcode().

Referenced by expandPostRAPseudo().

| bool AMDGPUInstrInfo::isSafeToMoveRegClassDefs | ( | const TargetRegisterClass * | RC | ) | const |

Definition at line 266 of file AMDGPUInstrInfo.cpp.

| bool llvm::AMDGPUInstrInfo::isSExtLoadInst | ( | llvm::MachineInstr * | MI | ) | const |

| unsigned AMDGPUInstrInfo::isStoreFromStackSlot | ( | const MachineInstr * | MI, |

| int & | FrameIndex | ||

| ) | const |

Definition at line 66 of file AMDGPUInstrInfo.cpp.

| unsigned AMDGPUInstrInfo::isStoreFromStackSlotPostFE | ( | const MachineInstr * | MI, |

| int & | FrameIndex | ||

| ) | const |

Definition at line 71 of file AMDGPUInstrInfo.cpp.

| bool llvm::AMDGPUInstrInfo::isStoreInst | ( | llvm::MachineInstr * | MI | ) | const |

| bool llvm::AMDGPUInstrInfo::isSWSExtLoadInst | ( | llvm::MachineInstr * | MI | ) | const |

| bool llvm::AMDGPUInstrInfo::isTruncStoreInst | ( | llvm::MachineInstr * | MI | ) | const |

| bool llvm::AMDGPUInstrInfo::isZExtLoadInst | ( | llvm::MachineInstr * | MI | ) | const |

| void AMDGPUInstrInfo::loadRegFromStackSlot | ( | MachineBasicBlock & | MBB, |

| MachineBasicBlock::iterator | MI, | ||

| unsigned | DestReg, | ||

| int | FrameIndex, | ||

| const TargetRegisterClass * | RC, | ||

| const TargetRegisterInfo * | TRI | ||

| ) | const |

Definition at line 117 of file AMDGPUInstrInfo.cpp.

| bool AMDGPUInstrInfo::ReverseBranchCondition | ( | SmallVectorImpl< MachineOperand > & | Cond | ) | const |

Definition at line 232 of file AMDGPUInstrInfo.cpp.

| bool AMDGPUInstrInfo::shouldScheduleLoadsNear | ( | SDNode * | Load1, |

| SDNode * | Load2, | ||

| int64_t | Offset1, | ||

| int64_t | Offset2, | ||

| unsigned | NumLoads | ||

| ) | const |

Definition at line 220 of file AMDGPUInstrInfo.cpp.

| void AMDGPUInstrInfo::storeRegToStackSlot | ( | MachineBasicBlock & | MBB, |

| MachineBasicBlock::iterator | MI, | ||

| unsigned | SrcReg, | ||

| bool | isKill, | ||

| int | FrameIndex, | ||

| const TargetRegisterClass * | RC, | ||

| const TargetRegisterInfo * | TRI | ||

| ) | const |

Definition at line 107 of file AMDGPUInstrInfo.cpp.

| bool AMDGPUInstrInfo::SubsumesPredicate | ( | const SmallVectorImpl< MachineOperand > & | Pred1, |

| const SmallVectorImpl< MachineOperand > & | Pred2 | ||

| ) | const |

Definition at line 247 of file AMDGPUInstrInfo.cpp.

| bool AMDGPUInstrInfo::unfoldMemoryOperand | ( | MachineFunction & | MF, |

| MachineInstr * | MI, | ||

| unsigned | Reg, | ||

| bool | UnfoldLoad, | ||

| bool | UnfoldStore, | ||

| SmallVectorImpl< MachineInstr * > & | NewMIs | ||

| ) | const |

Definition at line 197 of file AMDGPUInstrInfo.cpp.

| bool AMDGPUInstrInfo::unfoldMemoryOperand | ( | SelectionDAG & | DAG, |

| SDNode * | N, | ||

| SmallVectorImpl< SDNode * > & | NewNodes | ||

| ) | const |

Definition at line 206 of file AMDGPUInstrInfo.cpp.

|

protected |

Definition at line 48 of file AMDGPUInstrInfo.h.

Referenced by llvm::R600InstrInfo::buildSlotOfVectorInstruction(), getIndirectIndexEnd(), and llvm::R600InstrInfo::reserveIndirectRegisters().