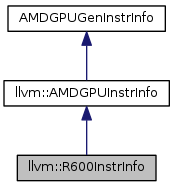

LLVM API Documentation

#include <R600InstrInfo.h>

Public Types | |

| enum | BankSwizzle { ALU_VEC_012_SCL_210 = 0, ALU_VEC_021_SCL_122, ALU_VEC_120_SCL_212, ALU_VEC_102_SCL_221, ALU_VEC_201, ALU_VEC_210 } |

Additional Inherited Members | |

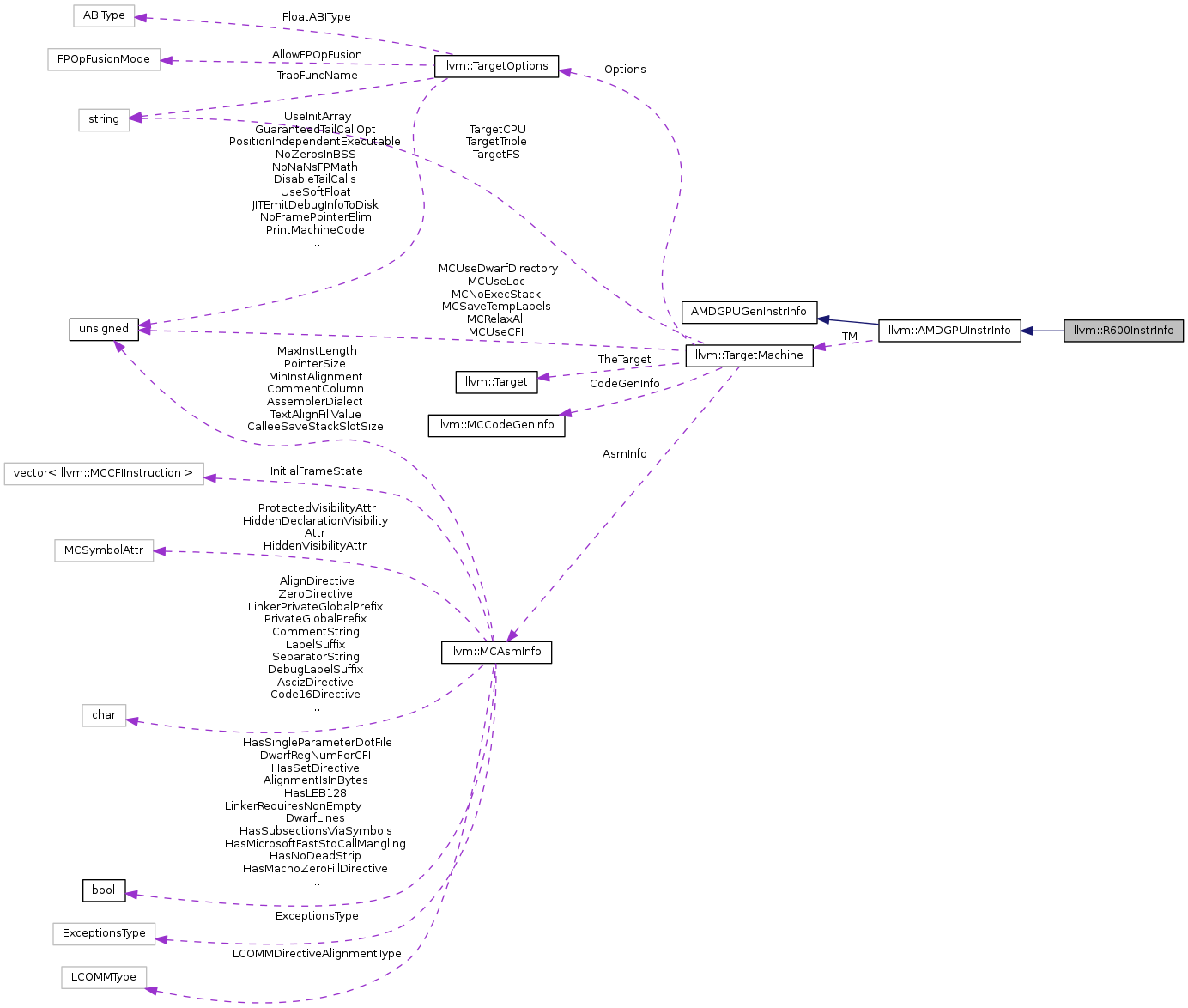

Protected Member Functions inherited from llvm::AMDGPUInstrInfo Protected Member Functions inherited from llvm::AMDGPUInstrInfo | |

| MachineInstr * | foldMemoryOperandImpl (MachineFunction &MF, MachineInstr *MI, const SmallVectorImpl< unsigned > &Ops, int FrameIndex) const |

| MachineInstr * | foldMemoryOperandImpl (MachineFunction &MF, MachineInstr *MI, const SmallVectorImpl< unsigned > &Ops, MachineInstr *LoadMI) const |

| virtual int | getIndirectIndexBegin (const MachineFunction &MF) const |

| virtual int | getIndirectIndexEnd (const MachineFunction &MF) const |

Protected Attributes inherited from llvm::AMDGPUInstrInfo Protected Attributes inherited from llvm::AMDGPUInstrInfo | |

| TargetMachine & | TM |

Definition at line 32 of file R600InstrInfo.h.

| Enumerator | |

|---|---|

| ALU_VEC_012_SCL_210 | |

| ALU_VEC_021_SCL_122 | |

| ALU_VEC_120_SCL_212 | |

| ALU_VEC_102_SCL_221 | |

| ALU_VEC_201 | |

| ALU_VEC_210 | |

Definition at line 42 of file R600InstrInfo.h.

|

explicit |

Definition at line 31 of file R600InstrInfo.cpp.

| void R600InstrInfo::addFlag | ( | MachineInstr * | MI, |

| unsigned | Operand, | ||

| unsigned | Flag | ||

| ) | const |

Add one of the MO_FLAG* flags to the specified Operand.

Definition at line 1356 of file R600InstrInfo.cpp.

References clearFlag(), getFlagOp(), llvm::MachineOperand::getImm(), llvm::MachineInstr::getOpcode(), HAS_NATIVE_OPERANDS, MO_FLAG_LAST, MO_FLAG_MASK, MO_FLAG_NOT_LAST, NUM_MO_FLAGS, and llvm::MachineOperand::setImm().

Referenced by llvm::R600TargetLowering::EmitInstrWithCustomInserter(), and InsertBranch().

| bool R600InstrInfo::AnalyzeBranch | ( | MachineBasicBlock & | MBB, |

| MachineBasicBlock *& | TBB, | ||

| MachineBasicBlock *& | FBB, | ||

| SmallVectorImpl< MachineOperand > & | Cond, | ||

| bool | AllowModify | ||

| ) | const |

Definition at line 694 of file R600InstrInfo.cpp.

References llvm::MachineBasicBlock::begin(), llvm::MachineOperand::CreateReg(), llvm::MachineBasicBlock::end(), llvm::MachineOperand::getMBB(), llvm::MachineInstr::getOpcode(), llvm::MachineInstr::getOperand(), I, isBranch(), isJump(), isPredicateSetter(), and llvm::SmallVectorTemplateBase< T, isPodLike< T >::value >::push_back().

| MachineInstrBuilder R600InstrInfo::buildDefaultInstruction | ( | MachineBasicBlock & | MBB, |

| MachineBasicBlock::iterator | I, | ||

| unsigned | Opcode, | ||

| unsigned | DstReg, | ||

| unsigned | Src0Reg, | ||

| unsigned | Src1Reg = 0 |

||

| ) | const |

buildDefaultInstruction - This function returns a MachineInstr with all the instruction modifiers initialized to their default values. You can use this function to avoid manually specifying each instruction modifier operand when building a new instruction.

Definition at line 1133 of file R600InstrInfo.cpp.

References llvm::MachineInstrBuilder::addImm(), llvm::MachineInstrBuilder::addReg(), llvm::BuildMI(), and llvm::MachineBasicBlock::findDebugLoc().

Referenced by buildIndirectRead(), buildIndirectWrite(), buildMovImm(), buildMovInstr(), buildSlotOfVectorInstruction(), copyPhysReg(), and llvm::R600TargetLowering::EmitInstrWithCustomInserter().

|

virtual |

Build instruction(s) for an indirect register read.

Implements llvm::AMDGPUInstrInfo.

Definition at line 1110 of file R600InstrInfo.cpp.

References llvm::MachineInstrBuilder::addReg(), buildDefaultInstruction(), llvm::RegState::Implicit, llvm::RegState::Kill, setImmOperand(), and llvm::LibFunc::write.

|

virtual |

Build instruction(s) for an indirect register write.

Implements llvm::AMDGPUInstrInfo.

Definition at line 1093 of file R600InstrInfo.cpp.

References llvm::MachineInstrBuilder::addReg(), buildDefaultInstruction(), llvm::RegState::Implicit, llvm::RegState::Kill, setImmOperand(), and llvm::LibFunc::write.

| MachineInstr * R600InstrInfo::buildMovImm | ( | MachineBasicBlock & | BB, |

| MachineBasicBlock::iterator | I, | ||

| unsigned | DstReg, | ||

| uint64_t | Imm | ||

| ) | const |

Definition at line 1261 of file R600InstrInfo.cpp.

References buildDefaultInstruction(), and setImmOperand().

Referenced by llvm::R600TargetLowering::EmitInstrWithCustomInserter().

|

virtual |

Build a MOV instruction.

Implements llvm::AMDGPUInstrInfo.

Definition at line 1271 of file R600InstrInfo.cpp.

References buildDefaultInstruction().

| MachineInstr * R600InstrInfo::buildSlotOfVectorInstruction | ( | MachineBasicBlock & | MBB, |

| MachineInstr * | MI, | ||

| unsigned | Slot, | ||

| unsigned | DstReg | ||

| ) | const |

Definition at line 1212 of file R600InstrInfo.cpp.

References buildDefaultInstruction(), llvm::AMDGPUSubtarget::getGeneration(), llvm::MachineOperand::getImm(), llvm::MachineInstr::getOpcode(), llvm::MachineInstr::getOperand(), getOperandIdx(), llvm::MachineOperand::getReg(), getSlotedOps(), llvm::TargetMachine::getSubtarget(), I, llvm::MachineOperand::isImm(), llvm::A64CC::MI, llvm::AMDGPUSubtarget::R700, llvm::MachineOperand::setImm(), setImmOperand(), llvm::MachineOperand::setReg(), llvm::AMDGPUInstrInfo::TM, and llvm::LibFunc::write.

|

virtual |

Calculate the "Indirect Address" for the given RegIndex and Channel.

We model indirect addressing using a virtual address space that can be accesed with loads and stores. The "Indirect Address" is the memory address in this virtual address space that maps to the given RegIndex and Channel.

Implements llvm::AMDGPUInstrInfo.

Definition at line 1082 of file R600InstrInfo.cpp.

| bool R600InstrInfo::canBeConsideredALU | ( | const MachineInstr * | MI | ) | const |

Opcode represents an ALU instruction or an instruction that will be lowered in ExpandSpecialInstrs Pass. Definition at line 164 of file R600InstrInfo.cpp.

References llvm::TargetOpcode::COPY, llvm::MachineInstr::getOpcode(), isALUInstr(), isCubeOp(), and isVector().

| void R600InstrInfo::clearFlag | ( | MachineInstr * | MI, |

| unsigned | Operand, | ||

| unsigned | Flag | ||

| ) | const |

Clear the specified flag on the instruction.

Definition at line 1377 of file R600InstrInfo.cpp.

References getFlagOp(), llvm::MachineOperand::getImm(), llvm::MachineInstr::getOpcode(), HAS_NATIVE_OPERANDS, NUM_MO_FLAGS, and llvm::MachineOperand::setImm().

Referenced by addFlag(), and RemoveBranch().

|

virtual |

Implements llvm::AMDGPUInstrInfo.

Definition at line 50 of file R600InstrInfo.cpp.

References buildDefaultInstruction(), llvm::RegState::Define, llvm::MachineInstr::getOperand(), getOperandIdx(), llvm::AMDGPURegisterInfo::getSubRegFromChannel(), I, llvm::RegState::Implicit, and llvm::MachineOperand::setIsKill().

| DFAPacketizer * R600InstrInfo::CreateTargetScheduleState | ( | const TargetMachine * | TM, |

| const ScheduleDAG * | DAG | ||

| ) | const |

Definition at line 654 of file R600InstrInfo.cpp.

References llvm::TargetMachine::getInstrItineraryData(), and llvm::TargetMachine::getSubtarget().

| bool R600InstrInfo::definesAddressRegister | ( | MachineInstr * | MI | ) | const |

Definition at line 237 of file R600InstrInfo.cpp.

References llvm::MachineInstr::findRegisterDefOperandIdx().

| bool R600InstrInfo::DefinesPredicate | ( | MachineInstr * | MI, |

| std::vector< MachineOperand > & | Pred | ||

| ) | const |

Definition at line 1001 of file R600InstrInfo.cpp.

References llvm::MachineInstr::getOpcode(), and isPredicateSetter().

| bool R600InstrInfo::FindSwizzleForVectorSlot | ( | const std::vector< std::vector< std::pair< int, unsigned > > > & | IGSrcs, |

| std::vector< R600InstrInfo::BankSwizzle > & | SwzCandidate, | ||

| const std::vector< std::pair< int, unsigned > > & | TransSrcs, | ||

| R600InstrInfo::BankSwizzle | TransSwz | ||

| ) | const |

Enumerate all possible Swizzle sequence to find one that can meet all read port requirements.

Definition at line 512 of file R600InstrInfo.cpp.

References isLegalUpTo(), and NextPossibleSolution().

Referenced by fitsReadPortLimitations().

| bool R600InstrInfo::fitsConstReadLimitations | ( | const std::vector< MachineInstr * > & | MIs | ) | const |

An instruction group can only access 2 channel pair (either [XY] or [ZW]) from KCache bank on R700+. This function check if MI set in input meet this limitations

Definition at line 623 of file R600InstrInfo.cpp.

References llvm::R600RegisterInfo::getHWRegChan(), llvm::MachineInstr::getOpcode(), getSrcs(), llvm::SmallSet< T, N, C >::insert(), isALUInstr(), llvm::SmallSet< T, N, C >::size(), and llvm::SmallVectorTemplateCommon< T >::size().

Referenced by FoldOperand().

Same but using const index set instead of MI set.

Definition at line 598 of file R600InstrInfo.cpp.

| bool R600InstrInfo::fitsReadPortLimitations | ( | const std::vector< MachineInstr * > & | MIs, |

| const DenseMap< unsigned, unsigned > & | PV, | ||

| std::vector< BankSwizzle > & | BS, | ||

| bool | isLastAluTrans | ||

| ) | const |

Given the order VEC_012 < VEC_021 < VEC_120 < VEC_102 < VEC_201 < VEC_210 returns true and the first (in lexical order) BankSwizzle affectation starting from the one already provided in the Instruction Group MIs that fits Read Port limitations in BS if available. Otherwise returns false and undefined content in BS. isLastAluTrans should be set if the last Alu of MIs will be executed on Trans ALU. In this case, ValidTSwizzle returns the BankSwizzle value to apply to the last instruction. PV holds GPR to PV registers in the Instruction Group MIs.

Definition at line 549 of file R600InstrInfo.cpp.

References ALU_VEC_012_SCL_210, ALU_VEC_021_SCL_122, ALU_VEC_102_SCL_221, ALU_VEC_120_SCL_212, FindSwizzleForVectorSlot(), getOperandIdx(), and isConstCompatible().

| MachineOperand & R600InstrInfo::getFlagOp | ( | MachineInstr * | MI, |

| unsigned | SrcIdx = 0, |

||

| unsigned | Flag = 0 |

||

| ) | const |

| SrcIdx | The register source to set the flag on (e.g src0, src1, src2) |

| Flag | The flag being set. |

Definition at line 1301 of file R600InstrInfo.cpp.

References GET_FLAG_OPERAND_IDX, llvm::MachineInstr::getOpcode(), llvm::MachineInstr::getOperand(), getOperandIdx(), HAS_NATIVE_OPERANDS, llvm::MachineOperand::isImm(), MO_FLAG_ABS, MO_FLAG_CLAMP, MO_FLAG_LAST, MO_FLAG_MASK, MO_FLAG_NEG, MO_FLAG_NOT_LAST, R600_InstFlag::OP3, and llvm::LibFunc::write.

Referenced by addFlag(), and clearFlag().

|

virtual |

Implements llvm::AMDGPUInstrInfo.

Definition at line 92 of file R600InstrInfo.cpp.

|

virtual |

Implements llvm::AMDGPUInstrInfo.

Definition at line 1089 of file R600InstrInfo.cpp.

| unsigned int R600InstrInfo::getInstrLatency | ( | const InstrItineraryData * | ItinData, |

| const MachineInstr * | MI, | ||

| unsigned * | PredCost = 0 |

||

| ) | const |

Definition at line 1053 of file R600InstrInfo.cpp.

|

inlinevirtual |

Definition at line 197 of file R600InstrInfo.h.

| unsigned R600InstrInfo::getMaxAlusPerClause | ( | ) | const |

Definition at line 1129 of file R600InstrInfo.cpp.

Referenced by llvm::R600SchedStrategy::initialize().

| int R600InstrInfo::getOperandIdx | ( | const MachineInstr & | MI, |

| unsigned | Op | ||

| ) | const |

Get the index of Op in the MachineInstr.

Op. Definition at line 1277 of file R600InstrInfo.cpp.

References llvm::MachineInstr::getOpcode().

Referenced by buildSlotOfVectorInstruction(), copyPhysReg(), llvm::R600TargetLowering::EmitInstrWithCustomInserter(), fitsReadPortLimitations(), FoldOperand(), getFlagOp(), getSelIdx(), getSrcIdx(), getSrcs(), isLDSNoRetInstr(), isLDSRetInstr(), PredicateInstruction(), and setImmOperand().

Get the index of Op for the given Opcode.

Op. Definition at line 1281 of file R600InstrInfo.cpp.

References llvm::AMDGPU::getNamedOperandIdx().

| unsigned int R600InstrInfo::getPredicationCost | ( | const MachineInstr * | ) | const |

Definition at line 1049 of file R600InstrInfo.cpp.

|

virtual |

Implements llvm::AMDGPUInstrInfo.

Definition at line 37 of file R600InstrInfo.cpp.

Referenced by llvm::R600TargetLowering::LowerOperation().

Definition at line 269 of file R600InstrInfo.cpp.

References getOperandIdx(), and SRC_SEL_ROWS.

Referenced by FoldOperand().

Definition at line 257 of file R600InstrInfo.cpp.

References getOperandIdx().

| SmallVector< std::pair< MachineOperand *, int64_t >, 3 > R600InstrInfo::getSrcs | ( | MachineInstr * | MI | ) | const |

Definition at line 294 of file R600InstrInfo.cpp.

References llvm::MachineOperand::getImm(), llvm::MachineInstr::getOpcode(), llvm::MachineInstr::getOperand(), getOperandIdx(), llvm::MachineOperand::getReg(), and llvm::SmallVectorTemplateBase< T, isPodLike< T >::value >::push_back().

Referenced by fitsConstReadLimitations().

| bool R600InstrInfo::hasFlagOperand | ( | const MachineInstr & | MI | ) | const |

Definition at line 1297 of file R600InstrInfo.cpp.

References GET_FLAG_OPERAND_IDX, and llvm::MachineInstr::getOpcode().

Definition at line 140 of file R600InstrInfo.cpp.

References R600_InstFlag::OP1, R600_InstFlag::OP2, and R600_InstFlag::OP3.

| unsigned R600InstrInfo::InsertBranch | ( | MachineBasicBlock & | MBB, |

| MachineBasicBlock * | TBB, | ||

| MachineBasicBlock * | FBB, | ||

| const SmallVectorImpl< MachineOperand > & | Cond, | ||

| DebugLoc | DL | ||

| ) | const |

Definition at line 787 of file R600InstrInfo.cpp.

References addFlag(), llvm::MachineInstrBuilder::addMBB(), llvm::MachineInstrBuilder::addReg(), llvm::BuildMI(), llvm::SmallVectorBase::empty(), llvm::MachineBasicBlock::end(), findFirstPredicateSetterFrom(), FindLastAluClause(), llvm::MachineInstr::getOperand(), llvm::RegState::Kill, MO_FLAG_PUSH, and llvm::MachineOperand::setImm().

Opcode represents an ALU instruction. Definition at line 134 of file R600InstrInfo.cpp.

References R600_InstFlag::ALU_INST.

Referenced by canBeConsideredALU(), fitsConstReadLimitations(), and readsLDSSrcReg().

Definition at line 123 of file R600InstrInfo.cpp.

Referenced by canBeConsideredALU().

Definition at line 200 of file R600InstrInfo.cpp.

References R600_InstFlag::IS_EXPORT.

| bool llvm::R600InstrInfo::isFlagSet | ( | const MachineInstr & | MI, |

| unsigned | Operand, | ||

| unsigned | Flag | ||

| ) | const |

Determine if the specified Flag is set on this Operand.

Definition at line 148 of file R600InstrInfo.cpp.

References R600_InstFlag::LDS_1A, R600_InstFlag::LDS_1A1D, and R600_InstFlag::LDS_1A2D.

Referenced by isLDSNoRetInstr(), and isLDSRetInstr().

Definition at line 156 of file R600InstrInfo.cpp.

References getOperandIdx(), and isLDSInstr().

Definition at line 160 of file R600InstrInfo.cpp.

References getOperandIdx(), and isLDSInstr().

Referenced by llvm::R600TargetLowering::EmitInstrWithCustomInserter().

| bool R600InstrInfo::isLegalToSplitMBBAt | ( | MachineBasicBlock & | MBB, |

| MachineBasicBlock::iterator | MBBI | ||

| ) | const |

MBBI can be moved into a new basic. Definition at line 81 of file R600InstrInfo.cpp.

References I, llvm::R600RegisterInfo::isPhysRegLiveAcrossClauses(), and llvm::TargetRegisterInfo::isVirtualRegister().

| unsigned R600InstrInfo::isLegalUpTo | ( | const std::vector< std::vector< std::pair< int, unsigned > > > & | IGSrcs, |

| const std::vector< R600InstrInfo::BankSwizzle > & | Swz, | ||

| const std::vector< std::pair< int, unsigned > > & | TransSrcs, | ||

| R600InstrInfo::BankSwizzle | TransSwz | ||

| ) | const |

returns how many MIs (whose inputs are represented by IGSrcs) can be packed in the same Instruction Group while meeting read port limitations given a Swz swizzle sequence.

Definition at line 443 of file R600InstrInfo.cpp.

References ALU_VEC_012_SCL_210, ALU_VEC_021_SCL_122, GET_REG_INDEX, getTransSwizzle(), llvm::Intrinsic::memset, and Swizzle().

Referenced by FindSwizzleForVectorSlot().

Implements llvm::AMDGPUInstrInfo.

Definition at line 96 of file R600InstrInfo.cpp.

Definition at line 111 of file R600InstrInfo.cpp.

References llvm::NVPTXISD::RETURN.

| bool R600InstrInfo::isPredicable | ( | MachineInstr * | MI | ) | const |

Definition at line 907 of file R600InstrInfo.cpp.

References llvm::MachineBasicBlock::begin(), llvm::MachineOperand::getImm(), llvm::MachineInstr::getOpcode(), llvm::MachineInstr::getOperand(), llvm::MachineInstr::getParent(), llvm::AMDGPUInstrInfo::isPredicable(), and isVector().

| bool R600InstrInfo::isPredicated | ( | const MachineInstr * | MI | ) | const |

Definition at line 891 of file R600InstrInfo.cpp.

References llvm::MachineInstr::findFirstPredOperandIdx(), llvm::MachineInstr::getOperand(), and llvm::MachineOperand::getReg().

| bool R600InstrInfo::isProfitableToDupForIfCvt | ( | MachineBasicBlock & | MBB, |

| unsigned | NumCyles, | ||

| const BranchProbability & | Probability | ||

| ) | const |

Definition at line 952 of file R600InstrInfo.cpp.

| bool R600InstrInfo::isProfitableToIfCvt | ( | MachineBasicBlock & | MBB, |

| unsigned | NumCyles, | ||

| unsigned | ExtraPredCycles, | ||

| const BranchProbability & | Probability | ||

| ) | const |

Definition at line 933 of file R600InstrInfo.cpp.

| bool R600InstrInfo::isProfitableToIfCvt | ( | MachineBasicBlock & | TMBB, |

| unsigned | NumTCycles, | ||

| unsigned | ExtraTCycles, | ||

| MachineBasicBlock & | FMBB, | ||

| unsigned | NumFCycles, | ||

| unsigned | ExtraFCycles, | ||

| const BranchProbability & | Probability | ||

| ) | const |

Definition at line 941 of file R600InstrInfo.cpp.

| bool R600InstrInfo::isProfitableToUnpredicate | ( | MachineBasicBlock & | TMBB, |

| MachineBasicBlock & | FMBB | ||

| ) | const |

Definition at line 960 of file R600InstrInfo.cpp.

Definition at line 119 of file R600InstrInfo.cpp.

Definition at line 182 of file R600InstrInfo.cpp.

References llvm::AMDGPUSubtarget::hasCaymanISA().

Referenced by isTransOnly().

| bool R600InstrInfo::isTransOnly | ( | const MachineInstr * | MI | ) | const |

Definition at line 188 of file R600InstrInfo.cpp.

References llvm::MachineInstr::getOpcode(), and isTransOnly().

| bool R600InstrInfo::isTrig | ( | const MachineInstr & | MI | ) | const |

Definition at line 41 of file R600InstrInfo.cpp.

References llvm::MachineInstr::getOpcode(), and R600_InstFlag::TRIG.

| bool R600InstrInfo::isVector | ( | const MachineInstr & | MI | ) | const |

Vector instructions are instructions that must fill all instruction slots within an instruction group.

Definition at line 45 of file R600InstrInfo.cpp.

References llvm::MachineInstr::getOpcode(), and R600_InstFlag::VECTOR.

Referenced by canBeConsideredALU(), and isPredicable().

Definition at line 192 of file R600InstrInfo.cpp.

Referenced by isVectorOnly().

| bool R600InstrInfo::isVectorOnly | ( | const MachineInstr * | MI | ) | const |

Definition at line 196 of file R600InstrInfo.cpp.

References llvm::MachineInstr::getOpcode(), and isVectorOnly().

Definition at line 223 of file R600InstrInfo.cpp.

| bool R600InstrInfo::PredicateInstruction | ( | MachineInstr * | MI, |

| const SmallVectorImpl< MachineOperand > & | Pred | ||

| ) | const |

Definition at line 1015 of file R600InstrInfo.cpp.

References llvm::MachineInstrBuilder::addReg(), llvm::MachineInstr::findFirstPredOperandIdx(), llvm::MachineInstr::getOpcode(), llvm::MachineInstr::getOperand(), getOperandIdx(), llvm::MachineInstr::getParent(), llvm::MachineBasicBlock::getParent(), getReg(), llvm::RegState::Implicit, llvm::A64CC::MI, llvm::MachineOperand::setImm(), and llvm::MachineOperand::setReg().

| bool R600InstrInfo::readsLDSSrcReg | ( | const MachineInstr * | MI | ) | const |

Definition at line 241 of file R600InstrInfo.cpp.

References llvm::MachineInstr::getOpcode(), I, isALUInstr(), llvm::TargetRegisterInfo::isVirtualRegister(), llvm::MachineInstr::operands_begin(), and llvm::MachineInstr::operands_end().

| unsigned R600InstrInfo::RemoveBranch | ( | MachineBasicBlock & | MBB | ) | const |

Definition at line 833 of file R600InstrInfo.cpp.

References llvm::MachineBasicBlock::begin(), clearFlag(), llvm::MachineBasicBlock::end(), findFirstPredicateSetterFrom(), FindLastAluClause(), I, and MO_FLAG_PUSH.

| void R600InstrInfo::reserveIndirectRegisters | ( | BitVector & | Reserved, |

| const MachineFunction & | MF | ||

| ) | const |

Reserve the registers that may be accesed using indirect addressing.

Definition at line 1061 of file R600InstrInfo.cpp.

References llvm::TargetMachine::getFrameLowering(), llvm::AMDGPUInstrInfo::getIndirectIndexBegin(), llvm::AMDGPUInstrInfo::getIndirectIndexEnd(), llvm::AMDGPUFrameLowering::getStackWidth(), llvm::BitVector::set(), and llvm::AMDGPUInstrInfo::TM.

Referenced by llvm::R600RegisterInfo::getReservedRegs().

| bool R600InstrInfo::ReverseBranchCondition | ( | SmallVectorImpl< MachineOperand > & | Cond | ) | const |

Definition at line 967 of file R600InstrInfo.cpp.

References llvm::MachineOperand::getImm(), llvm::MachineOperand::getReg(), OPCODE_IS_NOT_ZERO, OPCODE_IS_NOT_ZERO_INT, OPCODE_IS_ZERO, OPCODE_IS_ZERO_INT, llvm::MachineOperand::setImm(), and llvm::MachineOperand::setReg().

| void R600InstrInfo::setImmOperand | ( | MachineInstr * | MI, |

| unsigned | Op, | ||

| int64_t | Imm | ||

| ) | const |

Helper function for setting instruction flag values.

Definition at line 1285 of file R600InstrInfo.cpp.

References llvm::MachineInstr::getOperand(), getOperandIdx(), llvm::MachineOperand::isImm(), and llvm::MachineOperand::setImm().

Referenced by buildIndirectRead(), buildIndirectWrite(), buildMovImm(), buildSlotOfVectorInstruction(), and llvm::R600TargetLowering::EmitInstrWithCustomInserter().

| bool R600InstrInfo::SubsumesPredicate | ( | const SmallVectorImpl< MachineOperand > & | Pred1, |

| const SmallVectorImpl< MachineOperand > & | Pred2 | ||

| ) | const |

Definition at line 1008 of file R600InstrInfo.cpp.

| bool R600InstrInfo::usesAddressRegister | ( | MachineInstr * | MI | ) | const |

Definition at line 233 of file R600InstrInfo.cpp.

References llvm::MachineInstr::findRegisterUseOperandIdx().

Definition at line 213 of file R600InstrInfo.cpp.

References llvm::AMDGPUSubtarget::hasVertexCache(), IS_TEX, and IS_VTX.

Referenced by usesTextureCache().

| bool R600InstrInfo::usesTextureCache | ( | const MachineInstr * | MI | ) | const |

Definition at line 217 of file R600InstrInfo.cpp.

References ShaderType::COMPUTE, llvm::MachineFunction::getInfo(), llvm::MachineInstr::getOpcode(), llvm::MachineInstr::getParent(), llvm::MachineBasicBlock::getParent(), llvm::AMDGPUMachineFunction::ShaderType, usesTextureCache(), and usesVertexCache().

Definition at line 204 of file R600InstrInfo.cpp.

References llvm::AMDGPUSubtarget::hasVertexCache(), and IS_VTX.

Referenced by usesTextureCache(), and usesVertexCache().

| bool R600InstrInfo::usesVertexCache | ( | const MachineInstr * | MI | ) | const |

Definition at line 208 of file R600InstrInfo.cpp.

References ShaderType::COMPUTE, llvm::MachineFunction::getInfo(), llvm::MachineInstr::getOpcode(), llvm::MachineInstr::getParent(), llvm::MachineBasicBlock::getParent(), llvm::AMDGPUMachineFunction::ShaderType, and usesVertexCache().