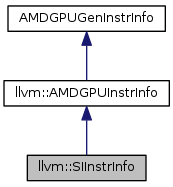

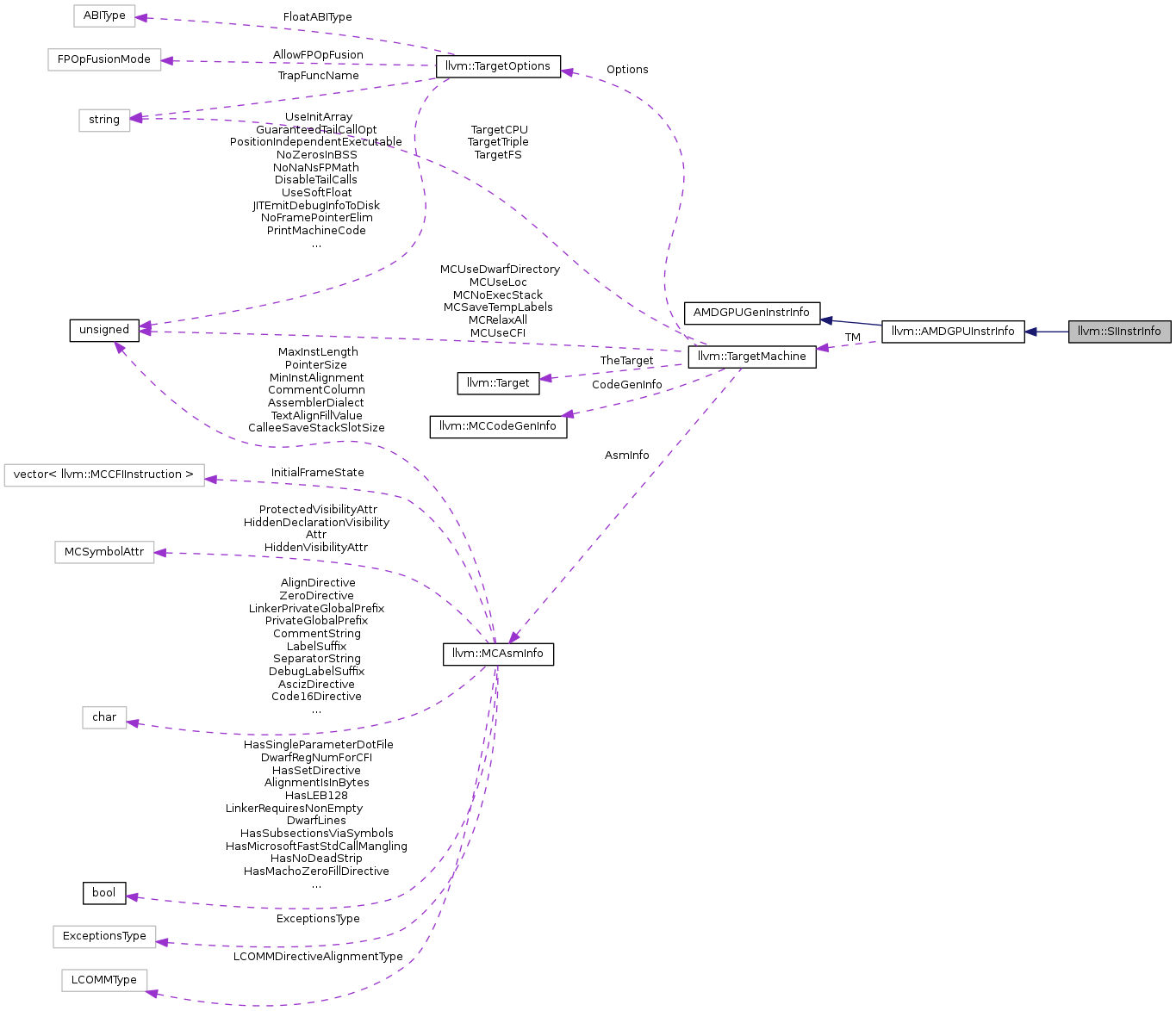

LLVM API Documentation

#include <SIInstrInfo.h>

Public Member Functions | |

| SIInstrInfo (AMDGPUTargetMachine &tm) | |

| const SIRegisterInfo & | getRegisterInfo () const |

| virtual void | copyPhysReg (MachineBasicBlock &MBB, MachineBasicBlock::iterator MI, DebugLoc DL, unsigned DestReg, unsigned SrcReg, bool KillSrc) const |

| unsigned | commuteOpcode (unsigned Opcode) const |

| virtual MachineInstr * | commuteInstruction (MachineInstr *MI, bool NewMI=false) const |

| virtual unsigned | getIEQOpcode () const |

| MachineInstr * | buildMovInstr (MachineBasicBlock *MBB, MachineBasicBlock::iterator I, unsigned DstReg, unsigned SrcReg) const |

| Build a MOV instruction. More... | |

| virtual bool | isMov (unsigned Opcode) const |

| virtual bool | isSafeToMoveRegClassDefs (const TargetRegisterClass *RC) const |

| int | isMIMG (uint16_t Opcode) const |

| int | isSMRD (uint16_t Opcode) const |

| bool | isVOP1 (uint16_t Opcode) const |

| bool | isVOP2 (uint16_t Opcode) const |

| bool | isVOP3 (uint16_t Opcode) const |

| bool | isVOPC (uint16_t Opcode) const |

| bool | isInlineConstant (const MachineOperand &MO) const |

| bool | isLiteralConstant (const MachineOperand &MO) const |

| virtual bool | verifyInstruction (const MachineInstr *MI, StringRef &ErrInfo) const |

| bool | isSALUInstr (const MachineInstr &MI) const |

| bool | isSALUOpSupportedOnVALU (const MachineInstr &MI) const |

| const TargetRegisterClass * | getOpRegClass (const MachineInstr &MI, unsigned OpNo) const |

Return the correct register class for OpNo. For target-specific instructions, this will return the register class that has been defined in tablegen. For generic instructions, like REG_SEQUENCE it will return the register class of its machine operand. to infer the correct register class base on the other operands. More... | |

| bool | canReadVGPR (const MachineInstr &MI, unsigned OpNo) const |

| void | legalizeOpWithMove (MachineInstr *MI, unsigned OpIdx) const |

Legalize the OpIndex operand of this instruction by inserting a MOV. For example: ADD_I32_e32 VGPR0, 15 to MOV VGPR1, 15 ADD_I32_e32 VGPR0, VGPR1. More... | |

| void | legalizeOperands (MachineInstr *MI) const |

Legalize all operands in this instruction. This function may create new instruction and insert them before MI. More... | |

| void | moveToVALU (MachineInstr &MI) const |

Replace this instruction's opcode with the equivalent VALU opcode. This function will also move the users of MI to the VALU if necessary. More... | |

| virtual unsigned | calculateIndirectAddress (unsigned RegIndex, unsigned Channel) const |

Calculate the "Indirect Address" for the given RegIndex and Channel. More... | |

| virtual const TargetRegisterClass * | getIndirectAddrRegClass () const |

| virtual MachineInstrBuilder | buildIndirectWrite (MachineBasicBlock *MBB, MachineBasicBlock::iterator I, unsigned ValueReg, unsigned Address, unsigned OffsetReg) const |

| Build instruction(s) for an indirect register write. More... | |

| virtual MachineInstrBuilder | buildIndirectRead (MachineBasicBlock *MBB, MachineBasicBlock::iterator I, unsigned ValueReg, unsigned Address, unsigned OffsetReg) const |

| Build instruction(s) for an indirect register read. More... | |

| void | reserveIndirectRegisters (BitVector &Reserved, const MachineFunction &MF) const |

| void | LoadM0 (MachineInstr *MoveRel, MachineBasicBlock::iterator I, unsigned SavReg, unsigned IndexReg) const |

Public Member Functions inherited from llvm::AMDGPUInstrInfo Public Member Functions inherited from llvm::AMDGPUInstrInfo | |

| AMDGPUInstrInfo (TargetMachine &tm) | |

| bool | isCoalescableExtInstr (const MachineInstr &MI, unsigned &SrcReg, unsigned &DstReg, unsigned &SubIdx) const |

| unsigned | isLoadFromStackSlot (const MachineInstr *MI, int &FrameIndex) const |

| unsigned | isLoadFromStackSlotPostFE (const MachineInstr *MI, int &FrameIndex) const |

| bool | hasLoadFromStackSlot (const MachineInstr *MI, const MachineMemOperand *&MMO, int &FrameIndex) const |

| unsigned | isStoreFromStackSlot (const MachineInstr *MI, int &FrameIndex) const |

| unsigned | isStoreFromStackSlotPostFE (const MachineInstr *MI, int &FrameIndex) const |

| bool | hasStoreFromStackSlot (const MachineInstr *MI, const MachineMemOperand *&MMO, int &FrameIndex) const |

| MachineInstr * | convertToThreeAddress (MachineFunction::iterator &MFI, MachineBasicBlock::iterator &MBBI, LiveVariables *LV) const |

| void | storeRegToStackSlot (MachineBasicBlock &MBB, MachineBasicBlock::iterator MI, unsigned SrcReg, bool isKill, int FrameIndex, const TargetRegisterClass *RC, const TargetRegisterInfo *TRI) const |

| void | loadRegFromStackSlot (MachineBasicBlock &MBB, MachineBasicBlock::iterator MI, unsigned DestReg, int FrameIndex, const TargetRegisterClass *RC, const TargetRegisterInfo *TRI) const |

| virtual bool | expandPostRAPseudo (MachineBasicBlock::iterator MI) const |

| bool | canFoldMemoryOperand (const MachineInstr *MI, const SmallVectorImpl< unsigned > &Ops) const |

| bool | unfoldMemoryOperand (MachineFunction &MF, MachineInstr *MI, unsigned Reg, bool UnfoldLoad, bool UnfoldStore, SmallVectorImpl< MachineInstr * > &NewMIs) const |

| bool | unfoldMemoryOperand (SelectionDAG &DAG, SDNode *N, SmallVectorImpl< SDNode * > &NewNodes) const |

| unsigned | getOpcodeAfterMemoryUnfold (unsigned Opc, bool UnfoldLoad, bool UnfoldStore, unsigned *LoadRegIndex=0) const |

| bool | shouldScheduleLoadsNear (SDNode *Load1, SDNode *Load2, int64_t Offset1, int64_t Offset2, unsigned NumLoads) const |

| bool | ReverseBranchCondition (SmallVectorImpl< MachineOperand > &Cond) const |

| void | insertNoop (MachineBasicBlock &MBB, MachineBasicBlock::iterator MI) const |

| bool | isPredicated (const MachineInstr *MI) const |

| bool | SubsumesPredicate (const SmallVectorImpl< MachineOperand > &Pred1, const SmallVectorImpl< MachineOperand > &Pred2) const |

| bool | DefinesPredicate (MachineInstr *MI, std::vector< MachineOperand > &Pred) const |

| bool | isPredicable (MachineInstr *MI) const |

| bool | isSafeToMoveRegClassDefs (const TargetRegisterClass *RC) const |

| bool | isLoadInst (llvm::MachineInstr *MI) const |

| bool | isExtLoadInst (llvm::MachineInstr *MI) const |

| bool | isSWSExtLoadInst (llvm::MachineInstr *MI) const |

| bool | isSExtLoadInst (llvm::MachineInstr *MI) const |

| bool | isZExtLoadInst (llvm::MachineInstr *MI) const |

| bool | isAExtLoadInst (llvm::MachineInstr *MI) const |

| bool | isStoreInst (llvm::MachineInstr *MI) const |

| bool | isTruncStoreInst (llvm::MachineInstr *MI) const |

| bool | isRegisterStore (const MachineInstr &MI) const |

| bool | isRegisterLoad (const MachineInstr &MI) const |

| virtual void | convertToISA (MachineInstr &MI, MachineFunction &MF, DebugLoc DL) const |

| Convert the AMDIL MachineInstr to a supported ISA MachineInstr. More... | |

| int | getMaskedMIMGOp (uint16_t Opcode, unsigned Channels) const |

Given a MIMG Opcode that writes all 4 channels, return the equivalent opcode that writes Channels Channels. More... | |

Static Public Member Functions | |

| static unsigned | getVALUOp (const MachineInstr &MI) |

Additional Inherited Members | |

Protected Member Functions inherited from llvm::AMDGPUInstrInfo Protected Member Functions inherited from llvm::AMDGPUInstrInfo | |

| MachineInstr * | foldMemoryOperandImpl (MachineFunction &MF, MachineInstr *MI, const SmallVectorImpl< unsigned > &Ops, int FrameIndex) const |

| MachineInstr * | foldMemoryOperandImpl (MachineFunction &MF, MachineInstr *MI, const SmallVectorImpl< unsigned > &Ops, MachineInstr *LoadMI) const |

| virtual int | getIndirectIndexBegin (const MachineFunction &MF) const |

| virtual int | getIndirectIndexEnd (const MachineFunction &MF) const |

Protected Attributes inherited from llvm::AMDGPUInstrInfo Protected Attributes inherited from llvm::AMDGPUInstrInfo | |

| TargetMachine & | TM |

Definition at line 24 of file SIInstrInfo.h.

|

explicit |

Definition at line 25 of file SIInstrInfo.cpp.

|

virtual |

Build instruction(s) for an indirect register read.

Implements llvm::AMDGPUInstrInfo.

Definition at line 663 of file SIInstrInfo.cpp.

References llvm::MachineInstrBuilder::addImm(), llvm::MachineInstrBuilder::addOperand(), llvm::MachineInstrBuilder::addReg(), llvm::BuildMI(), llvm::MachineBasicBlock::findDebugLoc(), llvm::AMDGPUInstrInfo::getIndirectIndexBegin(), and llvm::MachineBasicBlock::getParent().

|

virtual |

Build instruction(s) for an indirect register write.

Implements llvm::AMDGPUInstrInfo.

Definition at line 645 of file SIInstrInfo.cpp.

References llvm::MachineInstrBuilder::addImm(), llvm::MachineInstrBuilder::addOperand(), llvm::MachineInstrBuilder::addReg(), llvm::BuildMI(), llvm::RegState::Define, llvm::MachineBasicBlock::findDebugLoc(), llvm::AMDGPUInstrInfo::getIndirectIndexBegin(), and llvm::MachineBasicBlock::getParent().

|

virtual |

Build a MOV instruction.

Implements llvm::AMDGPUInstrInfo.

Definition at line 228 of file SIInstrInfo.cpp.

References llvm::MachineInstrBuilder::addReg(), llvm::BuildMI(), and llvm::MachineBasicBlock::findDebugLoc().

|

virtual |

Calculate the "Indirect Address" for the given RegIndex and Channel.

We model indirect addressing using a virtual address space that can be accesed with loads and stores. The "Indirect Address" is the memory address in this virtual address space that maps to the given RegIndex and Channel.

Implements llvm::AMDGPUInstrInfo.

Definition at line 635 of file SIInstrInfo.cpp.

| bool SIInstrInfo::canReadVGPR | ( | const MachineInstr & | MI, |

| unsigned | OpNo | ||

| ) | const |

OpNo to read a VGPR. Definition at line 405 of file SIInstrInfo.cpp.

References llvm::TargetOpcode::COPY, llvm::MachineInstr::getOpcode(), getOpRegClass(), llvm::SIRegisterInfo::hasVGPRs(), and llvm::TargetOpcode::REG_SEQUENCE.

Referenced by moveToVALU().

|

virtual |

Definition at line 188 of file SIInstrInfo.cpp.

References llvm::LibFunc::abs, llvm::MachineOperand::ChangeToImmediate(), llvm::MachineOperand::ChangeToRegister(), llvm::TargetInstrInfo::commuteInstruction(), commuteOpcode(), llvm::MachineOperand::getImm(), llvm::AMDGPU::getNamedOperandIdx(), llvm::MachineInstr::getNumOperands(), llvm::MachineInstr::getOpcode(), llvm::MachineInstr::getOperand(), llvm::MachineInstr::getParent(), llvm::MachineBasicBlock::getParent(), llvm::MachineOperand::getReg(), llvm::MachineRegisterInfo::getRegClass(), llvm::MachineFunction::getRegInfo(), llvm::MachineOperand::isFPImm(), llvm::MachineOperand::isReg(), llvm::SIRegisterInfo::isSGPRClass(), isVOP2(), isVOP3(), llvm::A64CC::MI, MRI, and llvm::MachineInstr::setDesc().

Referenced by legalizeOperands().

Definition at line 174 of file SIInstrInfo.cpp.

References llvm::AMDGPU::getCommuteOrig(), and llvm::AMDGPU::getCommuteRev().

Referenced by commuteInstruction().

|

virtual |

Implements llvm::AMDGPUInstrInfo.

Definition at line 39 of file SIInstrInfo.cpp.

References llvm::MachineInstrBuilder::addReg(), llvm::BuildMI(), llvm::TargetOpcode::COPY, llvm::RegState::Define, llvm::getKillRegState(), I, llvm::RegState::Implicit, llvm_unreachable, and llvm::MachineBasicBlock::rend().

|

inlinevirtual |

Implements llvm::AMDGPUInstrInfo.

Definition at line 51 of file SIInstrInfo.h.

|

virtual |

Implements llvm::AMDGPUInstrInfo.

Definition at line 641 of file SIInstrInfo.cpp.

| const TargetRegisterClass * SIInstrInfo::getOpRegClass | ( | const MachineInstr & | MI, |

| unsigned | OpNo | ||

| ) | const |

Return the correct register class for OpNo. For target-specific instructions, this will return the register class that has been defined in tablegen. For generic instructions, like REG_SEQUENCE it will return the register class of its machine operand. to infer the correct register class base on the other operands.

Definition at line 393 of file SIInstrInfo.cpp.

References llvm::MCInstrDesc::getNumOperands(), llvm::MachineInstr::getOpcode(), llvm::MachineInstr::getOperand(), llvm::MachineInstr::getParent(), llvm::MachineBasicBlock::getParent(), llvm::MachineOperand::getReg(), llvm::MachineRegisterInfo::getRegClass(), llvm::MachineFunction::getRegInfo(), llvm::MachineInstr::isVariadic(), MRI, llvm::MCInstrDesc::OpInfo, and llvm::MCOperandInfo::RegClass.

Referenced by canReadVGPR(), legalizeOperands(), and moveToVALU().

|

virtual |

Implements llvm::AMDGPUInstrInfo.

Definition at line 30 of file SIInstrInfo.cpp.

|

static |

Definition at line 370 of file SIInstrInfo.cpp.

References llvm::TargetOpcode::COPY, llvm::MachineInstr::getOpcode(), llvm::TargetOpcode::PHI, and llvm::TargetOpcode::REG_SEQUENCE.

Referenced by isSALUOpSupportedOnVALU(), and moveToVALU().

| bool SIInstrInfo::isInlineConstant | ( | const MachineOperand & | MO | ) | const |

Definition at line 280 of file SIInstrInfo.cpp.

References llvm::MachineOperand::getFPImm(), llvm::MachineOperand::getImm(), llvm::ConstantFP::isExactlyValue(), llvm::MachineOperand::isFPImm(), and llvm::MachineOperand::isImm().

Referenced by isLiteralConstant().

| bool SIInstrInfo::isLiteralConstant | ( | const MachineOperand & | MO | ) | const |

Definition at line 298 of file SIInstrInfo.cpp.

References llvm::MachineOperand::isFPImm(), llvm::MachineOperand::isImm(), and isInlineConstant().

Referenced by legalizeOperands(), and verifyInstruction().

| int SIInstrInfo::isMIMG | ( | uint16_t | Opcode | ) | const |

Definition at line 252 of file SIInstrInfo.cpp.

References SIInstrFlags::MIMG.

Referenced by llvm::SITargetLowering::AdjustInstrPostInstrSelection(), and llvm::SITargetLowering::PostISelFolding().

Implements llvm::AMDGPUInstrInfo.

Definition at line 236 of file SIInstrInfo.cpp.

|

virtual |

Definition at line 248 of file SIInstrInfo.cpp.

| bool SIInstrInfo::isSALUInstr | ( | const MachineInstr & | MI | ) | const |

Definition at line 276 of file SIInstrInfo.cpp.

References llvm::MachineInstr::getOpcode(), and SIInstrFlags::SALU.

| bool SIInstrInfo::isSALUOpSupportedOnVALU | ( | const MachineInstr & | MI | ) | const |

Definition at line 389 of file SIInstrInfo.cpp.

References getVALUOp().

| int SIInstrInfo::isSMRD | ( | uint16_t | Opcode | ) | const |

Definition at line 256 of file SIInstrInfo.cpp.

References SIInstrFlags::SMRD.

| bool SIInstrInfo::isVOP1 | ( | uint16_t | Opcode | ) | const |

Definition at line 260 of file SIInstrInfo.cpp.

References SIInstrFlags::VOP1.

Referenced by verifyInstruction().

| bool SIInstrInfo::isVOP2 | ( | uint16_t | Opcode | ) | const |

Definition at line 264 of file SIInstrInfo.cpp.

References SIInstrFlags::VOP2.

Referenced by commuteInstruction(), legalizeOperands(), and verifyInstruction().

| bool SIInstrInfo::isVOP3 | ( | uint16_t | Opcode | ) | const |

Definition at line 268 of file SIInstrInfo.cpp.

References SIInstrFlags::VOP3.

Referenced by commuteInstruction(), legalizeOperands(), and verifyInstruction().

| bool SIInstrInfo::isVOPC | ( | uint16_t | Opcode | ) | const |

Definition at line 272 of file SIInstrInfo.cpp.

References SIInstrFlags::VOPC.

Referenced by verifyInstruction().

| void SIInstrInfo::legalizeOperands | ( | MachineInstr * | MI | ) | const |

Legalize all operands in this instruction. This function may create new instruction and insert them before MI.

Definition at line 435 of file SIInstrInfo.cpp.

References llvm::MachineInstrBuilder::addOperand(), llvm::BuildMI(), commuteInstruction(), llvm::TargetOpcode::COPY, llvm::MachineRegisterInfo::createVirtualRegister(), llvm::MachineInstr::getDebugLoc(), llvm::SIRegisterInfo::getEquivalentVGPRClass(), llvm::AMDGPU::getNamedOperandIdx(), llvm::MachineInstr::getNumOperands(), llvm::MachineInstr::getOpcode(), llvm::MachineInstr::getOperand(), getOpRegClass(), llvm::MachineInstr::getParent(), llvm::MachineBasicBlock::getParent(), llvm::MachineOperand::getReg(), llvm::MachineRegisterInfo::getRegClass(), llvm::MachineFunction::getRegInfo(), llvm::SIRegisterInfo::hasVGPRs(), llvm::MachineInstr::isCommutable(), llvm::MachineOperand::isFPImm(), llvm::MachineOperand::isImm(), isLiteralConstant(), llvm::MachineOperand::isReg(), llvm::SIRegisterInfo::isSGPRClass(), llvm::TargetRegisterInfo::isVirtualRegister(), isVOP2(), isVOP3(), legalizeOpWithMove(), llvm::A64CC::MI, MRI, llvm::MachineInstr::readsRegister(), llvm::TargetOpcode::REG_SEQUENCE, and llvm::MachineOperand::setReg().

Referenced by moveToVALU().

| void SIInstrInfo::legalizeOpWithMove | ( | MachineInstr * | MI, |

| unsigned | OpIdx | ||

| ) | const |

Legalize the OpIndex operand of this instruction by inserting a MOV. For example: ADD_I32_e32 VGPR0, 15 to MOV VGPR1, 15 ADD_I32_e32 VGPR0, VGPR1.

If the operand being legalized is a register, then a COPY will be used instead of MOV.

Definition at line 415 of file SIInstrInfo.cpp.

References llvm::MachineInstrBuilder::addOperand(), llvm::BuildMI(), llvm::MachineOperand::ChangeToRegister(), llvm::TargetOpcode::COPY, llvm::MachineRegisterInfo::createVirtualRegister(), llvm::MachineBasicBlock::findDebugLoc(), llvm::SIRegisterInfo::getEquivalentVGPRClass(), llvm::MachineInstr::getOpcode(), llvm::MachineInstr::getOperand(), llvm::MachineInstr::getParent(), llvm::MachineBasicBlock::getParent(), llvm::MachineFunction::getRegInfo(), I, llvm::MachineOperand::isReg(), llvm::SIRegisterInfo::isSGPRClass(), llvm::A64CC::MI, and MRI.

Referenced by legalizeOperands().

| void llvm::SIInstrInfo::LoadM0 | ( | MachineInstr * | MoveRel, |

| MachineBasicBlock::iterator | I, | ||

| unsigned | SavReg, | ||

| unsigned | IndexReg | ||

| ) | const |

| void SIInstrInfo::moveToVALU | ( | MachineInstr & | MI | ) | const |

Replace this instruction's opcode with the equivalent VALU opcode. This function will also move the users of MI to the VALU if necessary.

Definition at line 554 of file SIInstrInfo.cpp.

References llvm::MachineInstr::addOperand(), canReadVGPR(), llvm::TargetOpcode::COPY, llvm::MachineOperand::CreateReg(), llvm::MachineRegisterInfo::createVirtualRegister(), llvm::SmallVectorBase::empty(), llvm::SIRegisterInfo::getEquivalentVGPRClass(), llvm::MachineInstr::getNumOperands(), llvm::MachineInstr::getOpcode(), llvm::MachineInstr::getOperand(), getOpRegClass(), llvm::MachineInstr::getParent(), llvm::MachineBasicBlock::getParent(), llvm::MachineOperand::getReg(), llvm::MachineFunction::getRegInfo(), getVALUOp(), llvm::SIRegisterInfo::hasVGPRs(), I, llvm::MCInstrDesc::ImplicitDefs, llvm::MCInstrDesc::ImplicitUses, llvm::MachineOperand::isReg(), legalizeOperands(), MRI, llvm::TargetOpcode::PHI, llvm::SmallVectorImpl< T >::pop_back_val(), llvm::SmallVectorTemplateBase< T, isPodLike< T >::value >::push_back(), llvm::TargetOpcode::REG_SEQUENCE, llvm::MachineInstr::RemoveOperand(), llvm::MachineRegisterInfo::replaceRegWith(), llvm::MachineInstr::setDesc(), llvm::MachineRegisterInfo::use_begin(), and llvm::MachineRegisterInfo::use_end().

| void SIInstrInfo::reserveIndirectRegisters | ( | BitVector & | Reserved, |

| const MachineFunction & | MF | ||

| ) | const |

Definition at line 681 of file SIInstrInfo.cpp.

References llvm::AMDGPUInstrInfo::getIndirectIndexBegin(), llvm::AMDGPUInstrInfo::getIndirectIndexEnd(), and llvm::BitVector::set().

Referenced by llvm::SIRegisterInfo::getReservedRegs().

|

virtual |

Definition at line 302 of file SIInstrInfo.cpp.

References llvm::AMDGPU::getNamedOperandIdx(), llvm::MachineInstr::getNumOperands(), llvm::MachineInstr::getOpcode(), llvm::MachineInstr::getOperand(), llvm::MachineOperand::getReg(), llvm::MachineOperand::isFPImm(), llvm::MachineOperand::isImm(), llvm::MachineOperand::isImplicit(), isLiteralConstant(), llvm::MachineOperand::isReg(), llvm::MachineOperand::isUse(), llvm::TargetRegisterInfo::isVirtualRegister(), isVOP1(), isVOP2(), isVOP3(), and isVOPC().