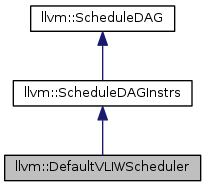

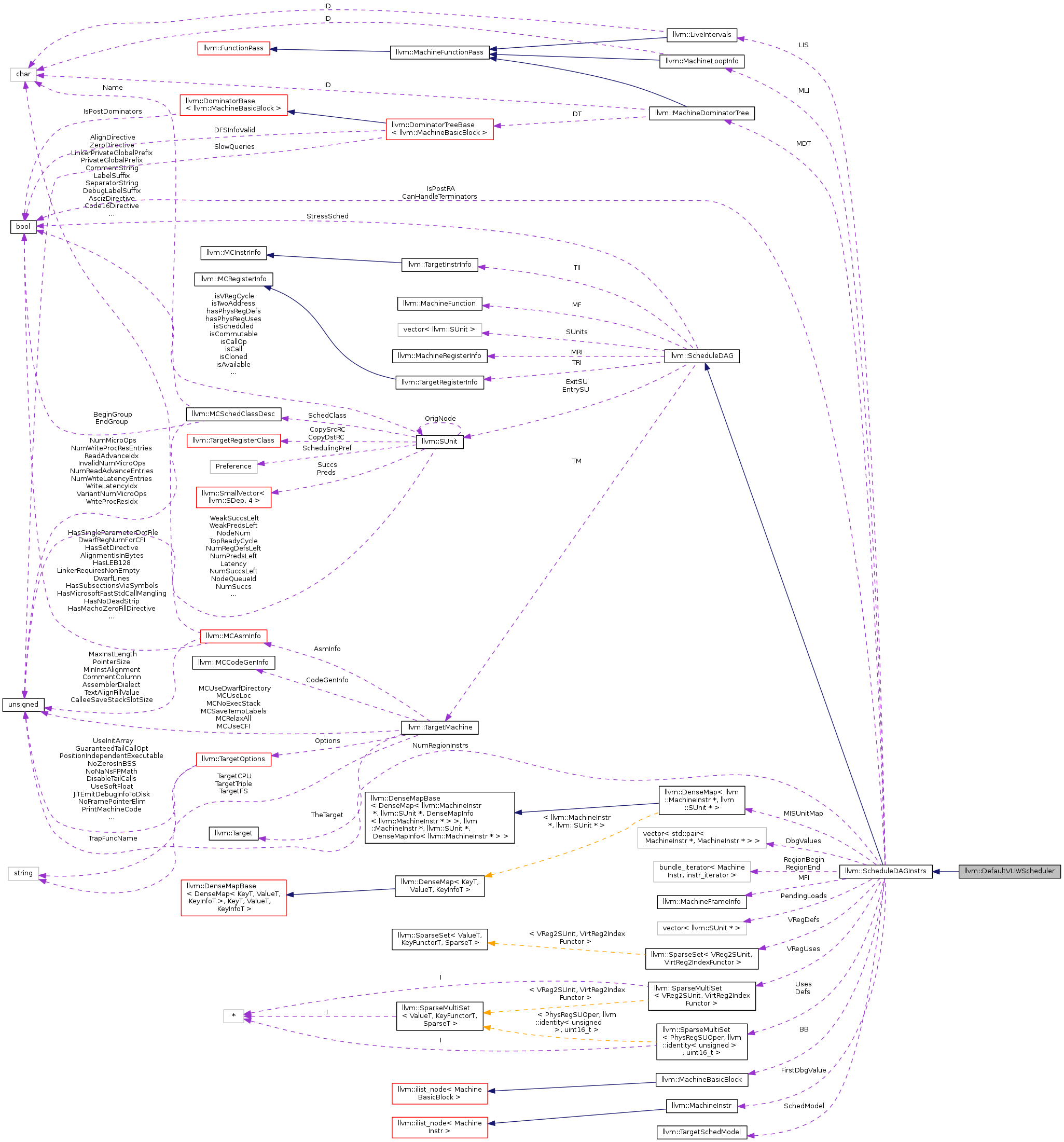

LLVM API Documentation

Public Member Functions | |

| DefaultVLIWScheduler (MachineFunction &MF, MachineLoopInfo &MLI, MachineDominatorTree &MDT, bool IsPostRA) | |

| void | schedule () |

Public Member Functions inherited from llvm::ScheduleDAGInstrs Public Member Functions inherited from llvm::ScheduleDAGInstrs | |

| ScheduleDAGInstrs (MachineFunction &mf, const MachineLoopInfo &mli, const MachineDominatorTree &mdt, bool IsPostRAFlag, LiveIntervals *LIS=0) | |

| virtual | ~ScheduleDAGInstrs () |

| LiveIntervals * | getLIS () const |

| Expose LiveIntervals for use in DAG mutators and such. More... | |

| const TargetSchedModel * | getSchedModel () const |

| Get the machine model for instruction scheduling. More... | |

| const MCSchedClassDesc * | getSchedClass (SUnit *SU) const |

| Resolve and cache a resolved scheduling class for an SUnit. More... | |

| MachineBasicBlock::iterator | begin () const |

| begin - Return an iterator to the top of the current scheduling region. More... | |

| MachineBasicBlock::iterator | end () const |

| end - Return an iterator to the bottom of the current scheduling region. More... | |

| SUnit * | newSUnit (MachineInstr *MI) |

| newSUnit - Creates a new SUnit and return a ptr to it. More... | |

| SUnit * | getSUnit (MachineInstr *MI) const |

| getSUnit - Return an existing SUnit for this MI, or NULL. More... | |

| virtual void | startBlock (MachineBasicBlock *BB) |

| startBlock - Prepare to perform scheduling in the given block. More... | |

| virtual void | finishBlock () |

| finishBlock - Clean up after scheduling in the given block. More... | |

| virtual void | enterRegion (MachineBasicBlock *bb, MachineBasicBlock::iterator begin, MachineBasicBlock::iterator end, unsigned regioninstrs) |

| Initialize the scheduler state for the next scheduling region. More... | |

| virtual void | exitRegion () |

| Notify that the scheduler has finished scheduling the current region. More... | |

| void | buildSchedGraph (AliasAnalysis *AA, RegPressureTracker *RPTracker=0, PressureDiffs *PDiffs=0) |

| void | addSchedBarrierDeps () |

| virtual void | finalizeSchedule () |

| virtual void | dumpNode (const SUnit *SU) const |

| virtual std::string | getGraphNodeLabel (const SUnit *SU) const |

| Return a label for a DAG node that points to an instruction. More... | |

| virtual std::string | getDAGName () const |

| Return a label for the region of code covered by the DAG. More... | |

Public Member Functions inherited from llvm::ScheduleDAG Public Member Functions inherited from llvm::ScheduleDAG | |

| ScheduleDAG (MachineFunction &mf) | |

| virtual | ~ScheduleDAG () |

| void | clearDAG () |

| clearDAG - clear the DAG state (between regions). More... | |

| const MCInstrDesc * | getInstrDesc (const SUnit *SU) const |

| virtual void | viewGraph (const Twine &Name, const Twine &Title) |

| virtual void | viewGraph () |

| Out-of-line implementation with no arguments is handy for gdb. More... | |

| virtual void | addCustomGraphFeatures (GraphWriter< ScheduleDAG * > &) const |

| unsigned | VerifyScheduledDAG (bool isBottomUp) |

Additional Inherited Members | |

Public Attributes inherited from llvm::ScheduleDAG Public Attributes inherited from llvm::ScheduleDAG | |

| const TargetMachine & | TM |

| const TargetInstrInfo * | TII |

| const TargetRegisterInfo * | TRI |

| MachineFunction & | MF |

| MachineRegisterInfo & | MRI |

| std::vector< SUnit > | SUnits |

| SUnit | EntrySU |

| SUnit | ExitSU |

| bool | StressSched |

Protected Types inherited from llvm::ScheduleDAGInstrs Protected Types inherited from llvm::ScheduleDAGInstrs | |

| typedef std::vector< std::pair < MachineInstr *, MachineInstr * > > | DbgValueVector |

Protected Member Functions inherited from llvm::ScheduleDAGInstrs Protected Member Functions inherited from llvm::ScheduleDAGInstrs | |

| void | initSUnits () |

| void | addPhysRegDataDeps (SUnit *SU, unsigned OperIdx) |

| void | addPhysRegDeps (SUnit *SU, unsigned OperIdx) |

| void | addVRegDefDeps (SUnit *SU, unsigned OperIdx) |

| void | addVRegUseDeps (SUnit *SU, unsigned OperIdx) |

Protected Attributes inherited from llvm::ScheduleDAGInstrs Protected Attributes inherited from llvm::ScheduleDAGInstrs | |

| const MachineLoopInfo & | MLI |

| const MachineDominatorTree & | MDT |

| const MachineFrameInfo * | MFI |

| LiveIntervals * | LIS |

| Live Intervals provides reaching defs in preRA scheduling. More... | |

| TargetSchedModel | SchedModel |

| TargetSchedModel provides an interface to the machine model. More... | |

| bool | IsPostRA |

| isPostRA flag indicates vregs cannot be present. More... | |

| bool | CanHandleTerminators |

| MachineBasicBlock * | BB |

| The block in which to insert instructions. More... | |

| MachineBasicBlock::iterator | RegionBegin |

| The beginning of the range to be scheduled. More... | |

| MachineBasicBlock::iterator | RegionEnd |

| The end of the range to be scheduled. More... | |

| unsigned | NumRegionInstrs |

| Instructions in this region (distance(RegionBegin, RegionEnd)). More... | |

| DenseMap< MachineInstr *, SUnit * > | MISUnitMap |

| VReg2UseMap | VRegUses |

| Reg2SUnitsMap | Defs |

| Reg2SUnitsMap | Uses |

| VReg2SUnitMap | VRegDefs |

| Track the last instruction in this region defining each virtual register. More... | |

| std::vector< SUnit * > | PendingLoads |

| DbgValueVector | DbgValues |

| MachineInstr * | FirstDbgValue |

Definition at line 106 of file DFAPacketizer.cpp.

| DefaultVLIWScheduler::DefaultVLIWScheduler | ( | MachineFunction & | MF, |

| MachineLoopInfo & | MLI, | ||

| MachineDominatorTree & | MDT, | ||

| bool | IsPostRA | ||

| ) |

Definition at line 115 of file DFAPacketizer.cpp.

References llvm::ScheduleDAGInstrs::CanHandleTerminators.

|

virtual |

schedule - Order nodes according to selected style, filling in the Sequence member.

Typically, a scheduling algorithm will implement schedule() without overriding enterRegion() or exitRegion().

Implements llvm::ScheduleDAGInstrs.

Definition at line 122 of file DFAPacketizer.cpp.

References llvm::ScheduleDAGInstrs::buildSchedGraph().

Referenced by llvm::VLIWPacketizerList::PacketizeMIs().