LLVM API Documentation

#include <MipsSEInstrInfo.h>

Additional Inherited Members | |

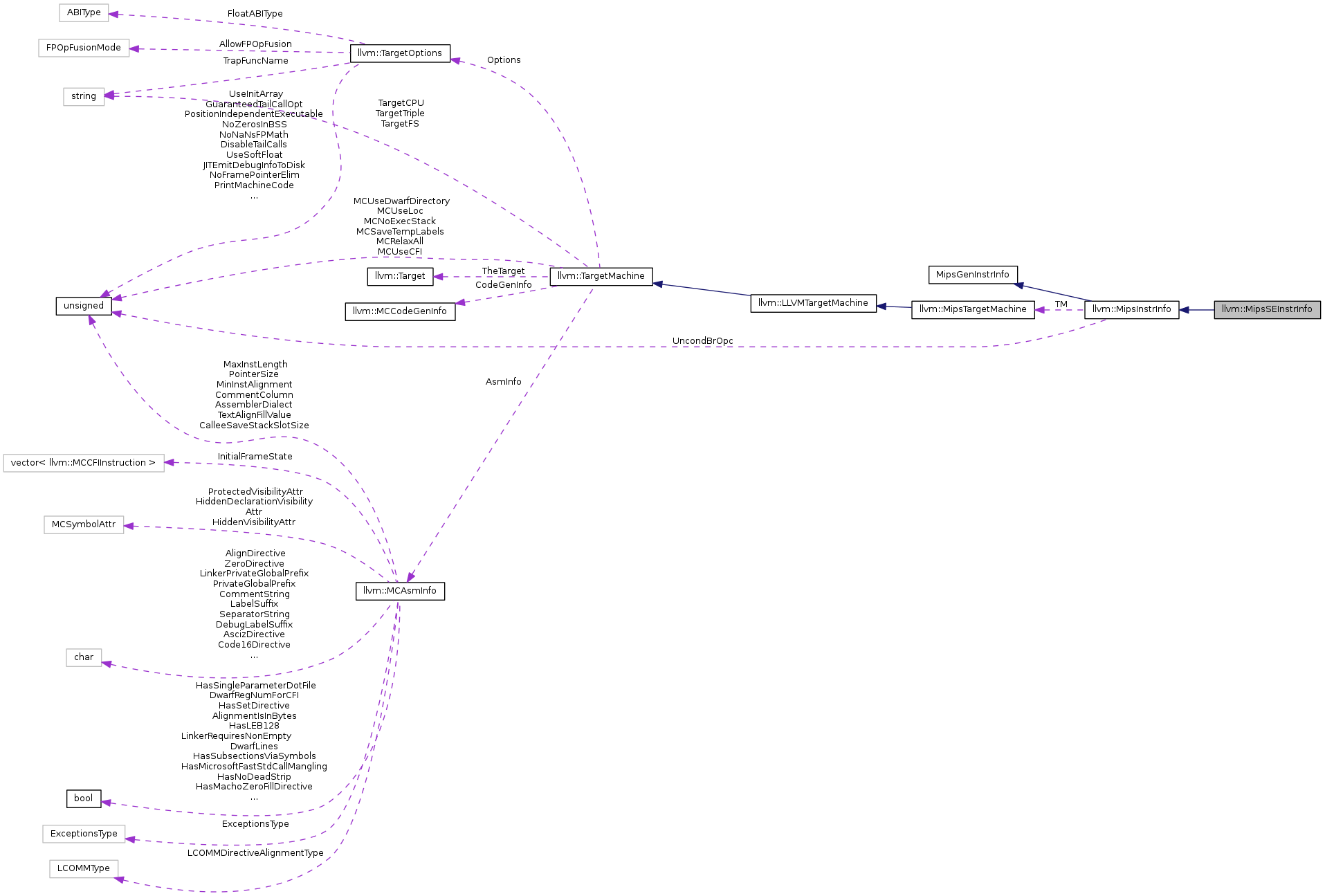

Public Types inherited from llvm::MipsInstrInfo Public Types inherited from llvm::MipsInstrInfo | |

| enum | BranchType { BT_None, BT_NoBranch, BT_Uncond, BT_Cond, BT_CondUncond, BT_Indirect } |

Static Public Member Functions inherited from llvm::MipsInstrInfo Static Public Member Functions inherited from llvm::MipsInstrInfo | |

| static const MipsInstrInfo * | create (MipsTargetMachine &TM) |

Protected Member Functions inherited from llvm::MipsInstrInfo Protected Member Functions inherited from llvm::MipsInstrInfo | |

| bool | isZeroImm (const MachineOperand &op) const |

| MachineMemOperand * | GetMemOperand (MachineBasicBlock &MBB, int FI, unsigned Flag) const |

Protected Attributes inherited from llvm::MipsInstrInfo Protected Attributes inherited from llvm::MipsInstrInfo | |

| MipsTargetMachine & | TM |

| unsigned | UncondBrOpc |

Definition at line 22 of file MipsSEInstrInfo.h.

|

explicit |

Definition at line 27 of file MipsSEInstrInfo.cpp.

| void MipsSEInstrInfo::adjustStackPtr | ( | unsigned | SP, |

| int64_t | Amount, | ||

| MachineBasicBlock & | MBB, | ||

| MachineBasicBlock::iterator | I | ||

| ) | const |

Adjust SP by Amount bytes.

Definition at line 350 of file MipsSEInstrInfo.cpp.

References llvm::MachineInstrBuilder::addImm(), llvm::MachineInstrBuilder::addReg(), llvm::BuildMI(), llvm::MachineBasicBlock::end(), llvm::TargetMachine::getSubtarget(), llvm::MipsSubtarget::isABI_N64(), llvm::isInt< 16 >(), llvm::RegState::Kill, loadImmediate(), and llvm::MipsInstrInfo::TM.

Referenced by llvm::MipsSEFrameLowering::eliminateCallFramePseudoInstr().

|

virtual |

Definition at line 82 of file MipsSEInstrInfo.cpp.

References llvm::MachineInstrBuilder::addImm(), llvm::MachineInstrBuilder::addReg(), llvm::BuildMI(), llvm::RegState::Define, llvm::getKillRegState(), llvm::RegState::Implicit, llvm::RegState::ImplicitDefine, llvm::MipsISD::MFHI, and llvm::MipsISD::MFLO.

|

virtual |

Definition at line 260 of file MipsSEInstrInfo.cpp.

References llvm::MipsISD::BuildPairF64, llvm::MachineBasicBlock::erase(), llvm::MipsISD::ExtractElementF64, llvm::MachineBasicBlock::getParent(), llvm::MipsISD::MFHI, and llvm::MipsISD::MFLO.

getOppositeBranchOpc - Return the inverse of the specified opcode, e.g. turning BEQ to BNE.

Implements llvm::MipsInstrInfo.

Definition at line 329 of file MipsSEInstrInfo.cpp.

References llvm_unreachable.

|

virtual |

getRegisterInfo - TargetInstrInfo is a superset of MRegister info. As such, whenever a client has an instance of instruction info, it should always be able to get register info as well (through this method).

Implements llvm::MipsInstrInfo.

Definition at line 33 of file MipsSEInstrInfo.cpp.

|

virtual |

isLoadFromStackSlot - If the specified machine instruction is a direct load from a stack slot, return the virtual or physical register number of the destination along with the FrameIndex of the loaded stack slot. If not, return 0. This predicate must return 0 if the instruction has any side effects other than loading from the stack slot.

Definition at line 43 of file MipsSEInstrInfo.cpp.

References llvm::MachineOperand::getIndex(), llvm::MachineInstr::getOpcode(), llvm::MachineInstr::getOperand(), llvm::MachineOperand::getReg(), llvm::MachineOperand::isFI(), llvm::MachineOperand::isImm(), llvm::MipsInstrInfo::isZeroImm(), and llvm::A64DB::LD.

|

virtual |

isStoreToStackSlot - If the specified machine instruction is a direct store to a stack slot, return the virtual or physical register number of the source reg along with the FrameIndex of the loaded stack slot. If not, return 0. This predicate must return 0 if the instruction has any side effects other than storing to the stack slot.

Definition at line 66 of file MipsSEInstrInfo.cpp.

References llvm::MachineOperand::getIndex(), llvm::MachineInstr::getOpcode(), llvm::MachineInstr::getOperand(), llvm::MachineOperand::getReg(), llvm::MachineOperand::isFI(), llvm::MachineOperand::isImm(), and llvm::MipsInstrInfo::isZeroImm().

| unsigned MipsSEInstrInfo::loadImmediate | ( | int64_t | Imm, |

| MachineBasicBlock & | MBB, | ||

| MachineBasicBlock::iterator | II, | ||

| DebugLoc | DL, | ||

| unsigned * | NewImm | ||

| ) | const |

Emit a series of instructions to load an immediate. If NewImm is a non-NULL parameter, the last instruction is not emitted, but instead its immediate operand is returned in NewImm.

This function generates the sequence of instructions needed to get the result of adding register REG and immediate IMM.

Definition at line 369 of file MipsSEInstrInfo.cpp.

References llvm::MachineInstrBuilder::addImm(), llvm::MachineInstrBuilder::addReg(), llvm::MipsAnalyzeImmediate::Analyze(), llvm::SmallVectorTemplateCommon< T, typename >::begin(), llvm::BuildMI(), llvm::SmallVectorTemplateCommon< T, typename >::end(), llvm::MachineBasicBlock::getParent(), llvm::MachineFunction::getRegInfo(), llvm::TargetMachine::getSubtarget(), llvm::MipsSubtarget::isABI_N64(), llvm::RegState::Kill, llvm::SmallVectorTemplateCommon< T, typename >::size(), and llvm::MipsInstrInfo::TM.

Referenced by adjustStackPtr().

|

virtual |

Implements llvm::MipsInstrInfo.

Definition at line 220 of file MipsSEInstrInfo.cpp.

References llvm::MachineInstrBuilder::addFrameIndex(), llvm::MachineInstrBuilder::addImm(), llvm::MachineInstrBuilder::addMemOperand(), llvm::BuildMI(), llvm::MachineBasicBlock::end(), llvm::MipsInstrInfo::GetMemOperand(), llvm::TargetRegisterClass::hasType(), llvm::A64DB::LD, llvm::MachineMemOperand::MOLoad, llvm::MVT::v16i8, llvm::MVT::v2f64, llvm::MVT::v2i64, llvm::MVT::v4f32, llvm::MVT::v4i32, llvm::MVT::v8f16, and llvm::MVT::v8i16.

|

virtual |

Implements llvm::MipsInstrInfo.

Definition at line 177 of file MipsSEInstrInfo.cpp.

References llvm::MachineInstrBuilder::addFrameIndex(), llvm::MachineInstrBuilder::addImm(), llvm::MachineInstrBuilder::addMemOperand(), llvm::MachineInstrBuilder::addReg(), llvm::BuildMI(), llvm::MachineBasicBlock::end(), llvm::getKillRegState(), llvm::MipsInstrInfo::GetMemOperand(), llvm::TargetRegisterClass::hasType(), llvm::MachineMemOperand::MOStore, llvm::MVT::v16i8, llvm::MVT::v2f64, llvm::MVT::v2i64, llvm::MVT::v4f32, llvm::MVT::v4i32, llvm::MVT::v8f16, and llvm::MVT::v8i16.