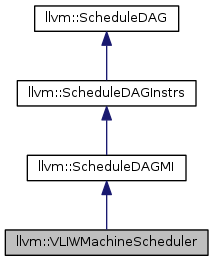

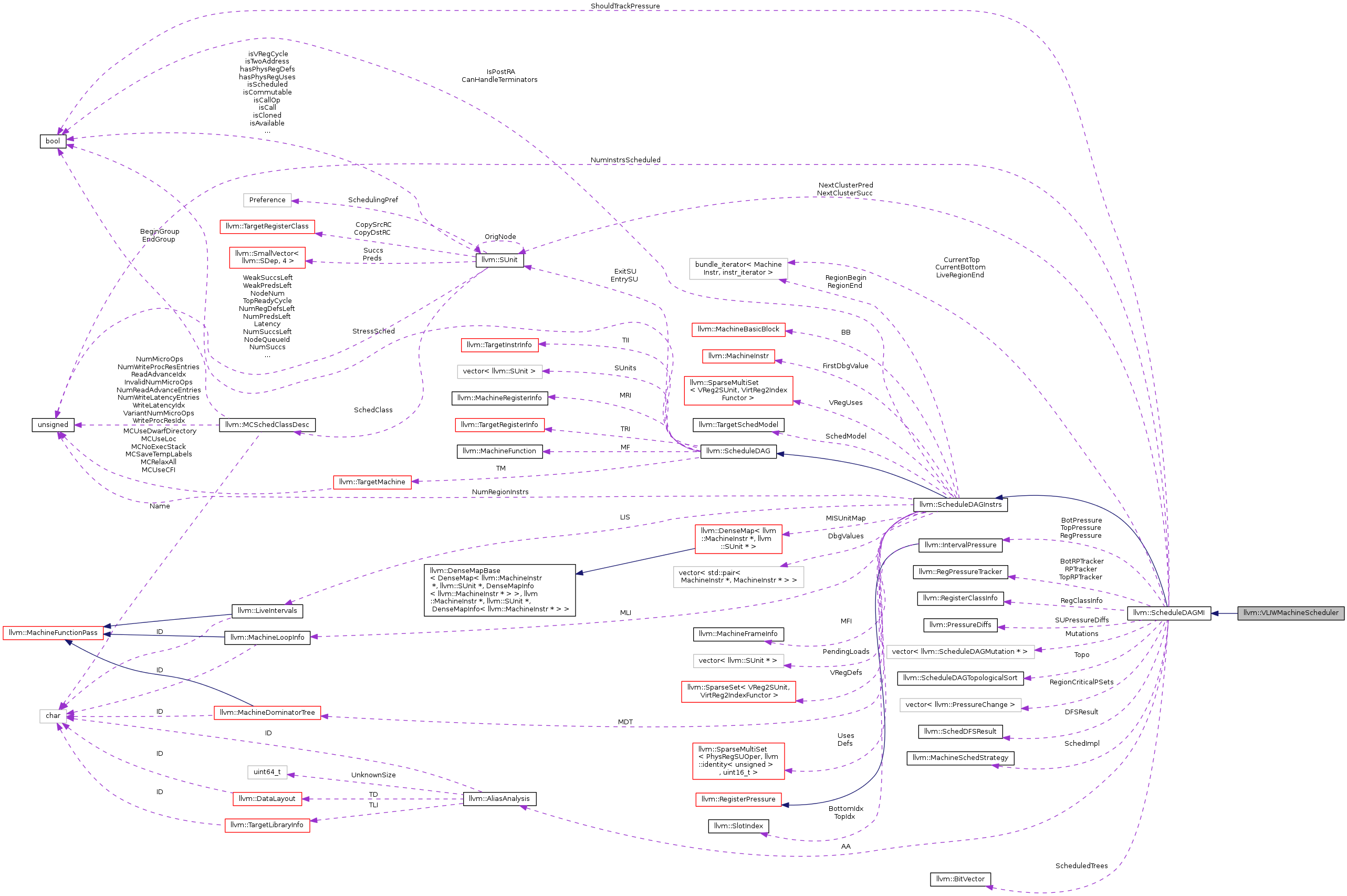

LLVM API Documentation

#include <HexagonMachineScheduler.h>

Public Member Functions | |

| VLIWMachineScheduler (MachineSchedContext *C, MachineSchedStrategy *S) | |

| virtual void | schedule () |

| void | postprocessDAG () |

| Perform platform specific DAG postprocessing. More... | |

Public Member Functions inherited from llvm::ScheduleDAGMI Public Member Functions inherited from llvm::ScheduleDAGMI | |

| ScheduleDAGMI (MachineSchedContext *C, MachineSchedStrategy *S) | |

| virtual | ~ScheduleDAGMI () |

| bool | isTrackingPressure () const |

| Return true if register pressure tracking is enabled. More... | |

| void | addMutation (ScheduleDAGMutation *Mutation) |

| bool | canAddEdge (SUnit *SuccSU, SUnit *PredSU) |

| True if an edge can be added from PredSU to SuccSU without creating a cycle. More... | |

| bool | addEdge (SUnit *SuccSU, const SDep &PredDep) |

| Add a DAG edge to the given SU with the given predecessor dependence data. More... | |

| MachineBasicBlock::iterator | top () const |

| MachineBasicBlock::iterator | bottom () const |

| void | enterRegion (MachineBasicBlock *bb, MachineBasicBlock::iterator begin, MachineBasicBlock::iterator end, unsigned regioninstrs) LLVM_OVERRIDE |

| void | moveInstruction (MachineInstr *MI, MachineBasicBlock::iterator InsertPos) |

| const IntervalPressure & | getTopPressure () const |

| Get current register pressure for the top scheduled instructions. More... | |

| const RegPressureTracker & | getTopRPTracker () const |

| const IntervalPressure & | getBotPressure () const |

| Get current register pressure for the bottom scheduled instructions. More... | |

| const RegPressureTracker & | getBotRPTracker () const |

| const IntervalPressure & | getRegPressure () const |

| Get register pressure for the entire scheduling region before scheduling. More... | |

| const std::vector < PressureChange > & | getRegionCriticalPSets () const |

| PressureDiff & | getPressureDiff (const SUnit *SU) |

| const SUnit * | getNextClusterPred () const |

| const SUnit * | getNextClusterSucc () const |

| void | computeDFSResult () |

| const SchedDFSResult * | getDFSResult () const |

| Return a non-null DFS result if the scheduling strategy initialized it. More... | |

| BitVector & | getScheduledTrees () |

| unsigned | computeCyclicCriticalPath () |

| Compute the cyclic critical path through the DAG. More... | |

| void | viewGraph (const Twine &Name, const Twine &Title) LLVM_OVERRIDE |

| void | viewGraph () LLVM_OVERRIDE |

| Out-of-line implementation with no arguments is handy for gdb. More... | |

Public Member Functions inherited from llvm::ScheduleDAGInstrs Public Member Functions inherited from llvm::ScheduleDAGInstrs | |

| ScheduleDAGInstrs (MachineFunction &mf, const MachineLoopInfo &mli, const MachineDominatorTree &mdt, bool IsPostRAFlag, LiveIntervals *LIS=0) | |

| virtual | ~ScheduleDAGInstrs () |

| LiveIntervals * | getLIS () const |

| Expose LiveIntervals for use in DAG mutators and such. More... | |

| const TargetSchedModel * | getSchedModel () const |

| Get the machine model for instruction scheduling. More... | |

| const MCSchedClassDesc * | getSchedClass (SUnit *SU) const |

| Resolve and cache a resolved scheduling class for an SUnit. More... | |

| MachineBasicBlock::iterator | begin () const |

| begin - Return an iterator to the top of the current scheduling region. More... | |

| MachineBasicBlock::iterator | end () const |

| end - Return an iterator to the bottom of the current scheduling region. More... | |

| SUnit * | newSUnit (MachineInstr *MI) |

| newSUnit - Creates a new SUnit and return a ptr to it. More... | |

| SUnit * | getSUnit (MachineInstr *MI) const |

| getSUnit - Return an existing SUnit for this MI, or NULL. More... | |

| virtual void | startBlock (MachineBasicBlock *BB) |

| startBlock - Prepare to perform scheduling in the given block. More... | |

| virtual void | finishBlock () |

| finishBlock - Clean up after scheduling in the given block. More... | |

| virtual void | exitRegion () |

| Notify that the scheduler has finished scheduling the current region. More... | |

| void | buildSchedGraph (AliasAnalysis *AA, RegPressureTracker *RPTracker=0, PressureDiffs *PDiffs=0) |

| void | addSchedBarrierDeps () |

| virtual void | finalizeSchedule () |

| virtual void | dumpNode (const SUnit *SU) const |

| virtual std::string | getGraphNodeLabel (const SUnit *SU) const |

| Return a label for a DAG node that points to an instruction. More... | |

| virtual std::string | getDAGName () const |

| Return a label for the region of code covered by the DAG. More... | |

Public Member Functions inherited from llvm::ScheduleDAG Public Member Functions inherited from llvm::ScheduleDAG | |

| ScheduleDAG (MachineFunction &mf) | |

| virtual | ~ScheduleDAG () |

| void | clearDAG () |

| clearDAG - clear the DAG state (between regions). More... | |

| const MCInstrDesc * | getInstrDesc (const SUnit *SU) const |

| virtual void | addCustomGraphFeatures (GraphWriter< ScheduleDAG * > &) const |

| unsigned | VerifyScheduledDAG (bool isBottomUp) |

Additional Inherited Members | |

Public Attributes inherited from llvm::ScheduleDAG Public Attributes inherited from llvm::ScheduleDAG | |

| const TargetMachine & | TM |

| const TargetInstrInfo * | TII |

| const TargetRegisterInfo * | TRI |

| MachineFunction & | MF |

| MachineRegisterInfo & | MRI |

| std::vector< SUnit > | SUnits |

| SUnit | EntrySU |

| SUnit | ExitSU |

| bool | StressSched |

Protected Types inherited from llvm::ScheduleDAGInstrs Protected Types inherited from llvm::ScheduleDAGInstrs | |

| typedef std::vector< std::pair < MachineInstr *, MachineInstr * > > | DbgValueVector |

Protected Member Functions inherited from llvm::ScheduleDAGMI Protected Member Functions inherited from llvm::ScheduleDAGMI | |

| void | buildDAGWithRegPressure () |

| Build the DAG and setup three register pressure trackers. More... | |

| void | postprocessDAG () |

| Apply each ScheduleDAGMutation step in order. More... | |

| void | initQueues (ArrayRef< SUnit * > TopRoots, ArrayRef< SUnit * > BotRoots) |

| Release ExitSU predecessors and setup scheduler queues. More... | |

| void | scheduleMI (SUnit *SU, bool IsTopNode) |

| Move an instruction and update register pressure. More... | |

| void | updateQueues (SUnit *SU, bool IsTopNode) |

| Update scheduler DAG and queues after scheduling an instruction. More... | |

| void | placeDebugValues () |

| Reinsert debug_values recorded in ScheduleDAGInstrs::DbgValues. More... | |

| void | dumpSchedule () const |

| dump the scheduled Sequence. More... | |

| void | initRegPressure () |

| void | updatePressureDiffs (ArrayRef< unsigned > LiveUses) |

| void | updateScheduledPressure (const SUnit *SU, const std::vector< unsigned > &NewMaxPressure) |

| bool | checkSchedLimit () |

| void | findRootsAndBiasEdges (SmallVectorImpl< SUnit * > &TopRoots, SmallVectorImpl< SUnit * > &BotRoots) |

| void | releaseSucc (SUnit *SU, SDep *SuccEdge) |

| void | releaseSuccessors (SUnit *SU) |

| releaseSuccessors - Call releaseSucc on each of SU's successors. More... | |

| void | releasePred (SUnit *SU, SDep *PredEdge) |

| void | releasePredecessors (SUnit *SU) |

| releasePredecessors - Call releasePred on each of SU's predecessors. More... | |

Protected Member Functions inherited from llvm::ScheduleDAGInstrs Protected Member Functions inherited from llvm::ScheduleDAGInstrs | |

| void | initSUnits () |

| void | addPhysRegDataDeps (SUnit *SU, unsigned OperIdx) |

| void | addPhysRegDeps (SUnit *SU, unsigned OperIdx) |

| void | addVRegDefDeps (SUnit *SU, unsigned OperIdx) |

| void | addVRegUseDeps (SUnit *SU, unsigned OperIdx) |

Protected Attributes inherited from llvm::ScheduleDAGMI Protected Attributes inherited from llvm::ScheduleDAGMI | |

| AliasAnalysis * | AA |

| RegisterClassInfo * | RegClassInfo |

| MachineSchedStrategy * | SchedImpl |

| SchedDFSResult * | DFSResult |

| BitVector | ScheduledTrees |

| ScheduleDAGTopologicalSort | Topo |

| std::vector < ScheduleDAGMutation * > | Mutations |

| Ordered list of DAG postprocessing steps. More... | |

| MachineBasicBlock::iterator | LiveRegionEnd |

| PressureDiffs | SUPressureDiffs |

| bool | ShouldTrackPressure |

| Register pressure in this region computed by initRegPressure. More... | |

| IntervalPressure | RegPressure |

| RegPressureTracker | RPTracker |

| std::vector< PressureChange > | RegionCriticalPSets |

| MachineBasicBlock::iterator | CurrentTop |

| The top of the unscheduled zone. More... | |

| IntervalPressure | TopPressure |

| RegPressureTracker | TopRPTracker |

| MachineBasicBlock::iterator | CurrentBottom |

| The bottom of the unscheduled zone. More... | |

| IntervalPressure | BotPressure |

| RegPressureTracker | BotRPTracker |

| const SUnit * | NextClusterPred |

| Record the next node in a scheduled cluster. More... | |

| const SUnit * | NextClusterSucc |

| unsigned | NumInstrsScheduled |

Protected Attributes inherited from llvm::ScheduleDAGInstrs Protected Attributes inherited from llvm::ScheduleDAGInstrs | |

| const MachineLoopInfo & | MLI |

| const MachineDominatorTree & | MDT |

| const MachineFrameInfo * | MFI |

| LiveIntervals * | LIS |

| Live Intervals provides reaching defs in preRA scheduling. More... | |

| TargetSchedModel | SchedModel |

| TargetSchedModel provides an interface to the machine model. More... | |

| bool | IsPostRA |

| isPostRA flag indicates vregs cannot be present. More... | |

| bool | CanHandleTerminators |

| MachineBasicBlock * | BB |

| The block in which to insert instructions. More... | |

| MachineBasicBlock::iterator | RegionBegin |

| The beginning of the range to be scheduled. More... | |

| MachineBasicBlock::iterator | RegionEnd |

| The end of the range to be scheduled. More... | |

| unsigned | NumRegionInstrs |

| Instructions in this region (distance(RegionBegin, RegionEnd)). More... | |

| DenseMap< MachineInstr *, SUnit * > | MISUnitMap |

| VReg2UseMap | VRegUses |

| Reg2SUnitsMap | Defs |

| Reg2SUnitsMap | Uses |

| VReg2SUnitMap | VRegDefs |

| Track the last instruction in this region defining each virtual register. More... | |

| std::vector< SUnit * > | PendingLoads |

| DbgValueVector | DbgValues |

| MachineInstr * | FirstDbgValue |

Extend the standard ScheduleDAGMI to provide more context and override the top-level schedule() driver.

Definition at line 95 of file HexagonMachineScheduler.h.

|

inline |

Definition at line 97 of file HexagonMachineScheduler.h.

| void VLIWMachineScheduler::postprocessDAG | ( | ) |

Perform platform specific DAG postprocessing.

Platform specific modifications to DAG.

Definition at line 24 of file HexagonMachineScheduler.cpp.

References llvm::SDep::Barrier, and llvm::ScheduleDAG::SUnits.

Referenced by schedule().

|

virtual |

Schedule - This is called back from ScheduleDAGInstrs::Run() when it's time to do some work.

schedule - Called back from MachineScheduler::runOnMachineFunction after setting up the current scheduling region. [RegionBegin, RegionEnd) only includes instructions that have DAG nodes, not scheduling boundaries.

Reimplemented from llvm::ScheduleDAGMI.

Definition at line 143 of file HexagonMachineScheduler.cpp.

References llvm::ScheduleDAGInstrs::BB, llvm::ScheduleDAGMI::buildDAGWithRegPressure(), llvm::ScheduleDAGMI::checkSchedLimit(), llvm::ScheduleDAGMI::CurrentBottom, llvm::ScheduleDAGMI::CurrentTop, llvm::dbgs(), DEBUG, llvm::ScheduleDAGMI::findRootsAndBiasEdges(), llvm::MachineFunction::getFunction(), llvm::MachineLoopInfo::getLoopDepth(), llvm::MachineBasicBlock::getName(), llvm::Value::getName(), llvm::MachineBasicBlock::getNumber(), llvm::MachineBasicBlock::getParent(), llvm::MachineSchedStrategy::initialize(), llvm::ScheduleDAGMI::initQueues(), llvm::ScheduleDAGInstrs::MLI, llvm::MachineSchedStrategy::pickNode(), llvm::ScheduleDAGMI::placeDebugValues(), postprocessDAG(), llvm::ScheduleDAGMI::SchedImpl, llvm::ScheduleDAGMI::scheduleMI(), llvm::ScheduleDAG::SUnits, and llvm::ScheduleDAGMI::updateQueues().