LLVM API Documentation

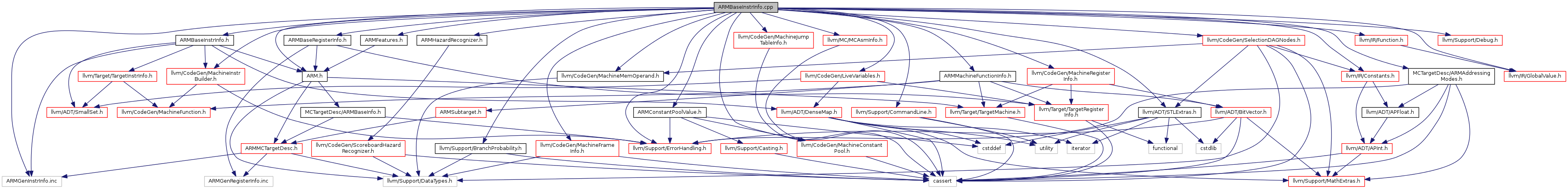

#include "ARM.h"#include "ARMBaseInstrInfo.h"#include "ARMBaseRegisterInfo.h"#include "ARMConstantPoolValue.h"#include "ARMFeatures.h"#include "ARMHazardRecognizer.h"#include "ARMMachineFunctionInfo.h"#include "MCTargetDesc/ARMAddressingModes.h"#include "llvm/ADT/STLExtras.h"#include "llvm/CodeGen/LiveVariables.h"#include "llvm/CodeGen/MachineConstantPool.h"#include "llvm/CodeGen/MachineFrameInfo.h"#include "llvm/CodeGen/MachineInstrBuilder.h"#include "llvm/CodeGen/MachineJumpTableInfo.h"#include "llvm/CodeGen/MachineMemOperand.h"#include "llvm/CodeGen/MachineRegisterInfo.h"#include "llvm/CodeGen/SelectionDAGNodes.h"#include "llvm/IR/Constants.h"#include "llvm/IR/Function.h"#include "llvm/IR/GlobalValue.h"#include "llvm/MC/MCAsmInfo.h"#include "llvm/Support/BranchProbability.h"#include "llvm/Support/CommandLine.h"#include "llvm/Support/Debug.h"#include "llvm/Support/ErrorHandling.h"#include "ARMGenInstrInfo.inc"

Go to the source code of this file.

Classes | |

| struct | ARM_MLxEntry |

| ARM_MLxEntry - Record information about MLA / MLS instructions. More... | |

| struct | AddSubFlagsOpcodePair |

Macros | |

| #define | GET_INSTRINFO_CTOR_DTOR |

Enumerations | |

| enum | ARMExeDomain { ExeGeneric = 0, ExeVFP = 1, ExeNEON = 2 } |

Variables | |

| static cl::opt< bool > | EnableARM3Addr ("enable-arm-3-addr-conv", cl::Hidden, cl::desc("Enable ARM 2-addr to 3-addr conv")) |

| static cl::opt< bool > | WidenVMOVS ("widen-vmovs", cl::Hidden, cl::init(true), cl::desc("Widen ARM vmovs to vmovd when possible")) |

| static cl::opt< unsigned > | SwiftPartialUpdateClearance ("swift-partial-update-clearance", cl::Hidden, cl::init(12), cl::desc("Clearance before partial register updates")) |

| static const ARM_MLxEntry | ARM_MLxTable [] |

| static const AddSubFlagsOpcodePair | AddSubFlagsOpcodeMap [] |

| #define GET_INSTRINFO_CTOR_DTOR |

Definition at line 40 of file ARMBaseInstrInfo.cpp.

| enum ARMExeDomain |

| Enumerator | |

|---|---|

| ExeGeneric | |

| ExeVFP | |

| ExeNEON | |

Definition at line 3894 of file ARMBaseInstrInfo.cpp.

|

static |

Return the number of cycles to add to (or subtract from) the static itinerary based on the def opcode and alignment. The caller will ensure that adjusted latency is at least one cycle.

Definition at line 3250 of file ARMBaseInstrInfo.cpp.

References llvm::ARM_AM::getAM2Offset(), llvm::ARM_AM::getAM2Op(), llvm::ARM_AM::getAM2ShiftOpc(), llvm::MachineOperand::getImm(), llvm::MCInstrDesc::getOpcode(), llvm::MachineInstr::getOperand(), llvm::ARMSubtarget::isCortexA8(), llvm::ARMSubtarget::isLikeA9(), llvm::ARMSubtarget::isSwift(), llvm::ARM_AM::lsl, llvm::ARM_AM::lsr, and llvm::ARM_AM::sub.

Referenced by llvm::ARMBaseInstrInfo::getOperandLatency().

|

static |

Identify instructions that can be folded into a MOVCC instruction, and return the defining instruction.

Definition at line 1668 of file ARMBaseInstrInfo.cpp.

References llvm::MachineInstr::getNumOperands(), llvm::MachineInstr::getOperand(), llvm::MachineOperand::getReg(), llvm::MachineRegisterInfo::getVRegDef(), llvm::MachineRegisterInfo::hasOneNonDBGUse(), llvm::MachineOperand::isCPI(), llvm::MachineOperand::isDead(), llvm::MachineOperand::isDef(), llvm::MachineOperand::isFI(), llvm::MachineOperand::isJTI(), llvm::TargetRegisterInfo::isPhysicalRegister(), llvm::MachineInstr::isPredicable(), llvm::MachineOperand::isReg(), llvm::MachineInstr::isSafeToMove(), llvm::MachineOperand::isTied(), llvm::TargetRegisterInfo::isVirtualRegister(), and llvm::A64CC::MI.

Referenced by llvm::ARMBaseInstrInfo::optimizeSelect().

|

static |

Create a copy of a const pool value. Update CPI to the new index and return the label UID.

Definition at line 1234 of file ARMBaseInstrInfo.cpp.

References llvm::ARMCP::CPBlockAddress, llvm::ARMCP::CPLSDA, llvm::ARMCP::CPValue, llvm::ARMConstantPoolConstant::Create(), llvm::ARMFunctionInfo::createPICLabelUId(), llvm::MachineFunction::getConstantPool(), llvm::MachineConstantPool::getConstantPoolIndex(), llvm::MachineConstantPool::getConstants(), llvm::Function::getContext(), llvm::MachineFunction::getFunction(), llvm::MachineFunction::getInfo(), and llvm_unreachable.

Referenced by llvm::ARMBaseInstrInfo::duplicate(), and llvm::ARMBaseInstrInfo::reMaterialize().

|

static |

Definition at line 3194 of file ARMBaseInstrInfo.cpp.

References I, llvm::A64CC::MI, and llvm::prior().

Referenced by llvm::ARMBaseInstrInfo::getOperandLatency().

|

static |

Definition at line 3218 of file ARMBaseInstrInfo.cpp.

References llvm::MachineInstr::getParent(), llvm::MachineBasicBlock::instr_end(), and llvm::A64CC::MI.

Referenced by llvm::ARMBaseInstrInfo::getOperandLatency().

|

static |

Definition at line 3934 of file ARMBaseInstrInfo.cpp.

References llvm::TargetRegisterInfo::getMatchingSuperReg().

Referenced by llvm::ARMBaseInstrInfo::setExecutionDomain().

|

static |

getImplicitSPRUseForDPRUse - Given a use of a DPR register and lane, set ImplicitSReg to a register number that must be marked as implicit-use or zero if no register needs to be defined as implicit-use.

If the function cannot determine if an SPR should be marked implicit use or not, it returns false.

This function handles cases where an instruction is being modified from taking an SPR to a DPR[Lane]. A use of the DPR is being added, which may conflict with an earlier def of an SPR corresponding to DPRLane^1.

If the other SPR is defined, an implicit-use of it should be added. Else, (including the case where the DPR itself is defined), it should not.

Definition at line 3964 of file ARMBaseInstrInfo.cpp.

References llvm::MachineBasicBlock::computeRegisterLiveness(), llvm::MachineInstr::definesRegister(), llvm::MachineInstr::getParent(), llvm::MCRegisterInfo::getSubReg(), llvm::MachineBasicBlock::LQR_Live, llvm::MachineBasicBlock::LQR_Unknown, and llvm::MachineInstr::readsRegister().

Referenced by llvm::ARMBaseInstrInfo::setExecutionDomain().

|

static |

FIXME: Works around a gcc miscompilation with -fstrict-aliasing.

Definition at line 542 of file ARMBaseInstrInfo.cpp.

Referenced by llvm::ARMBaseInstrInfo::GetInstSizeInBytes().

|

static |

Definition at line 2539 of file ARMBaseInstrInfo.cpp.

References llvm::ARM_AM::getAM2Offset(), llvm::ARM_AM::getAM2Op(), llvm::ARM_AM::getAM2ShiftOpc(), llvm::ARM_AM::getAM3Op(), llvm::MachineInstr::getDesc(), llvm::MachineOperand::getImm(), llvm::InstrItineraryData::getNumMicroOps(), llvm::MachineInstr::getOpcode(), llvm::MachineInstr::getOperand(), llvm::MachineOperand::getReg(), llvm::MCInstrDesc::getSchedClass(), llvm::ARM_AM::lsl, and llvm::ARM_AM::sub.

Referenced by llvm::ARMBaseInstrInfo::getNumMicroOps().

|

inlinestatic |

getSwappedCondition - assume the flags are set by MI(a,b), return the condition code if we modify the instructions such that flags are set by MI(b,a).

Definition at line 2164 of file ARMBaseInstrInfo.cpp.

References llvm::ARMCC::AL, llvm::ARMCC::EQ, llvm::ARMCC::GE, llvm::ARMCC::GT, llvm::ARMCC::HI, llvm::ARMCC::HS, llvm::ARMCC::LE, llvm::ARMCC::LO, llvm::ARMCC::LS, llvm::ARMCC::LT, and llvm::ARMCC::NE.

Referenced by llvm::ARMBaseInstrInfo::optimizeCompareInstr().

|

inlinestatic |

isRedundantFlagInstr - check whether the first instruction, whose only purpose is to update flags, can be made redundant. CMPrr can be made redundant by SUBrr if the operands are the same. CMPri can be made redundant by SUBri if the operands are the same. This function can be extended later on.

Definition at line 2185 of file ARMBaseInstrInfo.cpp.

References llvm::MachineOperand::getImm(), llvm::MachineInstr::getOpcode(), llvm::MachineInstr::getOperand(), and llvm::MachineOperand::getReg().

Referenced by llvm::ARMBaseInstrInfo::optimizeCompareInstr().

|

static |

isSuitableForMask - Identify a suitable 'and' instruction that operates on the given source register and applies the same mask as a 'tst' instruction. Provide a limited look-through for copies. When successful, MI will hold the found instruction.

Definition at line 2136 of file ARMBaseInstrInfo.cpp.

References AND, llvm::TargetOpcode::COPY, llvm::MachineBasicBlock::end(), llvm::MachineOperand::getImm(), llvm::MachineInstr::getOpcode(), llvm::MachineInstr::getOperand(), llvm::MachineInstr::getParent(), llvm::MachineOperand::getReg(), llvm::A64CC::MI, and llvm::next().

Referenced by llvm::ARMBaseInstrInfo::optimizeCompareInstr().

|

static |

Definition at line 1790 of file ARMBaseInstrInfo.cpp.

Referenced by llvm::convertAddSubFlagsOpcode().

|

static |

Definition at line 67 of file ARMBaseInstrInfo.cpp.

Referenced by llvm::ARMBaseInstrInfo::ARMBaseInstrInfo(), and llvm::ARMBaseInstrInfo::isFpMLxInstruction().

|

static |

Referenced by llvm::ARMBaseInstrInfo::convertToThreeAddress().

|

static |

Referenced by llvm::ARMBaseInstrInfo::getPartialRegUpdateClearance().

|

static |

Referenced by llvm::ARMBaseInstrInfo::expandPostRAPseudo().