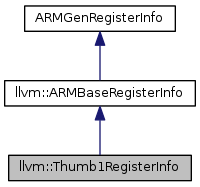

LLVM API Documentation

#include <Thumb1RegisterInfo.h>

Additional Inherited Members | |

Protected Member Functions inherited from llvm::ARMBaseRegisterInfo Protected Member Functions inherited from llvm::ARMBaseRegisterInfo | |

| ARMBaseRegisterInfo (const ARMSubtarget &STI) | |

| unsigned | getOpcode (int Op) const |

Protected Attributes inherited from llvm::ARMBaseRegisterInfo Protected Attributes inherited from llvm::ARMBaseRegisterInfo | |

| const ARMSubtarget & | STI |

| unsigned | FramePtr |

| FramePtr - ARM physical register used as frame ptr. More... | |

| unsigned | BasePtr |

Definition at line 26 of file Thumb1RegisterInfo.h.

| Thumb1RegisterInfo::Thumb1RegisterInfo | ( | const ARMSubtarget & | STI | ) |

Definition at line 43 of file Thumb1RegisterInfo.cpp.

|

virtual |

Reimplemented from llvm::ARMBaseRegisterInfo.

Definition at line 558 of file Thumb1RegisterInfo.cpp.

References llvm::AddDefaultPred(), llvm::ARMBaseRegisterInfo::BasePtr, llvm::MachineOperand::ChangeToImmediate(), llvm::MachineOperand::ChangeToRegister(), llvm::MachineRegisterInfo::createVirtualRegister(), emitLoadConstPool(), llvm::emitThumbRegPlusImmediate(), emitThumbRegPlusImmInReg(), llvm::MachineInstr::findFirstPredOperandIdx(), llvm::ISD::FrameIndex, llvm::MachineInstr::getDebugLoc(), llvm::MachineFunction::getFrameInfo(), llvm::TargetMachine::getFrameLowering(), llvm::ARMFunctionInfo::getFramePtrSpillOffset(), llvm::ARMBaseRegisterInfo::getFrameRegister(), llvm::MachineOperand::getIndex(), llvm::MachineFunction::getInfo(), llvm::TargetMachine::getInstrInfo(), llvm::MachineFrameInfo::getObjectOffset(), llvm::MachineInstr::getOpcode(), llvm::MachineInstr::getOperand(), llvm::MachineInstr::getParent(), llvm::MachineBasicBlock::getParent(), llvm::MachineOperand::getReg(), llvm::MachineFunction::getRegInfo(), llvm::MachineFrameInfo::getStackSize(), llvm::MachineFunction::getTarget(), llvm::ARMBaseRegisterInfo::hasBasePointer(), llvm::TargetFrameLowering::hasFP(), llvm::TargetFrameLowering::hasReservedCallFrame(), llvm::MachineFrameInfo::hasVarSizedObjects(), llvm::MachineInstr::isDebugValue(), llvm::MachineInstr::isPredicable(), llvm::RegScavenger::isScavengingFrameIndex(), llvm::ARMFunctionInfo::isThumbFunction(), llvm_unreachable, llvm::MachineInstr::mayLoad(), llvm::MachineInstr::mayStore(), llvm::A64CC::MI, removeOperands(), rewriteFrameIndex(), and llvm::MachineInstr::setDesc().

|

virtual |

emitLoadConstPool - Emits a load from constpool to materialize the specified immediate.

Reimplemented from llvm::ARMBaseRegisterInfo.

Definition at line 64 of file Thumb1RegisterInfo.cpp.

References llvm::MachineInstrBuilder::addImm(), llvm::MachineInstrBuilder::addReg(), llvm::BuildMI(), llvm::CallingConv::C, llvm::ISD::ConstantPool, llvm::MCInstrInfo::get(), llvm::ConstantInt::get(), llvm::MachineFunction::getConstantPool(), llvm::MachineConstantPool::getConstantPoolIndex(), llvm::Function::getContext(), llvm::getDefRegState(), llvm::MachineFunction::getFunction(), llvm::TargetMachine::getInstrInfo(), llvm::Type::getInt32Ty(), llvm::MachineBasicBlock::getParent(), llvm::MachineFunction::getTarget(), llvm::MachineInstrBuilder::setMIFlags(), and TII.

Referenced by eliminateFrameIndex().

| const TargetRegisterClass * Thumb1RegisterInfo::getLargestLegalSuperClass | ( | const TargetRegisterClass * | RC | ) | const |

Definition at line 48 of file Thumb1RegisterInfo.cpp.

References llvm::ARMBaseRegisterInfo::getLargestLegalSuperClass().

| const TargetRegisterClass * Thumb1RegisterInfo::getPointerRegClass | ( | const MachineFunction & | MF, |

| unsigned | Kind = 0 |

||

| ) | const |

Definition at line 56 of file Thumb1RegisterInfo.cpp.

| void Thumb1RegisterInfo::resolveFrameIndex | ( | MachineBasicBlock::iterator | I, |

| unsigned | BaseReg, | ||

| int64_t | Offset | ||

| ) | const |

Definition at line 488 of file Thumb1RegisterInfo.cpp.

References llvm::TargetMachine::getInstrInfo(), llvm::MachineInstr::getNumOperands(), llvm::MachineInstr::getOperand(), llvm::MachineInstr::getParent(), llvm::MachineBasicBlock::getParent(), llvm::MachineFunction::getTarget(), I, llvm::MachineOperand::isFI(), llvm::A64CC::MI, and rewriteFrameIndex().

| bool Thumb1RegisterInfo::rewriteFrameIndex | ( | MachineBasicBlock::iterator | II, |

| unsigned | FrameRegIdx, | ||

| unsigned | FrameReg, | ||

| int & | Offset, | ||

| const ARMBaseInstrInfo & | TII | ||

| ) | const |

Definition at line 346 of file Thumb1RegisterInfo.cpp.

References llvm::AddDefaultPred(), llvm::AddDefaultT1CC(), llvm::ARMII::AddrModeMask, llvm::ARMII::AddrModeT1_s, llvm::ARMCC::AL, calcNumMI(), llvm::MachineOperand::ChangeToImmediate(), llvm::MachineOperand::ChangeToRegister(), convertToNonSPOpcode(), emitThumbConstant(), llvm::emitThumbRegPlusImmediate(), llvm::MachineBasicBlock::erase(), llvm::MachineInstr::getDebugLoc(), llvm::MachineInstr::getDesc(), llvm::MachineOperand::getImm(), llvm::getInstrPredicate(), llvm::MachineInstr::getOpcode(), llvm::MachineInstr::getOperand(), llvm::MachineInstr::getParent(), llvm::MachineBasicBlock::getParent(), llvm::MachineOperand::getReg(), llvm_unreachable, llvm::A64CC::MI, llvm::next(), llvm::MachineInstr::RemoveOperand(), removeOperands(), llvm::MachineInstr::setDesc(), and llvm::MCInstrDesc::TSFlags.

Referenced by eliminateFrameIndex(), and resolveFrameIndex().

| bool Thumb1RegisterInfo::saveScavengerRegister | ( | MachineBasicBlock & | MBB, |

| MachineBasicBlock::iterator | I, | ||

| MachineBasicBlock::iterator & | UseMI, | ||

| const TargetRegisterClass * | RC, | ||

| unsigned | Reg | ||

| ) | const |

saveScavengerRegister - Spill the register so it can be used by the register scavenger. Return true.

Definition at line 509 of file Thumb1RegisterInfo.cpp.

References llvm::AddDefaultPred(), llvm::MachineInstrBuilder::addReg(), llvm::BuildMI(), llvm::MachineOperand::clobbersPhysReg(), llvm::RegState::Define, llvm::MCInstrInfo::get(), llvm::TargetMachine::getInstrInfo(), llvm::MachineBasicBlock::getParent(), llvm::MachineOperand::getReg(), llvm::MachineFunction::getTarget(), llvm::MachineOperand::isReg(), llvm::MachineOperand::isRegMask(), llvm::MachineOperand::isUndef(), llvm::TargetRegisterInfo::isVirtualRegister(), and llvm::RegState::Kill.