LLVM API Documentation

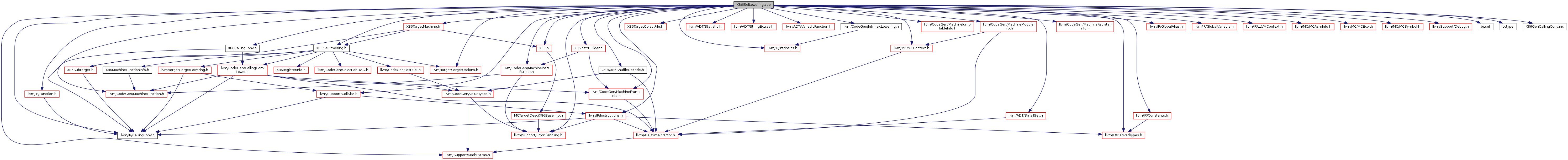

#include "X86ISelLowering.h"#include "Utils/X86ShuffleDecode.h"#include "X86.h"#include "X86CallingConv.h"#include "X86InstrBuilder.h"#include "X86TargetMachine.h"#include "X86TargetObjectFile.h"#include "llvm/ADT/SmallSet.h"#include "llvm/ADT/Statistic.h"#include "llvm/ADT/StringExtras.h"#include "llvm/ADT/VariadicFunction.h"#include "llvm/CodeGen/IntrinsicLowering.h"#include "llvm/CodeGen/MachineFrameInfo.h"#include "llvm/CodeGen/MachineFunction.h"#include "llvm/CodeGen/MachineInstrBuilder.h"#include "llvm/CodeGen/MachineJumpTableInfo.h"#include "llvm/CodeGen/MachineModuleInfo.h"#include "llvm/CodeGen/MachineRegisterInfo.h"#include "llvm/IR/CallingConv.h"#include "llvm/IR/Constants.h"#include "llvm/IR/DerivedTypes.h"#include "llvm/IR/Function.h"#include "llvm/IR/GlobalAlias.h"#include "llvm/IR/GlobalVariable.h"#include "llvm/IR/Instructions.h"#include "llvm/IR/Intrinsics.h"#include "llvm/IR/LLVMContext.h"#include "llvm/MC/MCAsmInfo.h"#include "llvm/MC/MCContext.h"#include "llvm/MC/MCExpr.h"#include "llvm/MC/MCSymbol.h"#include "llvm/Support/CallSite.h"#include "llvm/Support/Debug.h"#include "llvm/Support/ErrorHandling.h"#include "llvm/Support/MathExtras.h"#include "llvm/Target/TargetOptions.h"#include <bitset>#include <cctype>#include "X86GenCallingConv.inc"

Go to the source code of this file.

Macros | |

| #define | DEBUG_TYPE "x86-isel" |

Enumerations | |

| enum | StructReturnType { NotStructReturn, RegStructReturn, StackStructReturn } |

| #define DEBUG_TYPE "x86-isel" |

Definition at line 15 of file X86ISelLowering.cpp.

| enum StructReturnType |

CallIsStructReturn - Determines whether a call uses struct return semantics.

| Enumerator | |

|---|---|

| NotStructReturn | |

| RegStructReturn | |

| StackStructReturn | |

Definition at line 2037 of file X86ISelLowering.cpp.

|

static |

ArgsAreStructReturn - Determines whether a function uses struct return semantics.

Definition at line 2058 of file X86ISelLowering.cpp.

References llvm::SmallVectorBase::empty(), llvm::ISD::ArgFlagsTy::isInReg(), llvm::ISD::ArgFlagsTy::isSRet(), NotStructReturn, RegStructReturn, and StackStructReturn.

|

static |

Definition at line 5622 of file X86ISelLowering.cpp.

References llvm::ISD::EXTRACT_VECTOR_ELT, llvm::SelectionDAG::getIntPtrConstant(), llvm::SDValue::getNode(), llvm::SelectionDAG::getNode(), llvm::SDValue::getNumOperands(), llvm::SDValue::getOpcode(), llvm::SDValue::getOperand(), llvm::SDValue::getSimpleValueType(), llvm::SelectionDAG::getTargetLoweringInfo(), llvm::SelectionDAG::getUNDEF(), llvm::SDValue::getValueType(), llvm::SelectionDAG::getVectorShuffle(), llvm::ISD::INSERT_VECTOR_ELT, llvm::TargetLoweringBase::isOperationLegalOrCustom(), llvm::A64CC::NV, llvm::SmallVectorTemplateBase< T, isPodLike >::push_back(), llvm::SmallVectorTemplateCommon< T, typename >::size(), and llvm::ISD::UNDEF.

|

static |

Definition at line 2043 of file X86ISelLowering.cpp.

References llvm::SmallVectorBase::empty(), llvm::ISD::ArgFlagsTy::isInReg(), llvm::ISD::ArgFlagsTy::isSRet(), NotStructReturn, RegStructReturn, and StackStructReturn.

CanFoldXORWithAllOnes - Test whether the XOR operand is a AllOnes vector so it can be folded inside ANDNP.

Definition at line 17574 of file X86ISelLowering.cpp.

References llvm::ISD::BITCAST, llvm::SDValue::getNode(), llvm::SDValue::getOpcode(), llvm::SDNode::getOpcode(), llvm::SDValue::getOperand(), llvm::SDNode::getOperand(), llvm::SDNode::getValueType(), llvm::ISD::INSERT_SUBVECTOR, llvm::EVT::is256BitVector(), llvm::ISD::isBuildVectorAllOnes(), and llvm::ISD::UNDEF.

Referenced by PerformAndCombine().

|

static |

Definition at line 15235 of file X86ISelLowering.cpp.

References llvm::MachineInstr::definesRegister(), llvm::MachineBasicBlock::end(), llvm::MachineBasicBlock::isLiveIn(), llvm::next(), llvm::MachineInstr::readsRegister(), llvm::MachineBasicBlock::succ_begin(), and llvm::MachineBasicBlock::succ_end().

|

static |

Definition at line 17048 of file X86ISelLowering.cpp.

References llvm::ISD::AND, llvm::X86ISD::CMOV, llvm::X86ISD::CMP, llvm::X86::COND_B, llvm::X86::COND_E, llvm::X86::COND_NE, llvm::dyn_cast(), llvm::SDValue::getConstantOperandVal(), llvm::SDValue::getNode(), llvm::SDValue::getOpcode(), llvm::SDValue::getOperand(), llvm::X86::GetOppositeBranchCondition(), llvm::SDValue::getResNo(), llvm::ConstantSDNode::getZExtValue(), llvm::SDNode::hasAnyUseOfValue(), llvm::X86ISD::RDRAND, llvm::X86ISD::RDSEED, llvm::X86ISD::SETCC, llvm::X86ISD::SETCC_CARRY, llvm::X86ISD::SUB, llvm::ISD::TRUNCATE, and llvm::ISD::ZERO_EXTEND.

Referenced by PerformBrCondCombine(), PerformCMOVCombine(), and PerformSETCCCombine().

|

static |

Definition at line 19283 of file X86ISelLowering.cpp.

References llvm::SmallVectorTemplateCommon< T >::begin(), llvm::SmallVectorTemplateCommon< T >::end(), and llvm::SmallVectorTemplateCommon< T >::size().

Referenced by llvm::X86TargetLowering::ExpandInlineAsm().

|

static |

Definition at line 17498 of file X86ISelLowering.cpp.

References llvm::ISD::AND, llvm::ISD::ANY_EXTEND, llvm::ISD::BITCAST, llvm::ISD::BR_CC, llvm::ISD::BRCOND, llvm::X86ISD::CMP, llvm::X86::COND_E, llvm::X86::COND_NE, llvm::X86::COND_NP, llvm::X86::COND_P, llvm::ISD::CopyToReg, llvm::MVT::f32, llvm::MVT::f64, llvm::X86ISD::FSETCCsd, llvm::X86ISD::FSETCCss, llvm::SelectionDAG::getConstant(), llvm::SDValue::getConstantOperandVal(), llvm::SelectionDAG::getNode(), llvm::SDValue::getOpcode(), llvm::SDNode::getOperand(), llvm::SDValue::getValueType(), llvm::X86Subtarget::hasSSE2(), llvm::MVT::i32, llvm::MVT::i8, isAndOrOfSetCCs(), llvm::ISD::SELECT, llvm::ISD::SIGN_EXTEND, llvm::ISD::TRUNCATE, llvm::SDNode::use_begin(), llvm::SDNode::use_end(), and llvm::ISD::ZERO_EXTEND.

Referenced by PerformAndCombine(), and PerformOrCombine().

|

static |

CommuteVectorShuffle - Swap vector_shuffle operands as well as values in their permute mask.

Definition at line 4566 of file X86ISelLowering.cpp.

References llvm::ShuffleVectorSDNode::getMaskElt(), llvm::SDNode::getOperand(), llvm::SDNode::getSimpleValueType(), llvm::MVT::getVectorNumElements(), llvm::SelectionDAG::getVectorShuffle(), and llvm::SmallVectorTemplateBase< T, isPodLike< T >::value >::push_back().

|

static |

CommuteVectorShuffleMask - Change values in a shuffle permute mask assuming the two vector operands have swapped position.

Definition at line 3703 of file X86ISelLowering.cpp.

Referenced by isHorizontalBinOp(), LowerVECTOR_SHUFFLE_128v4(), and LowerVECTOR_SHUFFLEv32i8().

|

static |

Definition at line 3861 of file X86ISelLowering.cpp.

References llvm::ShuffleVectorSDNode::getMask(), llvm::SelectionDAG::getNode(), llvm::SDNode::getOperand(), llvm::SDNode::getSimpleValueType(), llvm::SelectionDAG::getVectorShuffle(), isUndefOrEqual(), llvm::ISD::UNDEF, llvm::MVT::v8f32, and llvm::MVT::v8i32.

Referenced by LowerVECTOR_SHUFFLE_256().

|

static |

Concat two 128-bit vectors into a 256 bit vector using VINSERTF128 instructions. This is used because creating CONCAT_VECTOR nodes of BUILD_VECTORS returns a larger BUILD_VECTOR while we're trying to lower large BUILD_VECTORS.

Definition at line 165 of file X86ISelLowering.cpp.

References llvm::SelectionDAG::getUNDEF(), and Insert128BitVector().

Referenced by getOnesVector(), and LowerAVXCONCAT_VECTORS().

|

static |

Definition at line 172 of file X86ISelLowering.cpp.

References llvm::SelectionDAG::getUNDEF(), and Insert256BitVector().

Referenced by LowerAVXCONCAT_VECTORS().

|

static |

CreateCopyOfByValArgument - Make a copy of an aggregate at address specified by "Src" to address "Dst" with size and alignment information specified by the specific parameter attribute. The copy will be passed as a byval function parameter.

Definition at line 2075 of file X86ISelLowering.cpp.

References llvm::ISD::ArgFlagsTy::getByValAlign(), llvm::ISD::ArgFlagsTy::getByValSize(), llvm::SelectionDAG::getConstant(), llvm::SelectionDAG::getMemcpy(), and llvm::MVT::i32.

|

static |

Definition at line 179 of file X86ISelLowering.cpp.

References llvm::TargetMachine::getSubtarget(), llvm::X86Subtarget::is64Bit(), llvm::X86Subtarget::isTargetCOFF(), llvm::X86Subtarget::isTargetELF(), llvm::X86Subtarget::isTargetEnvMacho(), llvm::X86Subtarget::isTargetLinux(), and llvm_unreachable.

|

static |

EltsFromConsecutiveLoads - Given the initializing elements 'Elts' of a vector of type 'VT', see if the elements can be replaced by a single large load which has the same value as a build_vector whose operands are 'elts'.

Example: <load i32 *a, load i32 *a+4, undef, undef> -> zextload a

FIXME: we'd also like to handle the case where the last elements are zero rather than undef via VZEXT_LOAD, but we do not detect that case today. There's even a handy isZeroNode for that purpose.

Definition at line 5397 of file X86ISelLowering.cpp.

References llvm::array_lengthof(), llvm::ISD::BITCAST, llvm::MemSDNode::getAlignment(), llvm::LoadSDNode::getBasePtr(), llvm::MemSDNode::getChain(), llvm::SelectionDAG::getLoad(), llvm::SelectionDAG::getMemIntrinsicNode(), llvm::SDValue::getNode(), llvm::SelectionDAG::getNode(), llvm::SDValue::getOpcode(), llvm::SDNode::getOpcode(), llvm::MemSDNode::getPointerInfo(), llvm::EVT::getSizeInBits(), llvm::SelectionDAG::getTargetLoweringInfo(), llvm::EVT::getVectorElementType(), llvm::SelectionDAG::getVTList(), llvm::SDNode::hasAnyUseOfValue(), llvm::MVT::i64, llvm::SelectionDAG::InferPtrAlignment(), llvm::SelectionDAG::isConsecutiveLoad(), llvm::MemSDNode::isInvariant(), llvm::ISD::isNON_EXTLoad(), llvm::MemSDNode::isNonTemporal(), llvm::TargetLoweringBase::isTypeLegal(), llvm::MemSDNode::isVolatile(), llvm::A64DB::LD, llvm::MVT::Other, llvm::SelectionDAG::ReplaceAllUsesOfValueWith(), llvm::SmallVectorTemplateCommon< T >::size(), llvm::ISD::TokenFactor, llvm::ISD::UNDEF, llvm::SelectionDAG::UpdateNodeOperands(), llvm::MVT::v2i64, and llvm::X86ISD::VZEXT_LOAD.

Referenced by PerformShuffleCombine().

|

static |

Definition at line 14876 of file X86ISelLowering.cpp.

References llvm::MachineInstrBuilder::addOperand(), llvm::X86::AddrNumOperands, llvm::BuildMI(), llvm::TargetOpcode::COPY, llvm::N86::EAX, llvm::N86::ECX, llvm::N86::EDX, llvm::MachineInstr::eraseFromParent(), llvm::MCInstrInfo::get(), llvm::MachineInstr::getDebugLoc(), llvm::MachineInstr::getOperand(), llvm::MachineOperand::getReg(), and llvm::X86Subtarget::is64Bit().

Referenced by llvm::X86TargetLowering::EmitInstrWithCustomInserter().

|

static |

Definition at line 14841 of file X86ISelLowering.cpp.

References llvm::MachineInstrBuilder::addOperand(), llvm::BuildMI(), llvm::TargetOpcode::COPY, llvm::N86::ECX, llvm::MachineInstr::eraseFromParent(), llvm::MCInstrInfo::get(), llvm::MachineInstr::getDebugLoc(), llvm::MachineInstr::getNumOperands(), llvm::MachineInstr::getOpcode(), llvm::MachineInstr::getOperand(), llvm::MachineOperand::getReg(), llvm::MachineInstr::hasOneMemOperand(), llvm::MachineOperand::isImplicit(), llvm::MachineOperand::isReg(), llvm_unreachable, llvm::MachineInstr::memoperands_begin(), llvm::MachineInstr::memoperands_end(), and llvm::MachineInstr::setMemRefs().

Referenced by llvm::X86TargetLowering::EmitInstrWithCustomInserter().

|

static |

Definition at line 14804 of file X86ISelLowering.cpp.

References llvm::MachineInstrBuilder::addOperand(), llvm::BuildMI(), llvm::TargetOpcode::COPY, llvm::MachineInstr::eraseFromParent(), llvm::MCInstrInfo::get(), llvm::MachineInstr::getDebugLoc(), llvm::MachineInstr::getNumOperands(), llvm::MachineInstr::getOpcode(), llvm::MachineInstr::getOperand(), llvm::MachineOperand::getReg(), llvm::MachineInstr::hasOneMemOperand(), llvm::MachineOperand::isImplicit(), llvm::MachineOperand::isReg(), llvm_unreachable, llvm::MachineInstr::memoperands_begin(), llvm::MachineInstr::memoperands_end(), and llvm::MachineInstr::setMemRefs().

Referenced by llvm::X86TargetLowering::EmitInstrWithCustomInserter().

|

static |

EmitTailCallStoreRetAddr - Emit a store of the return address if tail call optimization is performed and it is required (FPDiff!=0).

Definition at line 2479 of file X86ISelLowering.cpp.

References llvm::MachineFrameInfo::CreateFixedObject(), llvm::MachinePointerInfo::getFixedStack(), llvm::SelectionDAG::getFrameIndex(), llvm::MachineFunction::getFrameInfo(), and llvm::SelectionDAG::getStore().

|

static |

Utility function to emit xbegin specifying the start of an RTM region.

Definition at line 14067 of file X86ISelLowering.cpp.

References llvm::MachineBasicBlock::addLiveIn(), llvm::MachineBasicBlock::addSuccessor(), llvm::MachineBasicBlock::begin(), llvm::BuildMI(), llvm::TargetOpcode::COPY, llvm::MachineFunction::CreateMachineBasicBlock(), llvm::N86::EAX, llvm::MachineBasicBlock::end(), llvm::MachineInstr::eraseFromParent(), llvm::MCInstrInfo::get(), llvm::MachineBasicBlock::getBasicBlock(), llvm::MachineInstr::getDebugLoc(), llvm::MachineInstr::getOperand(), llvm::MachineBasicBlock::getParent(), llvm::MachineOperand::getReg(), I, llvm::MachineFunction::insert(), llvm::next(), llvm::MachineBasicBlock::splice(), and llvm::MachineBasicBlock::transferSuccessorsAndUpdatePHIs().

Referenced by llvm::X86TargetLowering::EmitInstrWithCustomInserter().

|

static |

Generate a DAG to grab 128-bits from a vector > 128 bits. This sets things up to match to an AVX VEXTRACTF128 / VEXTRACTI128 or AVX-512 VEXTRACTF32x4 / VEXTRACTI32x4 instructions or a simple subregister reference. Idx is an index in the 128 bits we want. It need not be aligned to a 128-bit bounday. That makes lowering EXTRACT_VECTOR_ELT operations easier.

Definition at line 103 of file X86ISelLowering.cpp.

References ExtractSubVector(), llvm::SDValue::getValueType(), llvm::EVT::is256BitVector(), and llvm::EVT::is512BitVector().

Referenced by Lower256IntArith(), Lower256IntVSETCC(), LowerEXTRACT_SUBVECTOR(), LowerShift(), LowerVECTOR_SHUFFLE_256(), LowerVectorBroadcast(), PerformSELECTCombine(), PerformShuffleCombine256(), PerformSTORECombine(), and PromoteSplat().

|

static |

Generate a DAG to grab 256-bits from a 512-bit vector.

Definition at line 111 of file X86ISelLowering.cpp.

References ExtractSubVector(), llvm::SDValue::getValueType(), and llvm::EVT::is512BitVector().

Referenced by LowerEXTRACT_SUBVECTOR().

|

static |

Extract one bit from mask vector, like v16i1 or v8i1. AVX-512 feature.

Definition at line 16359 of file X86ISelLowering.cpp.

References llvm::ISD::BITCAST, llvm::MipsISD::Ext, llvm::ISD::EXTRACT_VECTOR_ELT, llvm::SelectionDAG::getConstant(), llvm::MVT::getIntegerVT(), llvm::SelectionDAG::getNode(), llvm::SDNode::getOperand(), llvm::SDValue::getSimpleValueType(), llvm::SDNode::getSimpleValueType(), llvm::MVT::getSizeInBits(), llvm::MVT::getVectorElementType(), llvm::MVT::i1, llvm::MVT::i8, llvm::ISD::SHL, llvm::ISD::SRL, llvm::ISD::TRUNCATE, llvm::MVT::v16i1, llvm::MVT::v16i32, llvm::MVT::v8i1, llvm::MVT::v8i64, and llvm::ISD::ZERO_EXTEND.

Referenced by PerformEXTRACT_VECTOR_ELTCombine().

|

static |

Definition at line 62 of file X86ISelLowering.cpp.

References llvm::ISD::BUILD_VECTOR, llvm::ISD::EXTRACT_SUBVECTOR, llvm::SelectionDAG::getContext(), llvm::SelectionDAG::getIntPtrConstant(), llvm::SelectionDAG::getNode(), llvm::SDValue::getOpcode(), llvm::EVT::getSizeInBits(), llvm::SelectionDAG::getUNDEF(), llvm::SDValue::getValueType(), llvm::EVT::getVectorElementType(), llvm::EVT::getVectorNumElements(), llvm::EVT::getVectorVT(), llvm::SDNode::op_begin(), and llvm::ISD::UNDEF.

Referenced by Extract128BitVector(), and Extract256BitVector().

|

static |

FuncIsMadeTailCallSafe - Return true if the function is being made into a tailcall target by changing its ABI.

Definition at line 2112 of file X86ISelLowering.cpp.

References IsTailCallConvention().

Definition at line 14123 of file X86ISelLowering.cpp.

References llvm::EVT::getSimpleVT(), llvm::MVT::i32, llvm::MVT::i64, llvm::MVT::i8, llvm_unreachable, and llvm::MVT::SimpleTy.

Definition at line 4496 of file X86ISelLowering.cpp.

References llvm::SDValue::getNode(), llvm::SDNode::getOperand(), llvm::SDValue::getSimpleValueType(), llvm::MVT::getSizeInBits(), llvm::MVT::getVectorElementType(), and llvm_unreachable.

Referenced by llvm::X86::getExtractVEXTRACT128Immediate(), and llvm::X86::getExtractVEXTRACT256Immediate().

|

static |

Definition at line 11723 of file X86ISelLowering.cpp.

References llvm::array_lengthof(), llvm::dyn_cast(), llvm::SelectionDAG::getTargetConstant(), llvm::SDValue::getValueType(), llvm::EVT::getVectorNumElements(), llvm::MVT::getVectorVT(), getZeroVector(), llvm::ConstantSDNode::getZExtValue(), llvm::MVT::i1, llvm::MVT::i32, llvm::MVT::i8, and llvm::MVT::Other.

Referenced by LowerINTRINSIC_W_CHAIN().

Definition at line 4511 of file X86ISelLowering.cpp.

References llvm::SDValue::getNode(), llvm::SDNode::getOperand(), llvm::SDNode::getSimpleValueType(), llvm::MVT::getSizeInBits(), llvm::MVT::getVectorElementType(), and llvm_unreachable.

Referenced by llvm::X86::getInsertVINSERT128Immediate(), and llvm::X86::getInsertVINSERT256Immediate().

|

static |

getLegalSplat - Generate a legal splat with supported x86 shuffles

Definition at line 4849 of file X86ISelLowering.cpp.

References llvm::ISD::BITCAST, llvm::SelectionDAG::getNode(), llvm::SDValue::getSimpleValueType(), llvm::SelectionDAG::getUNDEF(), llvm::SelectionDAG::getVectorShuffle(), llvm::MVT::is128BitVector(), llvm::MVT::is256BitVector(), llvm_unreachable, llvm::MVT::v4f32, and llvm::MVT::v8f32.

Referenced by PromoteSplat().

Definition at line 14136 of file X86ISelLowering.cpp.

References llvm::EVT::getSimpleVT(), llvm::MVT::i32, llvm::MVT::i64, llvm::MVT::i8, llvm_unreachable, and llvm::MVT::SimpleTy.

getMaxByValAlign - Helper for getByValTypeAlignment to determine the desired ByVal argument alignment.

Definition at line 1565 of file X86ISelLowering.cpp.

Referenced by llvm::X86TargetLowering::getByValTypeAlignment().

|

static |

Definition at line 11744 of file X86ISelLowering.cpp.

References llvm::array_lengthof(), llvm::ISD::BITCAST, llvm::dyn_cast(), llvm::SelectionDAG::getNode(), llvm::SDValue::getOpcode(), llvm::SelectionDAG::getRegister(), llvm::SelectionDAG::getTargetConstant(), llvm::SDValue::getValueType(), llvm::EVT::getVectorNumElements(), llvm::MVT::getVectorVT(), llvm::SelectionDAG::getVTList(), getZeroVector(), llvm::ConstantSDNode::getZExtValue(), llvm::MVT::i1, llvm::MVT::i32, llvm::MVT::i8, llvm::MVT::Other, and llvm::ISD::UNDEF.

Referenced by LowerINTRINSIC_W_CHAIN().

|

static |

Definition at line 7005 of file X86ISelLowering.cpp.

References llvm::ISD::BITCAST, llvm::SelectionDAG::getNode(), llvm::SDValue::getSimpleValueType(), getTargetShuffleNode(), llvm::X86ISD::MOVDDUP, and llvm::MVT::v2f64.

|

static |

Definition at line 7035 of file X86ISelLowering.cpp.

References llvm::SDValue::getOpcode(), llvm::SDValue::getOperand(), llvm::SDValue::getSimpleValueType(), getTargetShuffleNode(), llvm::X86ISD::MOVHLPS, llvm::ISD::UNDEF, llvm::NVPTX::PTXLdStInstCode::V2, llvm::MVT::v4f32, and llvm::MVT::v4i32.

getMOVLMask - Returns a vector_shuffle mask for an movs{s|d}, movd operation of specified width.

Definition at line 4793 of file X86ISelLowering.cpp.

References llvm::EVT::getVectorNumElements(), llvm::SelectionDAG::getVectorShuffle(), and llvm::SmallVectorTemplateBase< T, isPodLike< T >::value >::push_back().

|

static |

Definition at line 7016 of file X86ISelLowering.cpp.

References llvm::ISD::BITCAST, llvm::SelectionDAG::getNode(), llvm::SDValue::getOperand(), llvm::SDValue::getSimpleValueType(), getTargetShuffleNode(), llvm::X86ISD::MOVLHPD, llvm::X86ISD::MOVLHPS, llvm::NVPTX::PTXLdStInstCode::V2, llvm::MVT::v2f64, llvm::MVT::v2i64, and llvm::MVT::v4f32.

|

static |

Definition at line 7051 of file X86ISelLowering.cpp.

References llvm::ShuffleVectorSDNode::getMask(), llvm::ShuffleVectorSDNode::getMaskElt(), llvm::SDValue::getOperand(), getShuffleSHUFImmediate(), llvm::SDValue::getSimpleValueType(), getTargetShuffleNode(), llvm::MVT::getVectorNumElements(), isMOVLMask(), MayFoldIntoStore(), MayFoldVectorLoad(), llvm::X86ISD::MOVLPD, llvm::X86ISD::MOVLPS, llvm::X86ISD::MOVSD, llvm::X86ISD::MOVSS, llvm::X86ISD::SHUFP, llvm::NVPTX::PTXLdStInstCode::V2, and llvm::MVT::v4i32.

|

static |

Definition at line 11784 of file X86ISelLowering.cpp.

References llvm::ISD::BITCAST, llvm::dyn_cast(), llvm::SelectionDAG::getMachineNode(), llvm::SelectionDAG::getNode(), llvm::SelectionDAG::getRegister(), llvm::SelectionDAG::getTargetConstant(), llvm::SDValue::getValueType(), llvm::EVT::getVectorNumElements(), llvm::MVT::getVectorVT(), llvm::SelectionDAG::getVTList(), llvm::ConstantSDNode::getZExtValue(), llvm::MVT::i1, llvm::MVT::i32, llvm::MVT::i8, and llvm::MVT::Other.

Referenced by LowerINTRINSIC_W_CHAIN().

Definition at line 14198 of file X86ISelLowering.cpp.

References llvm_unreachable.

|

static |

Definition at line 14216 of file X86ISelLowering.cpp.

References llvm_unreachable.

Definition at line 14149 of file X86ISelLowering.cpp.

References llvm_unreachable.

Definition at line 14169 of file X86ISelLowering.cpp.

References llvm_unreachable.

|

static |

getNumOfConsecutiveZeros - Return the number of elements of a vector shuffle operation which come from a consecutively from a zero. The search can start in two different directions, from left or right. We count undefs as zeros until PreferredNum is reached.

Definition at line 5081 of file X86ISelLowering.cpp.

References llvm::SDValue::getNode(), llvm::SDValue::getOpcode(), getShuffleScalarElt(), llvm::X86::isZeroNode(), and llvm::ISD::UNDEF.

Referenced by isVectorShiftLeft(), and isVectorShiftRight().

|

static |

getOnesVector - Returns a vector of specified type with all bits set. Always build ones vectors as <4 x i32> or <8 x i32>. For 256-bit types with no AVX2 supprt, use two <4 x i32> inserted in a <8 x i32> appropriately. Then bitcast to their original type, ensuring they get CSE'd.

Definition at line 4758 of file X86ISelLowering.cpp.

References llvm::array_lengthof(), llvm::ISD::BITCAST, llvm::ISD::BUILD_VECTOR, Concat128BitVectors(), llvm::SelectionDAG::getNode(), llvm::SelectionDAG::getTargetConstant(), llvm::MVT::i32, llvm::MVT::is128BitVector(), llvm::MVT::is256BitVector(), llvm::MVT::isVector(), llvm_unreachable, llvm::MVT::v4i32, and llvm::MVT::v8i32.

Definition at line 14229 of file X86ISelLowering.cpp.

References llvm::EVT::getSimpleVT(), llvm::MVT::i32, llvm::MVT::i8, llvm_unreachable, and llvm::MVT::SimpleTy.

|

static |

Definition at line 11766 of file X86ISelLowering.cpp.

References llvm::dyn_cast(), llvm::SelectionDAG::getConstant(), llvm::SelectionDAG::getMachineNode(), llvm::SelectionDAG::getRegister(), llvm::SelectionDAG::getTargetConstant(), llvm::SDValue::getValueType(), llvm::EVT::getVectorNumElements(), llvm::MVT::getVectorVT(), llvm::SelectionDAG::getVTList(), llvm::ConstantSDNode::getZExtValue(), llvm::MVT::i1, llvm::MVT::i32, llvm::MVT::i8, and llvm::MVT::Other.

Referenced by LowerINTRINSIC_W_CHAIN().

|

static |

getShufflePALIGNRImmediate - Return the appropriate immediate to shuffle the specified VECTOR_SHUFFLE mask with the PALIGNR instruction.

Definition at line 4473 of file X86ISelLowering.cpp.

References llvm::ShuffleVectorSDNode::getMaskElt(), llvm::SDNode::getSimpleValueType(), llvm::MVT::getSizeInBits(), llvm::MVT::getVectorElementType(), llvm::MVT::getVectorNumElements(), and llvm::MVT::is512BitVector().

|

static |

getShufflePSHUFHWImmediate - Return the appropriate immediate to shuffle the specified VECTOR_SHUFFLE mask with the PSHUFHW instruction.

Definition at line 4425 of file X86ISelLowering.cpp.

References llvm::ShuffleVectorSDNode::getMaskElt(), llvm::SDNode::getSimpleValueType(), llvm::MVT::getVectorNumElements(), llvm::MVT::v16i16, and llvm::MVT::v8i16.

Referenced by LowerVECTOR_SHUFFLEv8i16().

|

static |

getShufflePSHUFLWImmediate - Return the appropriate immediate to shuffle the specified VECTOR_SHUFFLE mask with the PSHUFLW instruction.

Definition at line 4449 of file X86ISelLowering.cpp.

References llvm::ShuffleVectorSDNode::getMaskElt(), llvm::SDNode::getSimpleValueType(), llvm::MVT::getVectorNumElements(), llvm::MVT::v16i16, and llvm::MVT::v8i16.

Referenced by LowerVECTOR_SHUFFLEv8i16().

|

static |

getShuffleScalarElt - Returns the scalar element that will make up the ith element of the result of the vector shuffle.

Definition at line 5015 of file X86ISelLowering.cpp.

References llvm::ISD::BITCAST, llvm::ISD::BUILD_VECTOR, llvm::SDValue::getNode(), llvm::SDValue::getOpcode(), llvm::SDValue::getOperand(), llvm::SDNode::getOperand(), llvm::SDValue::getSimpleValueType(), getTargetShuffleMask(), llvm::SelectionDAG::getUNDEF(), llvm::SDValue::getValueType(), llvm::MVT::getVectorElementType(), llvm::EVT::getVectorElementType(), llvm::MVT::getVectorNumElements(), llvm::EVT::getVectorNumElements(), isTargetShuffle(), llvm::EVT::isVector(), and llvm::ISD::SCALAR_TO_VECTOR.

Referenced by getNumOfConsecutiveZeros(), and PerformShuffleCombine().

|

static |

getShuffleSHUFImmediate - Return the appropriate immediate to shuffle the specified VECTOR_SHUFFLE mask with PSHUF* and SHUFP* instructions. Handles 128-bit and 256-bit.

Definition at line 4395 of file X86ISelLowering.cpp.

References llvm::ShuffleVectorSDNode::getMaskElt(), llvm::SDNode::getSimpleValueType(), llvm::MVT::getSizeInBits(), and llvm::MVT::getVectorNumElements().

Referenced by getMOVLP().

|

static |

getShuffleVectorZeroOrUndef - Return a vector_shuffle of the specified vector of zero or undef vector. This produces a shuffle where the low element of V2 is swizzled into the zero/undef vector, landing at element Idx. This produces a shuffle mask like 4,1,2,3 (idx=0) or 0,1,2,4 (idx=3).

Definition at line 4917 of file X86ISelLowering.cpp.

References llvm::SDValue::getSimpleValueType(), llvm::SelectionDAG::getUNDEF(), llvm::MVT::getVectorNumElements(), llvm::SelectionDAG::getVectorShuffle(), getZeroVector(), and llvm::SmallVectorTemplateBase< T, isPodLike< T >::value >::push_back().

Referenced by llvm::X86TargetLowering::BuildFILD().

|

static |

getShuffleVPERM2X128Immediate - Return the appropriate immediate to shuffle the specified VECTOR_MASK mask with VPERM2F128/VPERM2I128 instructions.

Definition at line 4134 of file X86ISelLowering.cpp.

References llvm::ShuffleVectorSDNode::getMaskElt(), llvm::SDNode::getSimpleValueType(), and llvm::MVT::getVectorNumElements().

|

static |

getTargetShuffleMask - Calculates the shuffle mask corresponding to the target specific opcode. Returns true if the Mask could be calculated. Sets IsUnary to true if only uses one source.

Definition at line 4935 of file X86ISelLowering.cpp.

References llvm::DecodeMOVHLPSMask(), llvm::DecodeMOVLHPSMask(), llvm::DecodePALIGNRMask(), llvm::DecodePSHUFHWMask(), llvm::DecodePSHUFLWMask(), llvm::DecodePSHUFMask(), llvm::DecodeSHUFPMask(), llvm::DecodeUNPCKHMask(), llvm::DecodeUNPCKLMask(), llvm::DecodeVPERM2X128Mask(), llvm::DecodeVPERMMask(), llvm::SmallVectorBase::empty(), llvm::SDNode::getNumOperands(), llvm::SDNode::getOpcode(), llvm::SDNode::getOperand(), llvm::MVT::getVectorNumElements(), llvm_unreachable, llvm::X86ISD::MOVDDUP, llvm::X86ISD::MOVHLPS, llvm::X86ISD::MOVLHPD, llvm::X86ISD::MOVLHPS, llvm::X86ISD::MOVLPD, llvm::X86ISD::MOVLPS, llvm::X86ISD::MOVSD, llvm::X86ISD::MOVSHDUP, llvm::X86ISD::MOVSLDUP, llvm::X86ISD::MOVSS, llvm::X86ISD::PALIGNR, llvm::X86ISD::PSHUFD, llvm::X86ISD::PSHUFHW, llvm::X86ISD::PSHUFLW, llvm::SmallVectorTemplateBase< T, isPodLike >::push_back(), llvm::X86ISD::SHUFP, llvm::X86ISD::UNPCKH, llvm::X86ISD::UNPCKL, llvm::X86ISD::VPERM2X128, llvm::X86ISD::VPERMI, and llvm::X86ISD::VPERMILP.

Referenced by getShuffleScalarElt(), and XFormVExtractWithShuffleIntoLoad().

|

static |

Definition at line 3289 of file X86ISelLowering.cpp.

References llvm::SelectionDAG::getNode(), llvm_unreachable, llvm::X86ISD::MOVDDUP, llvm::X86ISD::MOVSHDUP, and llvm::X86ISD::MOVSLDUP.

Referenced by llvm::X86TargetLowering::BuildFILD(), getMOVDDup(), getMOVHighToLow(), getMOVLowToHigh(), getMOVLP(), and LowerVECTOR_SHUFFLEv8i16().

|

static |

Definition at line 3300 of file X86ISelLowering.cpp.

References llvm::SelectionDAG::getConstant(), llvm::SelectionDAG::getNode(), llvm::MVT::i8, llvm_unreachable, llvm::X86ISD::PSHUFD, llvm::X86ISD::PSHUFHW, llvm::X86ISD::PSHUFLW, llvm::X86ISD::VPERMI, and llvm::X86ISD::VPERMILP.

|

static |

Definition at line 3314 of file X86ISelLowering.cpp.

References llvm::SelectionDAG::getConstant(), llvm::SelectionDAG::getNode(), llvm::MVT::i8, llvm_unreachable, llvm::X86ISD::PALIGNR, llvm::X86ISD::SHUFP, and llvm::X86ISD::VPERM2X128.

|

static |

Definition at line 3327 of file X86ISelLowering.cpp.

References llvm::SelectionDAG::getNode(), llvm_unreachable, llvm::X86ISD::MOVHLPS, llvm::X86ISD::MOVLHPD, llvm::X86ISD::MOVLHPS, llvm::X86ISD::MOVLPD, llvm::X86ISD::MOVLPS, llvm::X86ISD::MOVSD, llvm::X86ISD::MOVSS, llvm::X86ISD::UNPCKH, and llvm::X86ISD::UNPCKL.

|

static |

Definition at line 10967 of file X86ISelLowering.cpp.

References llvm::SelectionDAG::getConstant(), llvm::SelectionDAG::getNode(), llvm::EVT::getSizeInBits(), llvm::EVT::getVectorElementType(), llvm::MVT::i8, llvm::X86ISD::VSHLI, llvm::X86ISD::VSRAI, and llvm::X86ISD::VSRLI.

Referenced by getTargetVShiftNode(), LowerMUL(), LowerScalarImmediateShift(), and LowerShift().

|

static |

Definition at line 10987 of file X86ISelLowering.cpp.

References llvm::ISD::BITCAST, llvm::ISD::BUILD_VECTOR, llvm::SelectionDAG::getConstant(), llvm::SelectionDAG::getNode(), llvm::EVT::getSimpleVT(), llvm::MVT::getSizeInBits(), getTargetVShiftByConstNode(), llvm::SelectionDAG::getUNDEF(), llvm::SDValue::getValueType(), llvm::EVT::getVectorElementType(), llvm::MVT::getVectorVT(), llvm::MVT::i32, llvm_unreachable, llvm::MVT::v4i32, llvm::X86ISD::VSHL, llvm::X86ISD::VSHLI, llvm::X86ISD::VSRA, llvm::X86ISD::VSRAI, llvm::X86ISD::VSRL, and llvm::X86ISD::VSRLI.

Referenced by LowerINTRINSIC_WO_CHAIN(), and LowerScalarVariableShift().

|

static |

Definition at line 8132 of file X86ISelLowering.cpp.

References llvm::array_lengthof(), llvm::SelectionDAG::getCopyFromReg(), llvm::MachineFunction::getFrameInfo(), llvm::GlobalAddressSDNode::getGlobal(), llvm::SelectionDAG::getMachineFunction(), llvm::SelectionDAG::getNode(), llvm::GlobalAddressSDNode::getOffset(), llvm::SelectionDAG::getTargetGlobalAddress(), llvm::SDValue::getValue(), llvm::SDNode::getValueType(), llvm::SelectionDAG::getVTList(), llvm::MVT::Glue, llvm::TLSModel::LocalDynamic, llvm::MVT::Other, llvm::MachineFrameInfo::setAdjustsStack(), llvm::X86ISD::TLSADDR, and llvm::X86ISD::TLSBASEADDR.

Referenced by LowerToTLSGeneralDynamicModel32(), LowerToTLSGeneralDynamicModel64(), and LowerToTLSLocalDynamicModel().

getUnpackh - Returns a vector_shuffle node for an unpackh operation.

Definition at line 4816 of file X86ISelLowering.cpp.

References llvm::MVT::getVectorNumElements(), llvm::SelectionDAG::getVectorShuffle(), and llvm::SmallVectorTemplateBase< T, isPodLike< T >::value >::push_back().

Referenced by LowerAVXExtend(), and PromoteSplati8i16().

getUnpackl - Returns a vector_shuffle node for an unpackl operation.

Definition at line 4804 of file X86ISelLowering.cpp.

References llvm::MVT::getVectorNumElements(), llvm::SelectionDAG::getVectorShuffle(), and llvm::SmallVectorTemplateBase< T, isPodLike< T >::value >::push_back().

Referenced by llvm::X86TargetLowering::BuildFILD(), LowerAVXExtend(), and PromoteSplati8i16().

|

static |

getVShift - Return a vector logical shift node.

Definition at line 5301 of file X86ISelLowering.cpp.

References llvm::ISD::BITCAST, llvm::SelectionDAG::getConstant(), llvm::SelectionDAG::getNode(), llvm::TargetLoweringBase::getScalarShiftAmountTy(), llvm::SDValue::getValueType(), llvm::EVT::is128BitVector(), llvm::MVT::v2i64, llvm::X86ISD::VSHLDQ, and llvm::X86ISD::VSRLDQ.

|

static |

getVZextMovL - Return a zero-extending vector move low node.

Definition at line 6701 of file X86ISelLowering.cpp.

References llvm::ISD::BITCAST, llvm::dyn_cast(), llvm::SDValue::getNode(), llvm::SelectionDAG::getNode(), llvm::SDValue::getOpcode(), llvm::SDValue::getOperand(), llvm::SDValue::getValueType(), llvm::MVT::i32, llvm::MVT::i64, llvm::X86Subtarget::is64Bit(), isScalarLoadToVector(), llvm::A64DB::LD, llvm::ISD::SCALAR_TO_VECTOR, llvm::MVT::v2f64, llvm::MVT::v2i64, llvm::MVT::v4f32, llvm::MVT::v4i32, and llvm::X86ISD::VZEXT_MOVL.

Referenced by NormalizeVectorShuffle().

|

static |

getZeroVector - Returns a vector of specified type with all zero elements.

Definition at line 4714 of file X86ISelLowering.cpp.

References llvm::array_lengthof(), llvm::ISD::BITCAST, llvm::ISD::BUILD_VECTOR, llvm::MVT::f32, llvm::SelectionDAG::getNode(), llvm::SelectionDAG::getTargetConstant(), llvm::SelectionDAG::getTargetConstantFP(), llvm::X86Subtarget::hasInt256(), llvm::X86Subtarget::hasSSE2(), llvm::MVT::i32, llvm::EVT::is128BitVector(), llvm::EVT::is256BitVector(), llvm::EVT::is512BitVector(), llvm::EVT::isVector(), llvm_unreachable, llvm::MVT::v16i32, llvm::MVT::v4f32, llvm::MVT::v4i32, llvm::MVT::v8f32, and llvm::MVT::v8i32.

Referenced by getGatherNode(), getMGatherNode(), getShuffleVectorZeroOrUndef(), LowerAVXExtend(), LowerBuildVectorv16i8(), LowerBuildVectorv8i16(), LowerScalarImmediateShift(), NormalizeVectorShuffle(), performShiftToAllZeros(), and PerformShuffleCombine256().

hasFPCMov - is there a floating point cmov for the specific X86 condition code. Current x86 isa includes the following FP cmov instructions: fcmovb, fcomvbe, fcomve, fcmovu, fcmovae, fcmova, fcmovne, fcmovnu.

Definition at line 3509 of file X86ISelLowering.cpp.

References llvm::X86::COND_A, llvm::X86::COND_AE, llvm::X86::COND_B, llvm::X86::COND_BE, llvm::X86::COND_E, llvm::X86::COND_NE, llvm::X86::COND_NP, and llvm::X86::COND_P.

Referenced by PerformCMOVCombine().

|

static |

Generate a DAG to put 128-bits into a vector > 128 bits. This sets things up to match to an AVX VINSERTF128/VINSERTI128 or AVX-512 VINSERTF32x4/VINSERTI32x4 instructions or a simple superregister reference. Idx is an index in the 128 bits we want. It need not be aligned to a 128-bit bounday. That makes lowering INSERT_VECTOR_ELT operations easier.

Definition at line 147 of file X86ISelLowering.cpp.

References llvm::SDValue::getValueType(), InsertSubVector(), and llvm::EVT::is128BitVector().

Referenced by Concat128BitVectors(), LowerINSERT_SUBVECTOR(), LowerSCALAR_TO_VECTOR(), PerformLOADCombine(), and PerformShuffleCombine256().

|

static |

Definition at line 154 of file X86ISelLowering.cpp.

References llvm::SDValue::getValueType(), InsertSubVector(), and llvm::EVT::is256BitVector().

Referenced by Concat256BitVectors(), and LowerINSERT_SUBVECTOR().

|

static |

Definition at line 117 of file X86ISelLowering.cpp.

References llvm::SelectionDAG::getIntPtrConstant(), llvm::SelectionDAG::getNode(), llvm::SDValue::getOpcode(), llvm::EVT::getSizeInBits(), llvm::SDValue::getValueType(), llvm::EVT::getVectorElementType(), llvm::ISD::INSERT_SUBVECTOR, and llvm::ISD::UNDEF.

Referenced by Insert128BitVector(), and Insert256BitVector().

Definition at line 9681 of file X86ISelLowering.cpp.

References llvm::dyn_cast(), and llvm::ConstantSDNode::isAllOnesValue().

Referenced by PerformAndCombine(), and PerformXorCombine().

Definition at line 10459 of file X86ISelLowering.cpp.

References llvm::ISD::AND, llvm::SDValue::getOpcode(), llvm::SDValue::getOperand(), llvm::SDValue::hasOneUse(), llvm::ISD::OR, and llvm::X86ISD::SETCC.

Referenced by CMPEQCombine().

|

static |

Return true if the calling convention is a C calling convention.

Definition at line 2093 of file X86ISelLowering.cpp.

References llvm::CallingConv::C, llvm::CallingConv::X86_64_SysV, and llvm::CallingConv::X86_64_Win64.

|

static |

isCommutedMOVLMask - Returns true if the shuffle mask is except the reverse of what x86 movss want. X86 movs requires the lowest element to be lowest element of vector 2 and the other elements to come from vector 1 in order.

Definition at line 4233 of file X86ISelLowering.cpp.

References llvm::MVT::getVectorNumElements(), llvm::MVT::is128BitVector(), isUndefOrEqual(), and isUndefOrInRange().

Referenced by llvm::X86TargetLowering::isVectorClearMaskLegal(), and NormalizeVectorShuffle().

isHorizontalBinOp - Return 'true' if this vector operation is "horizontal" and return the operands for the horizontal operation in LHS and RHS. A horizontal operation performs the binary operation on successive elements of its first operand, then on successive elements of its second operand, returning the resulting values in a vector. For example, if A = < float a0, float a1, float a2, float a3 > and B = < float b0, float b1, float b2, float b3 > then the result of doing a horizontal operation on A and B is A horizontal-op B = < a0 op a1, a2 op a3, b0 op b1, b2 op b3 >. In short, LHS and RHS are inspected to see if LHS op RHS is of the form A horizontal-op B, for some already available A and B, and if so then LHS is set to A, RHS to B, and the routine returns 'true'. Note that the binary operation should have the property that if one of the operands is UNDEF then the result is UNDEF.

Definition at line 18469 of file X86ISelLowering.cpp.

References llvm::ARM_PROC::A, llvm::ArrayRef< T >::begin(), llvm::SmallVectorTemplateCommon< T >::begin(), llvm::CallingConv::C, CommuteVectorShuffleMask(), llvm::ArrayRef< T >::end(), llvm::SDValue::getNode(), llvm::SDValue::getOpcode(), llvm::SDValue::getOperand(), llvm::SDValue::getSimpleValueType(), llvm::MVT::getSizeInBits(), llvm::MVT::getVectorNumElements(), llvm::MVT::is128BitVector(), llvm::MVT::is256BitVector(), llvm::ISD::UNDEF, and llvm::ISD::VECTOR_SHUFFLE.

Referenced by PerformAddCombine(), PerformFADDCombine(), PerformFSUBCombine(), and PerformSubCombine().

isMOVDDUPMask - Return true if the specified VECTOR_SHUFFLE operand specifies a shuffle of elements that is suitable for input to 128-bit version of MOVDDUP.

Definition at line 4325 of file X86ISelLowering.cpp.

References llvm::MVT::getVectorNumElements(), llvm::MVT::is128BitVector(), and isUndefOrEqual().

isMOVDDUPYMask - Return true if the specified VECTOR_SHUFFLE operand specifies a shuffle of elements that is suitable for input to 256-bit version of MOVDDUP.

Definition at line 4305 of file X86ISelLowering.cpp.

References llvm::MVT::getVectorNumElements(), llvm::MVT::is256BitVector(), and isUndefOrEqual().

isMOVHLPS_v_undef_Mask - Special case of isMOVHLPSMask for canonical form of vector_shuffle v, v, <2, 3, 2, 3>, i.e. vector_shuffle v, undef, <2, 3, 2, 3>

Definition at line 3798 of file X86ISelLowering.cpp.

References llvm::MVT::getVectorNumElements(), llvm::MVT::is128BitVector(), and isUndefOrEqual().

isMOVHLPSMask - Return true if the specified VECTOR_SHUFFLE operand specifies a shuffle of elements that is suitable for input to MOVHLPS.

Definition at line 3779 of file X86ISelLowering.cpp.

References llvm::MVT::getVectorNumElements(), llvm::MVT::is128BitVector(), and isUndefOrEqual().

isMOVLHPSMask - Return true if the specified VECTOR_SHUFFLE operand specifies a shuffle of elements that is suitable for input to MOVLHPS.

Definition at line 3837 of file X86ISelLowering.cpp.

References llvm::MVT::getVectorNumElements(), llvm::MVT::is128BitVector(), and isUndefOrEqual().

isMOVLMask - Return true if the specified VECTOR_SHUFFLE operand specifies a shuffle of elements that is suitable for input to MOVSS, MOVSD, and MOVD, i.e. setting the lowest element.

Definition at line 4079 of file X86ISelLowering.cpp.

References llvm::EVT::getSizeInBits(), llvm::EVT::getVectorElementType(), llvm::EVT::getVectorNumElements(), llvm::EVT::is128BitVector(), and isUndefOrEqual().

Referenced by getMOVLP(), llvm::X86TargetLowering::isShuffleMaskLegal(), llvm::X86TargetLowering::isVectorClearMaskLegal(), and NormalizeVectorShuffle().

isMOVLPMask - Return true if the specified VECTOR_SHUFFLE operand specifies a shuffle of elements that is suitable for input to MOVLP{S|D}.

Definition at line 3815 of file X86ISelLowering.cpp.

References llvm::MVT::getVectorNumElements(), llvm::MVT::is128BitVector(), and isUndefOrEqual().

|

static |

isMOVSHDUPMask - Return true if the specified VECTOR_SHUFFLE operand specifies a shuffle of elements that is suitable for input to MOVSHDUP. Masks to match: <1, 1, 3, 3> or <1, 1, 3, 3, 5, 5, 7, 7>

Definition at line 4257 of file X86ISelLowering.cpp.

References llvm::MVT::getVectorNumElements(), llvm::X86Subtarget::hasSSE3(), llvm::MVT::is128BitVector(), llvm::MVT::is256BitVector(), llvm::MVT::is512BitVector(), and isUndefOrEqual().

|

static |

isMOVSLDUPMask - Return true if the specified VECTOR_SHUFFLE operand specifies a shuffle of elements that is suitable for input to MOVSLDUP. Masks to match: <0, 0, 2, 2> or <0, 0, 2, 2, 4, 4, 6, 6>

Definition at line 4281 of file X86ISelLowering.cpp.

References llvm::MVT::getVectorNumElements(), llvm::X86Subtarget::hasSSE3(), llvm::MVT::is128BitVector(), llvm::MVT::is256BitVector(), llvm::MVT::is512BitVector(), and isUndefOrEqual().

|

static |

isPALIGNRMask - Return true if the node specifies a shuffle of elements that is suitable for input to PALIGNR.

Definition at line 3630 of file X86ISelLowering.cpp.

References llvm::MVT::getSizeInBits(), llvm::MVT::getVectorNumElements(), llvm::X86Subtarget::hasInt256(), llvm::X86Subtarget::hasSSSE3(), llvm::MVT::is128BitVector(), llvm::MVT::is256BitVector(), llvm::MVT::is512BitVector(), isUndefOrEqual(), and isUndefOrInRange().

Referenced by llvm::X86TargetLowering::isShuffleMaskLegal().

Definition at line 4157 of file X86ISelLowering.cpp.

References llvm::MVT::getSizeInBits(), llvm::MVT::getVectorElementType(), llvm::MVT::getVectorNumElements(), llvm::MVT::is128BitVector(), llvm::MVT::is256BitVector(), and isUndefOrInRange().

isPSHUFDMask - Return true if the node specifies a shuffle of elements that is suitable for input to PSHUFD or PSHUFW. That is, it doesn't reference the second operand.

Definition at line 3562 of file X86ISelLowering.cpp.

References llvm::MVT::v2f64, llvm::MVT::v2i64, llvm::MVT::v4f32, and llvm::MVT::v4i32.

Referenced by llvm::X86TargetLowering::isShuffleMaskLegal().

isPSHUFHWMask - Return true if the node specifies a shuffle of elements that is suitable for input to PSHUFHW.

Definition at line 3572 of file X86ISelLowering.cpp.

References isSequentialOrUndefInRange(), isUndefOrInRange(), llvm::MVT::v16i16, and llvm::MVT::v8i16.

Referenced by llvm::X86TargetLowering::isShuffleMaskLegal().

isPSHUFLWMask - Return true if the node specifies a shuffle of elements that is suitable for input to PSHUFLW.

Definition at line 3601 of file X86ISelLowering.cpp.

References isSequentialOrUndefInRange(), isUndefOrInRange(), llvm::MVT::v16i16, and llvm::MVT::v8i16.

Referenced by llvm::X86TargetLowering::isShuffleMaskLegal().

|

static |

isScalarLoadToVector - Returns true if the node is a scalar load that is promoted to a vector. It also returns the LoadSDNode by reference if required.

Definition at line 4607 of file X86ISelLowering.cpp.

References llvm::SDValue::getNode(), llvm::SDNode::getOpcode(), llvm::SDNode::getOperand(), llvm::ISD::isNON_EXTLoad(), llvm::A64DB::LD, N, and llvm::ISD::SCALAR_TO_VECTOR.

Referenced by getVZextMovL(), and ShouldXformToMOVLP().

|

static |

isSequentialOrUndefInRange - Return true if every element in Mask, beginning from position Pos and ending in Pos+Size, falls within the specified sequential range (L, L+Pos]. or is undef.

Definition at line 3551 of file X86ISelLowering.cpp.

References isUndefOrEqual().

Referenced by isPSHUFHWMask(), isPSHUFLWMask(), and isVPERM2X128Mask().

|

static |

isShuffleHigh128VectorInsertLow - Checks whether the shuffle node is the same as extracting the high 128-bit part of 256-bit vector and then inserting the result into the low part of a new 256-bit vector

Definition at line 16097 of file X86ISelLowering.cpp.

References llvm::ShuffleVectorSDNode::getMaskElt(), llvm::SDNode::getValueType(), llvm::EVT::getVectorNumElements(), and isUndefOrEqual().

Referenced by PerformShuffleCombine256().

|

static |

isShuffleLow128VectorInsertHigh - Checks whether the shuffle node is the same as extracting the low 128-bit part of 256-bit vector and then inserting the result into the high part of a new 256-bit vector

Definition at line 16113 of file X86ISelLowering.cpp.

References llvm::ShuffleVectorSDNode::getMaskElt(), llvm::SDNode::getValueType(), llvm::EVT::getVectorNumElements(), and isUndefOrEqual().

Referenced by PerformShuffleCombine256().

|

static |

isShuffleMaskConsecutive - Check if the shuffle mask indicies [MaskI, MaskE) correspond consecutively to elements from one of the vector operands, starting from its index OpIdx. Also tell OpNum which source vector operand.

Definition at line 5107 of file X86ISelLowering.cpp.

References llvm::ShuffleVectorSDNode::getMaskElt().

Referenced by isVectorShiftLeft(), and isVectorShiftRight().

isSHUFPMask - Return true if the specified VECTOR_SHUFFLE operand specifies a shuffle of elements that is suitable for input to 128/256-bit SHUFPS and SHUFPD. If Commuted is true, then it checks for sources to be reverse of what x86 shuffles want.

Definition at line 3720 of file X86ISelLowering.cpp.

References llvm::MVT::getSizeInBits(), llvm::MVT::getVectorElementType(), llvm::MVT::getVectorNumElements(), and isUndefOrInRange().

Referenced by llvm::X86TargetLowering::isShuffleMaskLegal(), and llvm::X86TargetLowering::isVectorClearMaskLegal().

isSplatVector - Returns true if N is a BUILD_VECTOR node whose elements are all the same.

Definition at line 4673 of file X86ISelLowering.cpp.

References llvm::ISD::BUILD_VECTOR, llvm::SDNode::getNumOperands(), llvm::SDNode::getOpcode(), and llvm::SDNode::getOperand().

Referenced by LowerScalarImmediateShift(), LowerVectorBroadcast(), PerformOrCombine(), PerformSELECTCombine(), performShiftToAllZeros(), PerformSHLCombine(), and WidenMaskArithmetic().

|

static |

IsTailCallConvention - Return true if the calling convention is one that supports tail call optimization.

Definition at line 2087 of file X86ISelLowering.cpp.

References llvm::CallingConv::Fast, llvm::CallingConv::GHC, and llvm::CallingConv::HiPE.

Referenced by FuncIsMadeTailCallSafe().

Definition at line 3262 of file X86ISelLowering.cpp.

References llvm::X86ISD::MOVDDUP, llvm::X86ISD::MOVHLPS, llvm::X86ISD::MOVLHPD, llvm::X86ISD::MOVLHPS, llvm::X86ISD::MOVLPD, llvm::X86ISD::MOVLPS, llvm::X86ISD::MOVSD, llvm::X86ISD::MOVSHDUP, llvm::X86ISD::MOVSLDUP, llvm::X86ISD::MOVSS, llvm::X86ISD::PALIGNR, llvm::X86ISD::PSHUFD, llvm::X86ISD::PSHUFHW, llvm::X86ISD::PSHUFLW, llvm::X86ISD::SHUFP, llvm::X86ISD::UNPCKH, llvm::X86ISD::UNPCKL, llvm::X86ISD::VPERM2X128, llvm::X86ISD::VPERMI, and llvm::X86ISD::VPERMILP.

Referenced by getShuffleScalarElt(), and XFormVExtractWithShuffleIntoLoad().

|

static |

Definition at line 10152 of file X86ISelLowering.cpp.

References llvm::tgtok::Bits, llvm::APInt::getHighBitsSet(), llvm::SDValue::getOpcode(), llvm::SDValue::getOperand(), llvm::SDValue::getValueSizeInBits(), llvm::SelectionDAG::MaskedValueIsZero(), and llvm::ISD::TRUNCATE.

|

static |

isUndefOrEqual - Val is either less than zero (undef) or equal to the specified value.

Definition at line 3544 of file X86ISelLowering.cpp.

Referenced by Compact8x32ShuffleNode(), isCommutedMOVLMask(), isMOVDDUPMask(), isMOVDDUPYMask(), isMOVHLPS_v_undef_Mask(), isMOVHLPSMask(), isMOVLHPSMask(), isMOVLMask(), isMOVLPMask(), isMOVSHDUPMask(), isMOVSLDUPMask(), isPALIGNRMask(), isSequentialOrUndefInRange(), isShuffleHigh128VectorInsertLow(), isShuffleLow128VectorInsertHigh(), isUNPCKH_v_undef_Mask(), isUNPCKHMask(), isUNPCKL_v_undef_Mask(), isUNPCKLMask(), isVPERMILPMask(), PerformShuffleCombine256(), ShouldXformToMOVHLPS(), and ShouldXformToMOVLP().

|

static |

isUndefOrInRange - Return true if Val is undef or if its value falls within the specified range (L, H].

Definition at line 3538 of file X86ISelLowering.cpp.

References llvm::HexagonISD::Hi.

Referenced by isCommutedMOVLMask(), isPALIGNRMask(), isPermImmMask(), isPSHUFHWMask(), isPSHUFLWMask(), isSHUFPMask(), and isVPERMILPMask().

isUNPCKH_v_undef_Mask - Special case of isUNPCKHMask for canonical form of vector_shuffle v, v, <2, 6, 3, 7>, i.e. vector_shuffle v, undef, <2, 2, 3, 3>

Definition at line 4045 of file X86ISelLowering.cpp.

References llvm::MVT::getSizeInBits(), llvm::MVT::getVectorNumElements(), llvm::MVT::is128BitVector(), llvm::MVT::is256BitVector(), llvm::MVT::is512BitVector(), and isUndefOrEqual().

Referenced by llvm::X86TargetLowering::isShuffleMaskLegal().

|

static |

isUNPCKHMask - Return true if the specified VECTOR_SHUFFLE operand specifies a shuffle of elements that is suitable for input to UNPCKH.

Definition at line 3954 of file X86ISelLowering.cpp.

References llvm::MVT::getScalarType(), llvm::MVT::getSizeInBits(), llvm::MVT::getVectorNumElements(), llvm::MVT::is256BitVector(), llvm::MVT::is512BitVector(), and isUndefOrEqual().

Referenced by llvm::X86TargetLowering::isShuffleMaskLegal().

isUNPCKL_v_undef_Mask - Special case of isUNPCKLMask for canonical form of vector_shuffle v, v, <0, 4, 1, 5>, i.e. vector_shuffle v, undef, <0, 0, 1, 1>

Definition at line 4002 of file X86ISelLowering.cpp.

References llvm::MVT::getSizeInBits(), llvm::MVT::getVectorNumElements(), llvm::MVT::is128BitVector(), llvm::MVT::is256BitVector(), llvm::MVT::is512BitVector(), and isUndefOrEqual().

Referenced by llvm::X86TargetLowering::isShuffleMaskLegal().

|

static |

isUNPCKLMask - Return true if the specified VECTOR_SHUFFLE operand specifies a shuffle of elements that is suitable for input to UNPCKL.

Definition at line 3906 of file X86ISelLowering.cpp.

References llvm::MVT::getScalarType(), llvm::MVT::getSizeInBits(), llvm::MVT::getVectorNumElements(), llvm::MVT::is256BitVector(), llvm::MVT::is512BitVector(), and isUndefOrEqual().

Referenced by llvm::X86TargetLowering::isShuffleMaskLegal().

|

static |

isVectorShift - Returns true if the shuffle can be implemented as a logical left or right shift of a vector.

Definition at line 5205 of file X86ISelLowering.cpp.

References llvm::SDNode::getSimpleValueType(), llvm::MVT::is128BitVector(), isVectorShiftLeft(), and isVectorShiftRight().

|

static |

isVectorShiftLeft - Returns true if the shuffle can be implemented as a logical left shift of a vector.

Definition at line 5170 of file X86ISelLowering.cpp.

References llvm::ShuffleVectorSDNode::getMaskElt(), getNumOfConsecutiveZeros(), llvm::SDNode::getOperand(), llvm::SDNode::getSimpleValueType(), llvm::MVT::getVectorNumElements(), and isShuffleMaskConsecutive().

Referenced by isVectorShift().

|

static |

isVectorShiftRight - Returns true if the shuffle can be implemented as a logical left shift of a vector.

Definition at line 5135 of file X86ISelLowering.cpp.

References llvm::ShuffleVectorSDNode::getMaskElt(), getNumOfConsecutiveZeros(), llvm::SDNode::getOperand(), llvm::SDNode::getSimpleValueType(), llvm::MVT::getVectorNumElements(), and isShuffleMaskConsecutive().

Referenced by isVectorShift().

isVEXTRACTIndex - Return true if the specified EXTRACT_SUBVECTOR operand specifies a vector extract that is suitable for instruction that extract 128 or 256 bit vectors

Definition at line 4342 of file X86ISelLowering.cpp.

References llvm::SDValue::getNode(), llvm::SDNode::getOperand(), llvm::SDNode::getSimpleValueType(), llvm::MVT::getSizeInBits(), and llvm::MVT::getVectorElementType().

Referenced by llvm::X86::isVEXTRACT128Index(), and llvm::X86::isVEXTRACT256Index().

isVINSERTIndex - Return true if the specified INSERT_SUBVECTOR operand specifies a subvector insert that is suitable for input to insertion of 128 or 256-bit subvectors

Definition at line 4361 of file X86ISelLowering.cpp.

References llvm::SDValue::getNode(), llvm::SDNode::getOperand(), llvm::SDNode::getSimpleValueType(), llvm::MVT::getSizeInBits(), and llvm::MVT::getVectorElementType().

Referenced by llvm::X86::isVINSERT128Index(), and llvm::X86::isVINSERT256Index().

isVPERM2X128Mask - Match 256-bit shuffles where the elements are considered as permutations between 128-bit chunks or halves. As an example: this shuffle bellow: vector_shuffle <4, 5, 6, 7, 12, 13, 14, 15> The first half comes from the second half of V1 and the second half from the the second half of V2.

Definition at line 4103 of file X86ISelLowering.cpp.

References llvm::MVT::getVectorNumElements(), llvm::MVT::is256BitVector(), and isSequentialOrUndefInRange().

isVPERMILPMask - Return true if the specified VECTOR_SHUFFLE operand specifies a shuffle of elements that is suitable for input to VPERMILPD*. Note that VPERMIL mask matching is different depending whether theunderlying type is 32 or 64. In the VPERMILPS the high half of the mask should point to the same elements of the low, but to the higher half of the source. In VPERMILPD the two lanes could be shuffled independently of each other with the same restriction that lanes can't be crossed. Also handles PSHUFDY.

Definition at line 4201 of file X86ISelLowering.cpp.

References llvm::MVT::getSizeInBits(), llvm::MVT::getVectorElementType(), llvm::MVT::getVectorNumElements(), isUndefOrEqual(), and isUndefOrInRange().

Definition at line 10122 of file X86ISelLowering.cpp.

References llvm::X86ISD::ADC, llvm::X86ISD::ADD, llvm::X86ISD::AND, llvm::X86ISD::CMP, llvm::X86ISD::COMI, llvm::X86ISD::DEC, llvm::SDValue::getNode(), llvm::SDNode::getOpcode(), llvm::SDValue::getResNo(), llvm::X86ISD::INC, llvm::X86ISD::OR, llvm::X86ISD::SAHF, llvm::X86ISD::SBB, llvm::X86ISD::SMUL, llvm::X86ISD::SUB, llvm::X86ISD::UCOMI, llvm::X86ISD::UMUL, and llvm::X86ISD::XOR.

Definition at line 10471 of file X86ISelLowering.cpp.

References llvm::dyn_cast(), llvm::ConstantSDNode::getAPIntValue(), llvm::SDValue::getOpcode(), llvm::SDValue::getOperand(), llvm::SDValue::hasOneUse(), llvm::X86ISD::SETCC, and llvm::ISD::XOR.

Definition at line 10147 of file X86ISelLowering.cpp.

References llvm::dyn_cast(), and llvm::ConstantSDNode::isNullValue().

Referenced by PerformAndCombine().

|

static |

isZeroShuffle - Returns true if N is a VECTOR_SHUFFLE that can be resolved to an zero vector. FIXME: move to dag combiner / method on ShuffleVectorSDNode

Definition at line 4687 of file X86ISelLowering.cpp.

References llvm::ISD::BUILD_VECTOR, llvm::ShuffleVectorSDNode::getMaskElt(), llvm::SDValue::getNode(), llvm::SDValue::getOpcode(), llvm::SDValue::getOperand(), llvm::SDNode::getOperand(), llvm::SDNode::getValueType(), llvm::EVT::getVectorNumElements(), llvm::ISD::isBuildVectorAllZeros(), llvm::X86::isZeroNode(), llvm::ISD::UNDEF, and llvm::NVPTX::PTXLdStInstCode::V2.

Referenced by NormalizeVectorShuffle().

|

static |

Definition at line 12390 of file X86ISelLowering.cpp.

References llvm::ISD::CONCAT_VECTORS, Extract128BitVector(), llvm::SelectionDAG::getNode(), llvm::SDValue::getOpcode(), llvm::SDValue::getOperand(), llvm::EVT::getSimpleVT(), llvm::SDValue::getValueType(), llvm::EVT::getVectorElementType(), llvm::EVT::getVectorNumElements(), llvm::MVT::getVectorVT(), llvm::EVT::is256BitVector(), and llvm::EVT::isInteger().

Referenced by LowerADD(), LowerMUL(), and LowerSUB().

|

static |

Definition at line 9804 of file X86ISelLowering.cpp.

References llvm::ISD::CONCAT_VECTORS, Extract128BitVector(), llvm::SelectionDAG::getNode(), llvm::SDValue::getOpcode(), llvm::SDValue::getOperand(), llvm::SDValue::getSimpleValueType(), llvm::MVT::getVectorElementType(), llvm::MVT::getVectorNumElements(), llvm::MVT::getVectorVT(), llvm::MVT::is256BitVector(), and llvm::ISD::SETCC.

Referenced by LowerVSETCC().

|

static |

Definition at line 12417 of file X86ISelLowering.cpp.

References llvm::SDValue::getValueType(), llvm::EVT::is256BitVector(), llvm::EVT::isInteger(), and Lower256IntArith().

Referenced by llvm::X86TargetLowering::LowerOperation().

|

static |

Definition at line 13296 of file X86ISelLowering.cpp.

References llvm::X86ISD::ADC, llvm::X86ISD::ADD, llvm::ISD::ADDC, llvm::ISD::ADDE, llvm::SDValue::getNode(), llvm::SelectionDAG::getNode(), llvm::SDValue::getOpcode(), llvm::SDValue::getOperand(), llvm::SelectionDAG::getTargetLoweringInfo(), llvm::SDNode::getValueType(), llvm::SelectionDAG::getVTList(), llvm::MVT::i32, llvm::TargetLoweringBase::isTypeLegal(), llvm_unreachable, llvm::X86ISD::SBB, llvm::X86ISD::SUB, llvm::ISD::SUBC, and llvm::ISD::SUBE.

Referenced by llvm::X86TargetLowering::LowerOperation().

|

static |

Definition at line 12086 of file X86ISelLowering.cpp.

References llvm::SDValue::getOperand().

Referenced by llvm::X86TargetLowering::LowerOperation().

|

static |

Definition at line 8944 of file X86ISelLowering.cpp.

References llvm::SDValue::getNode(), llvm::X86Subtarget::hasFp256(), and LowerAVXExtend().

Referenced by llvm::X86TargetLowering::LowerOperation().

|

static |

Definition at line 5315 of file X86ISelLowering.cpp.

References llvm::ISD::ADD, llvm::MVT::f32, llvm::SelectionDAG::getConstant(), llvm::SDValue::getConstantOperandVal(), llvm::SelectionDAG::getContext(), llvm::MachineFunction::getFrameInfo(), llvm::SelectionDAG::getLoad(), llvm::SelectionDAG::getMachineFunction(), llvm::SelectionDAG::getNode(), llvm::SDValue::getOperand(), llvm::MVT::getSizeInBits(), llvm::SelectionDAG::getUNDEF(), llvm::SDValue::getValueType(), llvm::MVT::getVectorNumElements(), llvm::SelectionDAG::getVectorShuffle(), llvm::EVT::getVectorVT(), llvm::MVT::i32, llvm::SelectionDAG::InferPtrAlignment(), llvm::SelectionDAG::isBaseWithConstantOffset(), llvm::MachineFrameInfo::isFixedObjectIndex(), llvm::ISD::isNormalLoad(), llvm::A64DB::LD, llvm::SmallVectorTemplateBase< T, isPodLike< T >::value >::push_back(), and llvm::MachineFrameInfo::setObjectAlignment().

|

static |

Definition at line 13147 of file X86ISelLowering.cpp.

References llvm::CrossThread, llvm::N86::ESP, llvm::SelectionDAG::getConstant(), llvm::SelectionDAG::getMachineNode(), llvm::SelectionDAG::getNode(), llvm::SDValue::getOperand(), llvm::SelectionDAG::getRegister(), llvm::SelectionDAG::getTargetConstant(), llvm::X86Subtarget::hasSSE2(), llvm::MVT::i32, llvm::MVT::i8, llvm::X86Subtarget::is64Bit(), llvm::X86ISD::MEMBARRIER, llvm::X86ISD::MFENCE, llvm::MVT::Other, and llvm::SequentiallyConsistent.

Referenced by llvm::X86TargetLowering::LowerOperation().

|

static |

Definition at line 13271 of file X86ISelLowering.cpp.

References llvm::ISD::ATOMIC_SWAP, llvm::SelectionDAG::getAtomic(), llvm::SDValue::getNode(), llvm::SDNode::getOperand(), llvm::SelectionDAG::getTargetLoweringInfo(), llvm::SDValue::getValue(), llvm::TargetLoweringBase::isTypeLegal(), and llvm::SequentiallyConsistent.

Referenced by llvm::X86TargetLowering::LowerOperation().

|

static |

Definition at line 6140 of file X86ISelLowering.cpp.

References Concat128BitVectors(), Concat256BitVectors(), llvm::SDValue::getOperand(), llvm::SDValue::getSimpleValueType(), llvm::MVT::getVectorNumElements(), llvm::MVT::is256BitVector(), llvm::MVT::is512BitVector(), and llvm::NVPTX::PTXLdStInstCode::V2.

Referenced by LowerCONCAT_VECTORS().

|

static |

Definition at line 8870 of file X86ISelLowering.cpp.

References llvm::ISD::BITCAST, llvm::ISD::CONCAT_VECTORS, llvm::SelectionDAG::getNode(), llvm::SDValue::getOpcode(), llvm::SDNode::getOperand(), llvm::SDValue::getSimpleValueType(), llvm::SDNode::getSimpleValueType(), llvm::SelectionDAG::getUNDEF(), getUnpackh(), getUnpackl(), llvm::MVT::getVectorElementType(), llvm::MVT::getVectorNumElements(), llvm::MVT::getVectorVT(), getZeroVector(), llvm::X86Subtarget::hasInt256(), llvm::RegState::Undef, llvm::MVT::v16i16, llvm::MVT::v16i8, llvm::MVT::v4i32, llvm::MVT::v4i64, llvm::MVT::v8i16, llvm::MVT::v8i32, llvm::X86ISD::VZEXT_MOVL, and llvm::ISD::ZERO_EXTEND.

Referenced by LowerANY_EXTEND(), and LowerZERO_EXTEND().

|

static |

Definition at line 13234 of file X86ISelLowering.cpp.

References llvm::SDValue::getOperand(), llvm::SDValue::getSimpleValueType(), llvm::MVT::getSizeInBits(), llvm::X86Subtarget::hasMMX(), llvm::X86Subtarget::hasSSE2(), llvm::MVT::i64, llvm::X86Subtarget::is64Bit(), and llvm::MVT::isVector().

Referenced by llvm::X86TargetLowering::LowerOperation().

|

static |

LowerBuildVectorv16i8 - Custom lower build_vector of v16i8.

Definition at line 5221 of file X86ISelLowering.cpp.

References llvm::ISD::BITCAST, llvm::SelectionDAG::getConstant(), llvm::SelectionDAG::getIntPtrConstant(), llvm::SelectionDAG::getNode(), llvm::SDValue::getOperand(), llvm::SelectionDAG::getUNDEF(), getZeroVector(), llvm::MVT::i16, llvm::MVT::i8, llvm::ISD::INSERT_VECTOR_ELT, llvm::ISD::OR, llvm::ISD::SHL, llvm::MVT::v16i8, llvm::MVT::v8i16, and llvm::ISD::ZERO_EXTEND.

|

static |

LowerBuildVectorv8i16 - Custom lower build_vector of v8i16.

Definition at line 5269 of file X86ISelLowering.cpp.

References llvm::SelectionDAG::getIntPtrConstant(), llvm::SelectionDAG::getNode(), llvm::SDValue::getOperand(), llvm::SelectionDAG::getUNDEF(), getZeroVector(), llvm::ISD::INSERT_VECTOR_ELT, and llvm::MVT::v8i16.

|

static |

Definition at line 13183 of file X86ISelLowering.cpp.

References llvm::A64CC::AL, llvm::array_lengthof(), llvm::N86::EAX, llvm::SelectionDAG::getCopyFromReg(), llvm::SelectionDAG::getCopyToReg(), llvm::SelectionDAG::getMemIntrinsicNode(), llvm::SDValue::getOperand(), llvm::EVT::getSimpleVT(), llvm::SelectionDAG::getTargetConstant(), llvm::SDValue::getValue(), llvm::SDValue::getValueType(), llvm::SelectionDAG::getVTList(), llvm::MVT::Glue, llvm::MVT::i32, llvm::MVT::i64, llvm::MVT::i8, llvm::X86Subtarget::is64Bit(), llvm::X86ISD::LCMPXCHG_DAG, llvm_unreachable, llvm::MVT::Other, llvm::MVT::SimpleTy, and T.

Referenced by llvm::X86TargetLowering::LowerOperation().

|

static |

Definition at line 6156 of file X86ISelLowering.cpp.

References llvm::SDValue::getNumOperands(), and LowerAVXCONCAT_VECTORS().

Referenced by llvm::X86TargetLowering::LowerOperation().

|

static |

Definition at line 12309 of file X86ISelLowering.cpp.

References llvm::array_lengthof(), llvm::X86ISD::BSR, llvm::X86ISD::CMOV, llvm::X86::COND_E, llvm::SelectionDAG::getConstant(), llvm::SelectionDAG::getNode(), llvm::SDValue::getOperand(), llvm::EVT::getSizeInBits(), llvm::SDValue::getValue(), llvm::SDValue::getValueType(), llvm::SelectionDAG::getVTList(), llvm::MVT::i32, llvm::MVT::i8, llvm::ISD::TRUNCATE, llvm::ISD::XOR, and llvm::ISD::ZERO_EXTEND.

Referenced by llvm::X86TargetLowering::LowerOperation().

|

static |

Definition at line 12343 of file X86ISelLowering.cpp.

References llvm::X86ISD::BSR, llvm::SelectionDAG::getConstant(), llvm::SelectionDAG::getNode(), llvm::SDValue::getOperand(), llvm::EVT::getSizeInBits(), llvm::SDValue::getValueType(), llvm::SelectionDAG::getVTList(), llvm::MVT::i32, llvm::MVT::i8, llvm::ISD::TRUNCATE, llvm::ISD::XOR, and llvm::ISD::ZERO_EXTEND.

Referenced by llvm::X86TargetLowering::LowerOperation().

|

static |

Definition at line 12368 of file X86ISelLowering.cpp.

References llvm::array_lengthof(), llvm::X86ISD::BSF, llvm::X86ISD::CMOV, llvm::X86::COND_E, llvm::SelectionDAG::getConstant(), llvm::SelectionDAG::getNode(), llvm::SDValue::getOperand(), llvm::EVT::getSizeInBits(), llvm::SDValue::getValue(), llvm::SDValue::getValueType(), llvm::SelectionDAG::getVTList(), llvm::MVT::i32, and llvm::MVT::i8.

Referenced by llvm::X86TargetLowering::LowerOperation().

|

static |

Definition at line 7880 of file X86ISelLowering.cpp.

References Extract128BitVector(), Extract256BitVector(), llvm::SDValue::getOperand(), llvm::SDValue::getSimpleValueType(), llvm::X86Subtarget::hasFp256(), llvm::MVT::is128BitVector(), llvm::MVT::is256BitVector(), and llvm::MVT::is512BitVector().

Referenced by llvm::X86TargetLowering::LowerOperation().

|

static |

Definition at line 7575 of file X86ISelLowering.cpp.

References Assert, llvm::ISD::AssertZext, llvm::ISD::BITCAST, llvm::ISD::EXTRACT_VECTOR_ELT, llvm::MVT::f32, llvm::SDValue::getNode(), llvm::SelectionDAG::getNode(), llvm::SDNode::getOpcode(), llvm::SDValue::getOperand(), llvm::SDValue::getSimpleValueType(), llvm::MVT::getSizeInBits(), llvm::SelectionDAG::getValueType(), llvm::SDNode::getValueType(), llvm::SDValue::hasOneUse(), llvm::MVT::i16, llvm::MVT::i32, llvm::MVT::i64, llvm::MVT::is128BitVector(), llvm::X86ISD::PEXTRB, llvm::X86ISD::PEXTRW, llvm::ISD::STORE, llvm::ISD::TRUNCATE, llvm::SDNode::use_begin(), and llvm::MVT::v4i32.

|

static |

Definition at line 9322 of file X86ISelLowering.cpp.

References llvm::ISD::AND, llvm::X86ISD::FGETSIGNx86, llvm::SelectionDAG::getConstant(), llvm::SelectionDAG::getNode(), llvm::SDValue::getOperand(), and llvm::SDValue::getSimpleValueType().

Referenced by llvm::X86TargetLowering::LowerOperation().

|

static |

Definition at line 9161 of file X86ISelLowering.cpp.

References llvm::ISD::CONCAT_VECTORS, llvm::SelectionDAG::getNode(), llvm::SDValue::getOperand(), llvm::SDValue::getSimpleValueType(), llvm::SelectionDAG::getUNDEF(), llvm::MVT::v2f32, llvm::MVT::v4f32, and llvm::X86ISD::VFPEXT.

Referenced by llvm::X86TargetLowering::LowerOperation().

|

static |

Definition at line 13322 of file X86ISelLowering.cpp.

References llvm::CallingConv::C, llvm::ISD::EXTRACT_VECTOR_ELT, llvm::MVT::f64, llvm::StructType::get(), llvm::VectorType::get(), llvm::SelectionDAG::getContext(), llvm::SelectionDAG::getEntryNode(), llvm::SelectionDAG::getExternalSymbol(), llvm::SDValue::getNode(), llvm::SDValue::getOperand(), llvm::TargetLoweringBase::getPointerTy(), llvm::SelectionDAG::getTargetLoweringInfo(), llvm::EVT::getTypeForEVT(), llvm::SDValue::getValueType(), llvm::X86Subtarget::is64Bit(), llvm::TargetLowering::ArgListEntry::isSExt, llvm::X86Subtarget::isTargetDarwin(), llvm::TargetLowering::ArgListEntry::isZExt, llvm::TargetLowering::LowerCallTo(), llvm::ISD::MERGE_VALUES, llvm::TargetLowering::ArgListEntry::Node, and llvm::TargetLowering::ArgListEntry::Ty.

Referenced by llvm::X86TargetLowering::LowerOperation().

|

static |

Definition at line 7906 of file X86ISelLowering.cpp.

References llvm::SDValue::getNode(), llvm::SDNode::getOperand(), llvm::SDNode::getSimpleValueType(), llvm::X86Subtarget::hasFp256(), Insert128BitVector(), Insert256BitVector(), llvm::MVT::is128BitVector(), llvm::MVT::is256BitVector(), and llvm::MVT::is512BitVector().

Referenced by llvm::X86TargetLowering::LowerOperation().

|

static |

Definition at line 7747 of file X86ISelLowering.cpp.

References llvm::ISD::ANY_EXTEND, llvm::MVT::f32, llvm::SelectionDAG::getIntPtrConstant(), llvm::SelectionDAG::getNode(), llvm::SDValue::getOperand(), llvm::SDValue::getSimpleValueType(), llvm::MVT::getSizeInBits(), llvm::SDValue::getValueType(), llvm::MVT::getVectorElementType(), llvm::MVT::i32, llvm::MVT::i64, llvm::X86ISD::INSERTPS, llvm::MVT::is128BitVector(), llvm::X86ISD::PINSRB, llvm::X86ISD::PINSRW, llvm::ISD::SCALAR_TO_VECTOR, llvm::MVT::v16i8, llvm::MVT::v4f32, and llvm::MVT::v8i16.

|

static |

Definition at line 11802 of file X86ISelLowering.cpp.

References llvm::ISD::ADD, llvm::array_lengthof(), llvm::X86ISD::CMOV, llvm::X86::COND_B, llvm::X86::COND_NE, llvm::N86::EBP, llvm::N86::ECX, llvm::X86ISD::EH_RETURN, llvm::X86ISD::EH_SJLJ_LONGJMP, llvm::X86ISD::EH_SJLJ_SETJMP, llvm::SelectionDAG::getConstant(), llvm::SelectionDAG::getCopyFromReg(), llvm::SelectionDAG::getCopyToReg(), llvm::SelectionDAG::getEntryNode(), llvm::MachineFunction::getFrameInfo(), llvm::X86RegisterInfo::getFrameRegister(), getGatherNode(), llvm::SelectionDAG::getIntPtrConstant(), llvm::SelectionDAG::getLoad(), llvm::SelectionDAG::getMachineFunction(), getMGatherNode(), getMScatterNode(), llvm::SDValue::getNode(), llvm::SelectionDAG::getNode(), llvm::SDValue::getOperand(), llvm::TargetLoweringBase::getPointerTy(), llvm::SelectionDAG::getRegister(), llvm::TargetMachine::getRegisterInfo(), llvm::X86TargetLowering::getReturnAddressFrameIndex(), getScatterNode(), llvm::X86RegisterInfo::getSlotSize(), llvm::SelectionDAG::getStore(), llvm::TargetLoweringBase::getTargetMachine(), llvm::SDValue::getValueType(), llvm::SDNode::getValueType(), llvm::SelectionDAG::getVTList(), llvm::SDNode::getVTList(), llvm::SelectionDAG::getZExtOrTrunc(), llvm::MVT::Glue, llvm::MVT::i32, llvm::MVT::i64, llvm::MVT::i8, llvm_unreachable, llvm::ISD::MERGE_VALUES, llvm::MVT::Other, llvm::X86ISD::RDRAND, llvm::X86ISD::RDSEED, llvm::AArch64ISD::Ret, llvm::X86ISD::SETCC, llvm::MachineFrameInfo::setFrameAddressIsTaken(), llvm::MachineFrameInfo::setReturnAddressIsTaken(), llvm::Intrinsic::x86_avx512_gather_dpd_512, llvm::Intrinsic::x86_avx512_gather_dpd_mask_512, llvm::Intrinsic::x86_avx512_gather_dpi_512, llvm::Intrinsic::x86_avx512_gather_dpi_mask_512, llvm::Intrinsic::x86_avx512_gather_dpq_512, llvm::Intrinsic::x86_avx512_gather_dpq_mask_512, llvm::Intrinsic::x86_avx512_gather_dps_512, llvm::Intrinsic::x86_avx512_gather_dps_mask_512, llvm::Intrinsic::x86_avx512_gather_qpd_512, llvm::Intrinsic::x86_avx512_gather_qpd_mask_512, llvm::Intrinsic::x86_avx512_gather_qpi_512, llvm::Intrinsic::x86_avx512_gather_qpi_mask_512, llvm::Intrinsic::x86_avx512_gather_qpq_512, llvm::Intrinsic::x86_avx512_gather_qpq_mask_512, llvm::Intrinsic::x86_avx512_gather_qps_512, llvm::Intrinsic::x86_avx512_gather_qps_mask_512, llvm::Intrinsic::x86_avx512_scatter_dpd_512, llvm::Intrinsic::x86_avx512_scatter_dpd_mask_512, llvm::Intrinsic::x86_avx512_scatter_dpi_512, llvm::Intrinsic::x86_avx512_scatter_dpi_mask_512, llvm::Intrinsic::x86_avx512_scatter_dpq_512, llvm::Intrinsic::x86_avx512_scatter_dpq_mask_512, llvm::Intrinsic::x86_avx512_scatter_dps_512, llvm::Intrinsic::x86_avx512_scatter_dps_mask_512, llvm::Intrinsic::x86_avx512_scatter_qpd_512, llvm::Intrinsic::x86_avx512_scatter_qpd_mask_512, llvm::Intrinsic::x86_avx512_scatter_qpi_512, llvm::Intrinsic::x86_avx512_scatter_qpi_mask_512, llvm::Intrinsic::x86_avx512_scatter_qpq_512, llvm::Intrinsic::x86_avx512_scatter_qpq_mask_512, llvm::Intrinsic::x86_avx512_scatter_qps_512, llvm::Intrinsic::x86_avx512_scatter_qps_mask_512, llvm::Intrinsic::x86_rdrand_16, llvm::Intrinsic::x86_rdrand_32, llvm::Intrinsic::x86_rdrand_64, llvm::Intrinsic::x86_rdseed_16, llvm::Intrinsic::x86_rdseed_32, llvm::Intrinsic::x86_rdseed_64, llvm::Intrinsic::x86_xtest, llvm::X86ISD::XTEST, and llvm::ISD::ZERO_EXTEND.

Referenced by llvm::X86TargetLowering::LowerOperation().

|

static |

Definition at line 11022 of file X86ISelLowering.cpp.