LLVM API Documentation

#include <TargetLowering.h>

Classes | |

| struct | AddrMode |

| struct | IntrinsicInfo |

| class | ValueTypeActionImpl |

Public Types | |

| enum | LegalizeAction { Legal, Promote, Expand, Custom } |

| enum | LegalizeTypeAction { TypeLegal, TypePromoteInteger, TypeExpandInteger, TypeSoftenFloat, TypeExpandFloat, TypeScalarizeVector, TypeSplitVector, TypeWidenVector } |

| enum | BooleanContent { UndefinedBooleanContent, ZeroOrOneBooleanContent, ZeroOrNegativeOneBooleanContent } |

| Enum that describes how the target represents true/false values. More... | |

| enum | SelectSupportKind { ScalarValSelect, ScalarCondVectorVal, VectorMaskSelect } |

| Enum that describes what type of support for selects the target has. More... | |

| typedef std::pair < LegalizeTypeAction, EVT > | LegalizeKind |

Public Member Functions | |

| TargetLoweringBase (const TargetMachine &TM, const TargetLoweringObjectFile *TLOF) | |

| NOTE: The constructor takes ownership of TLOF. More... | |

| virtual | ~TargetLoweringBase () |

| const TargetMachine & | getTargetMachine () const |

| const DataLayout * | getDataLayout () const |

| const TargetLoweringObjectFile & | getObjFileLowering () const |

| bool | isBigEndian () const |

| bool | isLittleEndian () const |

| virtual MVT | getPointerTy (uint32_t=0) const |

| unsigned | getPointerSizeInBits (uint32_t AS=0) const |

| unsigned | getPointerTypeSizeInBits (Type *Ty) const |

| virtual MVT | getScalarShiftAmountTy (EVT LHSTy) const |

| EVT | getShiftAmountTy (EVT LHSTy) const |

| virtual MVT | getVectorIdxTy () const |

| bool | isSelectExpensive () const |

| Return true if the select operation is expensive for this target. More... | |

| virtual bool | isSelectSupported (SelectSupportKind) const |

| virtual bool | shouldSplitVectorElementType (EVT) const |

| bool | isIntDivCheap () const |

| bool | isSlowDivBypassed () const |

| Returns true if target has indicated at least one type should be bypassed. More... | |

| const DenseMap< unsigned int, unsigned int > & | getBypassSlowDivWidths () const |

| bool | isPow2DivCheap () const |

| Return true if pow2 div is cheaper than a chain of srl/add/sra. More... | |

| bool | isJumpExpensive () const |

| bool | isPredictableSelectExpensive () const |

| virtual bool | isLoadBitCastBeneficial (EVT, EVT) const |

| virtual EVT | getSetCCResultType (LLVMContext &Context, EVT VT) const |

| virtual MVT::SimpleValueType | getCmpLibcallReturnType () const |

| BooleanContent | getBooleanContents (bool isVec) const |

| Sched::Preference | getSchedulingPreference () const |

| Return target scheduling preference. More... | |

| virtual Sched::Preference | getSchedulingPreference (SDNode *) const |

| virtual const TargetRegisterClass * | getRegClassFor (MVT VT) const |

| virtual const TargetRegisterClass * | getRepRegClassFor (MVT VT) const |

| virtual uint8_t | getRepRegClassCostFor (MVT VT) const |

| bool | isTypeLegal (EVT VT) const |

| const ValueTypeActionImpl & | getValueTypeActions () const |

| LegalizeTypeAction | getTypeAction (LLVMContext &Context, EVT VT) const |

| LegalizeTypeAction | getTypeAction (MVT VT) const |

| EVT | getTypeToTransformTo (LLVMContext &Context, EVT VT) const |

| EVT | getTypeToExpandTo (LLVMContext &Context, EVT VT) const |

| unsigned | getVectorTypeBreakdown (LLVMContext &Context, EVT VT, EVT &IntermediateVT, unsigned &NumIntermediates, MVT &RegisterVT) const |

| virtual bool | getTgtMemIntrinsic (IntrinsicInfo &, const CallInst &, unsigned) const |

| virtual bool | isFPImmLegal (const APFloat &, EVT) const |

| virtual bool | isShuffleMaskLegal (const SmallVectorImpl< int > &, EVT) const |

| virtual bool | canOpTrap (unsigned Op, EVT VT) const |

| virtual bool | isVectorClearMaskLegal (const SmallVectorImpl< int > &, EVT) const |

| LegalizeAction | getOperationAction (unsigned Op, EVT VT) const |

| bool | isOperationLegalOrCustom (unsigned Op, EVT VT) const |

| bool | isOperationLegalOrPromote (unsigned Op, EVT VT) const |

| bool | isOperationExpand (unsigned Op, EVT VT) const |

| bool | isOperationLegal (unsigned Op, EVT VT) const |

| Return true if the specified operation is legal on this target. More... | |

| LegalizeAction | getLoadExtAction (unsigned ExtType, MVT VT) const |

| bool | isLoadExtLegal (unsigned ExtType, EVT VT) const |

| Return true if the specified load with extension is legal on this target. More... | |

| LegalizeAction | getTruncStoreAction (MVT ValVT, MVT MemVT) const |

| bool | isTruncStoreLegal (EVT ValVT, EVT MemVT) const |

| LegalizeAction | getIndexedLoadAction (unsigned IdxMode, MVT VT) const |

| bool | isIndexedLoadLegal (unsigned IdxMode, EVT VT) const |

| Return true if the specified indexed load is legal on this target. More... | |

| LegalizeAction | getIndexedStoreAction (unsigned IdxMode, MVT VT) const |

| bool | isIndexedStoreLegal (unsigned IdxMode, EVT VT) const |

| Return true if the specified indexed load is legal on this target. More... | |

| LegalizeAction | getCondCodeAction (ISD::CondCode CC, MVT VT) const |

| bool | isCondCodeLegal (ISD::CondCode CC, MVT VT) const |

| Return true if the specified condition code is legal on this target. More... | |

| MVT | getTypeToPromoteTo (unsigned Op, MVT VT) const |

| EVT | getValueType (Type *Ty, bool AllowUnknown=false) const |

| MVT | getSimpleValueType (Type *Ty, bool AllowUnknown=false) const |

| Return the MVT corresponding to this LLVM type. See getValueType. More... | |

| virtual unsigned | getByValTypeAlignment (Type *Ty) const |

| MVT | getRegisterType (MVT VT) const |

| Return the type of registers that this ValueType will eventually require. More... | |

| MVT | getRegisterType (LLVMContext &Context, EVT VT) const |

| Return the type of registers that this ValueType will eventually require. More... | |

| unsigned | getNumRegisters (LLVMContext &Context, EVT VT) const |

| virtual bool | ShouldShrinkFPConstant (EVT) const |

| bool | hasTargetDAGCombine (ISD::NodeType NT) const |

| unsigned | getMaxStoresPerMemset (bool OptSize) const |

| Get maximum # of store operations permitted for llvm.memset. More... | |

| unsigned | getMaxStoresPerMemcpy (bool OptSize) const |

| Get maximum # of store operations permitted for llvm.memcpy. More... | |

| unsigned | getMaxStoresPerMemmove (bool OptSize) const |

| Get maximum # of store operations permitted for llvm.memmove. More... | |

| virtual bool | allowsUnalignedMemoryAccesses (EVT, bool *=0) const |

| Determine if the target supports unaligned memory accesses. More... | |

| virtual EVT | getOptimalMemOpType (uint64_t, unsigned, unsigned, bool, bool, bool, MachineFunction &) const |

| virtual bool | isSafeMemOpType (MVT) const |

| bool | usesUnderscoreSetJmp () const |

| Determine if we should use _setjmp or setjmp to implement llvm.setjmp. More... | |

| bool | usesUnderscoreLongJmp () const |

| Determine if we should use _longjmp or longjmp to implement llvm.longjmp. More... | |

| bool | supportJumpTables () const |

| Return whether the target can generate code for jump tables. More... | |

| int | getMinimumJumpTableEntries () const |

| unsigned | getStackPointerRegisterToSaveRestore () const |

| unsigned | getExceptionPointerRegister () const |

| unsigned | getExceptionSelectorRegister () const |

| unsigned | getJumpBufSize () const |

| unsigned | getJumpBufAlignment () const |

| unsigned | getMinStackArgumentAlignment () const |

| Return the minimum stack alignment of an argument. More... | |

| unsigned | getMinFunctionAlignment () const |

| Return the minimum function alignment. More... | |

| unsigned | getPrefFunctionAlignment () const |

| Return the preferred function alignment. More... | |

| unsigned | getPrefLoopAlignment () const |

| Return the preferred loop alignment. More... | |

| bool | getInsertFencesForAtomic () const |

| virtual bool | getStackCookieLocation (unsigned &, unsigned &) const |

| virtual unsigned | getMaximalGlobalOffset () const |

| virtual bool | isNoopAddrSpaceCast (unsigned SrcAS, unsigned DestAS) const |

| Returns true if a cast between SrcAS and DestAS is a noop. More... | |

| virtual void | resetOperationActions () |

| Reset the operation actions based on target options. More... | |

| virtual bool | GetAddrModeArguments (IntrinsicInst *, SmallVectorImpl< Value * > &, Type *&) const |

| virtual bool | isLegalAddressingMode (const AddrMode &AM, Type *Ty) const |

| virtual int | getScalingFactorCost (const AddrMode &AM, Type *Ty) const |

| Return the cost of the scaling factor used in the addressing mode represented by AM for this target, for a load/store of the specified type. More... | |

| virtual bool | isLegalICmpImmediate (int64_t) const |

| virtual bool | isLegalAddImmediate (int64_t) const |

| virtual bool | isTruncateFree (Type *, Type *) const |

| virtual bool | allowTruncateForTailCall (Type *, Type *) const |

| virtual bool | isTruncateFree (EVT, EVT) const |

| virtual bool | isZExtFree (Type *, Type *) const |

| virtual bool | isZExtFree (EVT, EVT) const |

| virtual bool | hasPairedLoad (Type *, unsigned &) const |

| virtual bool | hasPairedLoad (EVT, unsigned &) const |

| virtual bool | isZExtFree (SDValue Val, EVT VT2) const |

| virtual bool | isFNegFree (EVT VT) const |

| virtual bool | isFAbsFree (EVT VT) const |

| virtual bool | isFMAFasterThanFMulAndFAdd (EVT) const |

| virtual bool | isNarrowingProfitable (EVT, EVT) const |

| void | setLibcallName (RTLIB::Libcall Call, const char *Name) |

| Rename the default libcall routine name for the specified libcall. More... | |

| const char * | getLibcallName (RTLIB::Libcall Call) const |

| Get the libcall routine name for the specified libcall. More... | |

| void | setCmpLibcallCC (RTLIB::Libcall Call, ISD::CondCode CC) |

| ISD::CondCode | getCmpLibcallCC (RTLIB::Libcall Call) const |

| void | setLibcallCallingConv (RTLIB::Libcall Call, CallingConv::ID CC) |

| Set the CallingConv that should be used for the specified libcall. More... | |

| CallingConv::ID | getLibcallCallingConv (RTLIB::Libcall Call) const |

| Get the CallingConv that should be used for the specified libcall. More... | |

| LegalizeKind | getTypeConversion (LLVMContext &Context, EVT VT) const |

Helpers for TargetTransformInfo implementations | |

| int | InstructionOpcodeToISD (unsigned Opcode) const |

| Get the ISD node that corresponds to the Instruction class opcode. More... | |

| std::pair< unsigned, MVT > | getTypeLegalizationCost (Type *Ty) const |

| Estimate the cost of type-legalization and the legalized type. More... | |

Static Public Member Functions | |

| static ISD::NodeType | getExtendForContent (BooleanContent Content) |

Protected Attributes | |

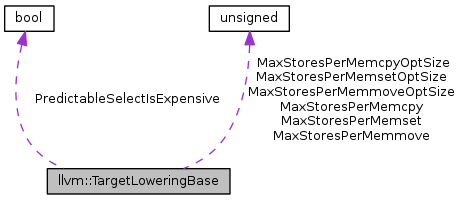

| unsigned | MaxStoresPerMemset |

| Specify maximum number of store instructions per memset call. More... | |

| unsigned | MaxStoresPerMemsetOptSize |

| unsigned | MaxStoresPerMemcpy |

| Specify maximum bytes of store instructions per memcpy call. More... | |

| unsigned | MaxStoresPerMemcpyOptSize |

| unsigned | MaxStoresPerMemmove |

| Specify maximum bytes of store instructions per memmove call. More... | |

| unsigned | MaxStoresPerMemmoveOptSize |

| bool | PredictableSelectIsExpensive |

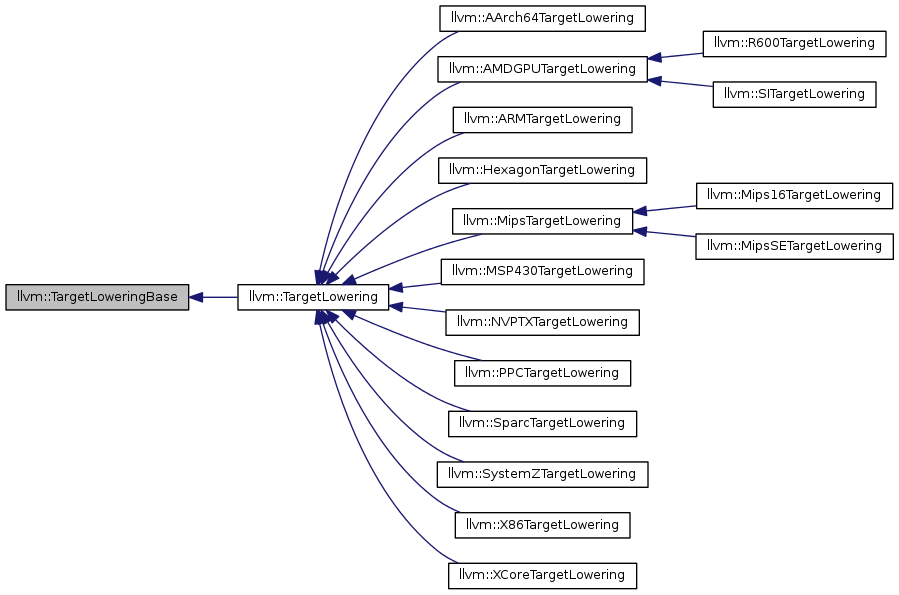

This base class for TargetLowering contains the SelectionDAG-independent parts that can be used from the rest of CodeGen.

Definition at line 73 of file TargetLowering.h.

| typedef std::pair<LegalizeTypeAction, EVT> llvm::TargetLoweringBase::LegalizeKind |

LegalizeKind holds the legalization kind that needs to happen to EVT in order to type-legalize it.

Definition at line 102 of file TargetLowering.h.

Enum that describes how the target represents true/false values.

| Enumerator | |

|---|---|

| UndefinedBooleanContent | |

| ZeroOrOneBooleanContent | |

| ZeroOrNegativeOneBooleanContent | |

Definition at line 105 of file TargetLowering.h.

This enum indicates whether operations are valid for a target, and if not, what action should be used to make them valid.

| Enumerator | |

|---|---|

| Legal | |

| Promote | |

| Expand | |

| Custom | |

Definition at line 80 of file TargetLowering.h.

This enum indicates whether a types are legal for a target, and if not, what action should be used to make them valid.

| Enumerator | |

|---|---|

| TypeLegal | |

| TypePromoteInteger | |

| TypeExpandInteger | |

| TypeSoftenFloat | |

| TypeExpandFloat | |

| TypeScalarizeVector | |

| TypeSplitVector | |

| TypeWidenVector | |

Definition at line 89 of file TargetLowering.h.

Enum that describes what type of support for selects the target has.

| Enumerator | |

|---|---|

| ScalarValSelect | |

| ScalarCondVectorVal | |

| VectorMaskSelect | |

Definition at line 112 of file TargetLowering.h.

|

explicit |

NOTE: The constructor takes ownership of TLOF.

Definition at line 660 of file TargetLoweringBase.cpp.

References llvm::Sched::ILP, initActions(), InitCmpLibcallCCs(), InitLibcallCallingConvs(), InitLibcallNames(), llvm::DataLayout::isLittleEndian(), MaxStoresPerMemcpy, MaxStoresPerMemcpyOptSize, MaxStoresPerMemmove, MaxStoresPerMemmoveOptSize, MaxStoresPerMemset, MaxStoresPerMemsetOptSize, PredictableSelectIsExpensive, and UndefinedBooleanContent.

|

virtual |

Definition at line 698 of file TargetLoweringBase.cpp.

|

inlineprotected |

Tells the code generator which bitwidths to bypass.

Definition at line 941 of file TargetLowering.h.

Referenced by llvm::X86TargetLowering::resetOperationActions().

|

inlineprotected |

If Opc/OrigVT is specified as being promoted, the promotion code defaults to trying a larger integer/fp until it can find one that works. If that default is insufficient, this method can be used by the target to override the default.

Definition at line 1051 of file TargetLowering.h.

References llvm::MVT::SimpleTy.

Referenced by llvm::AMDGPUTargetLowering::AMDGPUTargetLowering(), llvm::MipsTargetLowering::MipsTargetLowering(), llvm::PPCTargetLowering::PPCTargetLowering(), and llvm::X86TargetLowering::resetOperationActions().

|

inlineprotected |

Add the specified register class as an available regclass for the specified value type. This indicates the selector can handle values of that class natively.

Definition at line 952 of file TargetLowering.h.

References llvm::array_lengthof(), and llvm::MVT::SimpleTy.

Referenced by llvm::AArch64TargetLowering::AArch64TargetLowering(), llvm::MipsSETargetLowering::addMSAFloatType(), llvm::MipsSETargetLowering::addMSAIntType(), llvm::ARMTargetLowering::ARMTargetLowering(), llvm::HexagonTargetLowering::HexagonTargetLowering(), llvm::Mips16TargetLowering::Mips16TargetLowering(), llvm::MipsSETargetLowering::MipsSETargetLowering(), llvm::MSP430TargetLowering::MSP430TargetLowering(), llvm::NVPTXTargetLowering::NVPTXTargetLowering(), llvm::PPCTargetLowering::PPCTargetLowering(), llvm::R600TargetLowering::R600TargetLowering(), llvm::X86TargetLowering::resetOperationActions(), llvm::SITargetLowering::SITargetLowering(), llvm::SparcTargetLowering::SparcTargetLowering(), llvm::SystemZTargetLowering::SystemZTargetLowering(), and llvm::XCoreTargetLowering::XCoreTargetLowering().

|

inlinevirtual |

Determine if the target supports unaligned memory accesses.

This function returns true if the target allows unaligned memory accesses. of the specified type. If true, it also returns whether the unaligned memory access is "fast" in the second argument by reference. This is used, for example, in situations where an array copy/move/set is converted to a sequence of store operations. It's use helps to ensure that such replacements don't generate code that causes an alignment error (trap) on the target machine.

Reimplemented in llvm::X86TargetLowering, llvm::PPCTargetLowering, llvm::ARMTargetLowering, llvm::SystemZTargetLowering, llvm::SITargetLowering, llvm::MipsSETargetLowering, and llvm::Mips16TargetLowering.

Definition at line 717 of file TargetLowering.h.

Referenced by FindOptimalMemOpLowering().

|

inlinevirtual |

Return true if a truncation from Ty1 to Ty2 is permitted when deciding whether a call is in tail position. Typically this means that both results would be assigned to the same register or stack slot, but it could mean the target performs adequate checks of its own before proceeding with the tail call.

Reimplemented in llvm::X86TargetLowering, llvm::ARMTargetLowering, llvm::SystemZTargetLowering, and llvm::HexagonTargetLowering.

Definition at line 1181 of file TargetLowering.h.

Referenced by getNoopInput().

Returns true if the operation can trap for the value type.

VT must be a legal type. By default, we optimistically assume most operations don't trap except for divide and remainder.

canOpTrap - Returns true if the operation can trap for the value type. VT must be a legal type.

Definition at line 823 of file TargetLoweringBase.cpp.

References llvm::ISD::FDIV, llvm::ISD::FREM, isTypeLegal(), llvm::ISD::SDIV, llvm::ISD::SREM, llvm::ISD::UDIV, and llvm::ISD::UREM.

|

inlineprotected |

Remove all operation actions.

Definition at line 966 of file TargetLowering.h.

|

inlineprotected |

Remove all register classes.

Definition at line 959 of file TargetLowering.h.

References llvm::MVT::LAST_VALUETYPE, and llvm::Intrinsic::memset.

Referenced by llvm::Mips16TargetLowering::Mips16TargetLowering().

|

protected |

Once all of the register classes are added, this allows us to compute derived properties we expose.

computeRegisterProperties - Once all of the register classes are added, this allows us to compute derived properties we expose.

Definition at line 927 of file TargetLoweringBase.cpp.

References llvm::MVT::f128, llvm::MVT::f32, llvm::MVT::f64, findRepresentativeClass(), llvm::MVT::FIRST_VECTOR_VALUETYPE, llvm::MVT::getPow2VectorType(), llvm::MVT::getScalarType(), llvm::MVT::getSizeInBits(), llvm::MVT::getVectorElementType(), llvm::MVT::getVectorNumElements(), getVectorTypeBreakdownMVT(), llvm::MVT::i1, llvm::MVT::i128, llvm::MVT::i32, llvm::MVT::i64, llvm::MVT::isInteger(), isTypeLegal(), llvm::MVT::isVoid, llvm::MVT::LAST_INTEGER_VALUETYPE, llvm::MVT::LAST_VALUETYPE, llvm::MVT::LAST_VECTOR_VALUETYPE, llvm::MVT::MAX_ALLOWED_VALUETYPE, llvm::MVT::Other, llvm::MVT::ppcf128, llvm::MSP430ISD::RRC, llvm::TargetLoweringBase::ValueTypeActionImpl::setTypeAction(), shouldSplitVectorElementType(), llvm::tie(), TypeExpandFloat, TypeExpandInteger, TypePromoteInteger, TypeScalarizeVector, TypeSoftenFloat, TypeSplitVector, and TypeWidenVector.

Referenced by llvm::AArch64TargetLowering::AArch64TargetLowering(), llvm::ARMTargetLowering::ARMTargetLowering(), llvm::HexagonTargetLowering::HexagonTargetLowering(), llvm::Mips16TargetLowering::Mips16TargetLowering(), llvm::MipsSETargetLowering::MipsSETargetLowering(), llvm::MSP430TargetLowering::MSP430TargetLowering(), llvm::NVPTXTargetLowering::NVPTXTargetLowering(), llvm::PPCTargetLowering::PPCTargetLowering(), llvm::R600TargetLowering::R600TargetLowering(), llvm::X86TargetLowering::resetOperationActions(), llvm::SITargetLowering::SITargetLowering(), llvm::SparcTargetLowering::SparcTargetLowering(), llvm::SystemZTargetLowering::SystemZTargetLowering(), and llvm::XCoreTargetLowering::XCoreTargetLowering().

|

protectedvirtual |

Return the largest legal super-reg register class of the register class for the specified type and its associated "cost".

findRepresentativeClass - Return the largest legal super-reg register class of the register class for the specified type and its associated "cost".

Reimplemented in llvm::X86TargetLowering, and llvm::ARMTargetLowering.

Definition at line 900 of file TargetLoweringBase.cpp.

References llvm::TargetRegisterInfo::getNumRegClasses(), llvm::TargetRegisterInfo::getRegClass(), llvm::TargetMachine::getRegisterInfo(), llvm::TargetRegisterClass::getSize(), getTargetMachine(), isLegalRC(), llvm::SuperRegClassIterator::isValid(), llvm::BitVector::setBitsInMask(), and llvm::MVT::SimpleTy.

Referenced by computeRegisterProperties(), llvm::ARMTargetLowering::findRepresentativeClass(), and llvm::X86TargetLowering::findRepresentativeClass().

|

inlinevirtual |

CodeGenPrepare sinks address calculations into the same BB as Load/Store instructions reading the address. This allows as much computation as possible to be done in the address mode for that operand. This hook lets targets also pass back when this should be done on intrinsics which load/store.

Definition at line 1114 of file TargetLowering.h.

|

inline |

For targets without i1 registers, this gives the nature of the high-bits of boolean values held in types wider than i1.

"Boolean values" are special true/false values produced by nodes like SETCC and consumed (as the condition) by nodes like SELECT and BRCOND. Not to be confused with general values promoted from i1. Some cpus distinguish between vectors of boolean and scalars; the isVec parameter selects between the two kinds. For example on X86 a scalar boolean should be zero extended from i1, while the elements of a vector of booleans should be sign extended from i1.

Definition at line 240 of file TargetLowering.h.

Referenced by llvm::SelectionDAG::ComputeMaskedBits(), llvm::SelectionDAG::ComputeNumSignBits(), llvm::SelectionDAG::FoldSetCC(), and llvm::TargetLowering::SimplifySetCC().

|

inline |

Returns map of slow types for division or remainder with corresponding fast types

Definition at line 190 of file TargetLowering.h.

Return the desired alignment for ByVal aggregate function arguments in the caller parameter area. This is the actual alignment, not its logarithm.

getByValTypeAlignment - Return the desired alignment for ByVal aggregate function arguments in the caller parameter area. This is the actual alignment, not its logarithm.

Reimplemented in llvm::X86TargetLowering, and llvm::PPCTargetLowering.

Definition at line 1232 of file TargetLoweringBase.cpp.

References llvm::DataLayout::getCallFrameTypeAlignment().

Referenced by llvm::TargetLowering::LowerCallTo().

|

inline |

Get the CondCode that's to be used to test the result of the comparison libcall against zero.

Definition at line 1298 of file TargetLowering.h.

References llvm::Call.

Referenced by llvm::TargetLowering::softenSetCCOperands().

|

virtual |

Return the ValueType for comparison libcalls. Comparions libcalls include floating point comparion calls, and Ordered/Unordered check calls on floating point numbers.

Definition at line 1101 of file TargetLoweringBase.cpp.

References llvm::MVT::i32.

Referenced by llvm::TargetLowering::softenSetCCOperands().

|

inline |

Return how the condition code should be treated: either it is legal, needs to be expanded to some other code sequence, or the target has a custom expander for it.

Definition at line 533 of file TargetLowering.h.

References llvm::array_lengthof(), Promote, and llvm::MVT::SimpleTy.

Referenced by isCondCodeLegal(), and llvm::TargetLowering::SimplifySetCC().

|

inline |

Definition at line 146 of file TargetLowering.h.

Referenced by llvm::ComputeValueVTs(), llvm::SelectionDAG::CreateStackTemporary(), llvm::ARMSelectionDAGInfo::EmitTargetCodeForMemset(), FindOptimalMemOpLowering(), llvm::SelectionDAG::getConstantPool(), llvm::SelectionDAG::getMemcpy(), getMemcpyLoadsAndStores(), llvm::SelectionDAG::getMemmove(), getMemmoveLoadsAndStores(), llvm::SelectionDAG::getMemset(), getMemsetStores(), llvm::NVPTXTargetLowering::getPrototype(), llvm::SparcTargetLowering::getSRetArgSize(), llvm::AArch64TargetLowering::getTgtMemIntrinsic(), llvm::ARMTargetLowering::getTgtMemIntrinsic(), llvm::SelectionDAG::InferPtrAlignment(), llvm::NVPTXTargetLowering::LowerCall(), llvm::SelectionDAGBuilder::LowerCallTo(), llvm::TargetLowering::LowerCallTo(), llvm::NVPTXTargetLowering::LowerFormalArguments(), llvm::AArch64TargetLowering::LowerGlobalAddressELFSmall(), llvm::NVPTXTargetLowering::LowerReturn(), llvm::MSP430TargetLowering::MSP430TargetLowering(), llvm::TargetLowering::ParseConstraints(), llvm::PPCTargetLowering::PerformDAGCombine(), llvm::FunctionLoweringInfo::set(), llvm::TargetLowering::SimplifySetCC(), llvm::SelectionDAGBuilder::visitSPDescriptorParent(), llvm::X86TargetLowering::X86TargetLowering(), and XFormVExtractWithShuffleIntoLoad().

|

inline |

If a physical register, this returns the register that receives the exception address on entry to a landing pad.

Definition at line 779 of file TargetLowering.h.

|

inline |

If a physical register, this returns the register that receives the exception typeid on entry to a landing pad.

Definition at line 785 of file TargetLowering.h.

|

inlinestatic |

Definition at line 120 of file TargetLowering.h.

References llvm::ISD::ANY_EXTEND, llvm_unreachable, llvm::ISD::SIGN_EXTEND, UndefinedBooleanContent, llvm::ISD::ZERO_EXTEND, ZeroOrNegativeOneBooleanContent, and ZeroOrOneBooleanContent.

|

inline |

Return how the indexed load should be treated: either it is legal, needs to be promoted to a larger size, needs to be expanded to some other code sequence, or the target has a custom expander for it.

Definition at line 497 of file TargetLowering.h.

References llvm::ISD::LAST_INDEXED_MODE, llvm::MVT::LAST_VALUETYPE, and llvm::MVT::SimpleTy.

Referenced by isIndexedLoadLegal().

|

inline |

Return how the indexed store should be treated: either it is legal, needs to be promoted to a larger size, needs to be expanded to some other code sequence, or the target has a custom expander for it.

Definition at line 515 of file TargetLowering.h.

References llvm::ISD::LAST_INDEXED_MODE, llvm::MVT::LAST_VALUETYPE, and llvm::MVT::SimpleTy.

Referenced by isIndexedStoreLegal().

|

inline |

Return whether the DAG builder should automatically insert fences and reduce ordering for atomics.

Definition at line 823 of file TargetLowering.h.

|

inline |

Returns the target's jmp_buf alignment in bytes (if never set, the default is 0)

Definition at line 797 of file TargetLowering.h.

|

inline |

Returns the target's jmp_buf size in bytes (if never set, the default is 200)

Definition at line 791 of file TargetLowering.h.

|

inline |

Get the CallingConv that should be used for the specified libcall.

Definition at line 1308 of file TargetLowering.h.

References llvm::Call.

Referenced by llvm::ARMSelectionDAGInfo::EmitTargetCodeForMemset(), llvm::SelectionDAG::getMemcpy(), llvm::SelectionDAG::getMemmove(), llvm::SelectionDAG::getMemset(), llvm::AArch64TargetLowering::LowerF128ToCall(), and llvm::TargetLowering::makeLibCall().

|

inline |

Get the libcall routine name for the specified libcall.

Definition at line 1286 of file TargetLowering.h.

References llvm::Call.

Referenced by accumulateAndSortLibcalls(), llvm::ARMSelectionDAGInfo::EmitTargetCodeForMemset(), llvm::SelectionDAG::getMemcpy(), llvm::SelectionDAG::getMemmove(), llvm::SelectionDAG::getMemset(), isDivRemLibcallAvailable(), isSinCosLibcallAvailable(), LowerF128_FPEXTEND(), LowerF128_FPROUND(), llvm::AArch64TargetLowering::LowerF128ToCall(), LowerFP_TO_SINT(), LowerFP_TO_UINT(), llvm::SparcTargetLowering::LowerOperation(), LowerSINT_TO_FP(), LowerUINT_TO_FP(), llvm::TargetLowering::makeLibCall(), and llvm::SparcTargetLowering::ReplaceNodeResults().

|

inline |

Return how this load with extension should be treated: either it is legal, needs to be promoted to a larger size, needs to be expanded to some other code sequence, or the target has a custom expander for it.

Definition at line 464 of file TargetLowering.h.

References llvm::ISD::LAST_LOADEXT_TYPE, llvm::MVT::LAST_VALUETYPE, and llvm::MVT::SimpleTy.

Referenced by isLoadExtLegal().

|

inlinevirtual |

Returns the maximal possible offset which can be used for loads / stores from the global.

Reimplemented in llvm::ARMTargetLowering.

Definition at line 837 of file TargetLowering.h.

Get maximum # of store operations permitted for llvm.memcpy.

This function returns the maximum number of store operations permitted to replace a call to llvm.memcpy. The value is set by the target at the performance threshold for such a replacement. If OptSize is true, return the limit for functions that have OptSize attribute.

Definition at line 694 of file TargetLowering.h.

References MaxStoresPerMemcpy, and MaxStoresPerMemcpyOptSize.

Referenced by getMemcpyLoadsAndStores().

Get maximum # of store operations permitted for llvm.memmove.

This function returns the maximum number of store operations permitted to replace a call to llvm.memmove. The value is set by the target at the performance threshold for such a replacement. If OptSize is true, return the limit for functions that have OptSize attribute.

Definition at line 704 of file TargetLowering.h.

References MaxStoresPerMemmove, and MaxStoresPerMemmoveOptSize.

Referenced by getMemmoveLoadsAndStores().

Get maximum # of store operations permitted for llvm.memset.

This function returns the maximum number of store operations permitted to replace a call to llvm.memset. The value is set by the target at the performance threshold for such a replacement. If OptSize is true, return the limit for functions that have OptSize attribute.

Definition at line 684 of file TargetLowering.h.

References MaxStoresPerMemset, and MaxStoresPerMemsetOptSize.

Referenced by getMemsetStores().

|

inline |

Return the minimum function alignment.

Definition at line 807 of file TargetLowering.h.

Referenced by llvm::MachineFunction::MachineFunction().

|

inline |

Return integer threshold on number of blocks to use jump tables rather than if sequence.

Definition at line 767 of file TargetLowering.h.

|

inline |

Return the minimum stack alignment of an argument.

Definition at line 802 of file TargetLowering.h.

|

inline |

Return the number of registers that this ValueType will eventually require.

This is one for any types promoted to live in larger registers, but may be more than one for types (like i64) that are split into pieces. For types like i140, which are first promoted then expanded, it is the number of registers needed to hold all the bits of the original type. For an i140 on a 32 bit machine this means 5 registers.

Definition at line 646 of file TargetLowering.h.

References llvm::array_lengthof(), getRegisterType(), llvm::EVT::getSimpleVT(), llvm::MVT::getSizeInBits(), llvm::EVT::getSizeInBits(), getVectorTypeBreakdown(), llvm::EVT::isInteger(), llvm::EVT::isSimple(), llvm::EVT::isVector(), llvm_unreachable, and llvm::MVT::SimpleTy.

Referenced by llvm::FunctionLoweringInfo::ComputePHILiveOutRegInfo(), llvm::FunctionLoweringInfo::CreateRegs(), GetRegistersForValue(), llvm::GetReturnInfo(), llvm::NVPTXTargetLowering::LowerCall(), llvm::TargetLowering::LowerCallTo(), llvm::NVPTXTargetLowering::LowerFormalArguments(), and llvm::FunctionLoweringInfo::set().

|

inline |

Definition at line 147 of file TargetLowering.h.

Referenced by addPassesToGenerateCode(), llvm::AsmPrinter::getObjFileLowering(), and llvm::HexagonTargetLowering::LowerGLOBALADDRESS().

|

inline |

Return how this operation should be treated: either it is legal, needs to be promoted to a larger size, needs to be expanded to some other code sequence, or the target has a custom expander for it.

Definition at line 421 of file TargetLowering.h.

References llvm::array_lengthof(), Custom, Expand, llvm::EVT::getSimpleVT(), I, llvm::EVT::isExtended(), and llvm::MVT::SimpleTy.

Referenced by getTypeToPromoteTo(), isOperationExpand(), isOperationLegal(), isOperationLegalOrCustom(), and isOperationLegalOrPromote().

|

inlinevirtual |

Returns the target specific optimal type for load and store operations as a result of memset, memcpy, and memmove lowering.

If DstAlign is zero that means it's safe to destination alignment can satisfy any constraint. Similarly if SrcAlign is zero it means there isn't a need to check it against alignment requirement, probably because the source does not need to be loaded. If 'IsMemset' is true, that means it's expanding a memset. If 'ZeroMemset' is true, that means it's a memset of zero. 'MemcpyStrSrc' indicates whether the memcpy source is constant so it does not need to be loaded. It returns EVT::Other if the type should be determined using generic target-independent logic.

Reimplemented in llvm::X86TargetLowering, llvm::PPCTargetLowering, and llvm::ARMTargetLowering.

Definition at line 732 of file TargetLowering.h.

References llvm::MVT::Other.

Referenced by FindOptimalMemOpLowering().

| unsigned TargetLoweringBase::getPointerSizeInBits | ( | uint32_t | AS = 0 | ) | const |

Definition at line 801 of file TargetLoweringBase.cpp.

References llvm::DataLayout::getPointerSizeInBits().

Referenced by getPointerTy(), and getPointerTypeSizeInBits().

|

virtual |

Return the pointer type for the given address space, defaults to the pointer type from the data layout. FIXME: The default needs to be removed once all the code is updated.

Definition at line 797 of file TargetLoweringBase.cpp.

References llvm::MVT::getIntegerVT(), and getPointerSizeInBits().

Referenced by AddCombineToVPADDL(), llvm::X86TargetLowering::BuildFILD(), CheckType(), CheckValueType(), llvm::SelectionDAG::CreateStackTemporary(), llvm::PPCTargetLowering::emitEHSjLjLongJmp(), llvm::PPCTargetLowering::emitEHSjLjSetJmp(), llvm::X86SelectionDAGInfo::EmitTargetCodeForMemset(), llvm::ARMSelectionDAGInfo::EmitTargetCodeForMemset(), expandExp(), expandExp2(), expandPow(), ExpandUnalignedLoad(), ExpandUnalignedStore(), FindOptimalMemOpLowering(), getCopyFromParts(), GetExponent(), llvm::SelectionDAG::getIntPtrConstant(), llvm::SelectionDAG::getMemcpy(), llvm::SelectionDAG::getMemmove(), llvm::SelectionDAG::getMemset(), getNoopInput(), llvm::X86TargetLowering::getPICJumpTableRelocBase(), llvm::TargetLowering::getPICJumpTableRelocBase(), llvm::NVPTXTargetLowering::getPrototype(), llvm::FastISel::getRegForGEPIndex(), llvm::MSP430TargetLowering::getReturnAddressFrameIndex(), llvm::X86TargetLowering::getReturnAddressFrameIndex(), getSetCCResultType(), llvm::ARMTargetLowering::getSetCCResultType(), llvm::SelectionDAGBuilder::getValueImpl(), getValueType(), getVectorIdxTy(), InsertFenceForAtomic(), isBLACompatibleAddress(), llvm::MSP430TargetLowering::LowerBlockAddress(), llvm::HexagonTargetLowering::LowerBlockAddress(), llvm::AArch64TargetLowering::LowerBlockAddress(), llvm::HexagonTargetLowering::LowerBR_JT(), llvm::HexagonTargetLowering::LowerCall(), llvm::NVPTXTargetLowering::LowerCall(), llvm::AArch64TargetLowering::LowerCall(), llvm::SystemZTargetLowering::LowerCall(), llvm::SparcTargetLowering::LowerCall_32(), llvm::SparcTargetLowering::LowerCall_64(), llvm::SelectionDAGBuilder::LowerCallTo(), llvm::HexagonTargetLowering::LowerEH_RETURN(), llvm::MSP430TargetLowering::LowerExternalSymbol(), llvm::SparcTargetLowering::LowerF128_LibCallArg(), llvm::SparcTargetLowering::LowerF128Compare(), llvm::SparcTargetLowering::LowerF128Op(), llvm::AArch64TargetLowering::LowerF128ToCall(), llvm::NVPTXTargetLowering::LowerFormalArguments(), llvm::AArch64TargetLowering::LowerFormalArguments(), llvm::SystemZTargetLowering::LowerFormalArguments(), llvm::SparcTargetLowering::LowerFormalArguments_32(), llvm::SparcTargetLowering::LowerFormalArguments_64(), LowerFSINCOS(), llvm::AMDGPUTargetLowering::LowerGlobalAddress(), llvm::NVPTXTargetLowering::LowerGlobalAddress(), llvm::MSP430TargetLowering::LowerGlobalAddress(), llvm::HexagonTargetLowering::LowerGLOBALADDRESS(), llvm::AArch64TargetLowering::LowerGlobalAddressELFLarge(), llvm::AArch64TargetLowering::LowerGlobalAddressELFSmall(), llvm::SparcTargetLowering::LowerGlobalTLSAddress(), llvm::AArch64TargetLowering::LowerGlobalTLSAddress(), LowerINTRINSIC_W_CHAIN(), llvm::MSP430TargetLowering::LowerJumpTable(), llvm::AArch64TargetLowering::LowerJumpTable(), LowerMemOpCallTo(), llvm::SparcTargetLowering::LowerReturn_32(), llvm::MSP430TargetLowering::LowerRETURNADDR(), LowerRETURNADDR(), LowerSIGN_EXTEND_AVX512(), llvm::AArch64TargetLowering::LowerTLSDescCall(), llvm::MSP430TargetLowering::LowerVASTART(), llvm::AArch64TargetLowering::LowerVASTART(), LowerVASTART(), LowerVectorBroadcast(), LowerZERO_EXTEND_AVX512(), llvm::SparcTargetLowering::makeAddress(), llvm::TargetLowering::makeLibCall(), llvm::PPCTargetLowering::PerformDAGCombine(), PerformEXTRACT_VECTOR_ELTCombine(), PerformLOADCombine(), PerformSTORECombine(), PrepareCall(), llvm::AArch64TargetLowering::SaveVarArgRegisters(), llvm::PPCTargetLowering::SelectAddressRegImm(), llvm::SelectionDAGISel::SelectCodeCommon(), llvm::TargetLowering::SimplifySetCC(), llvm::SparcTargetLowering::SparcTargetLowering(), llvm::SystemZTargetLowering::SystemZTargetLowering(), llvm::SelectionDAGBuilder::visitBitTestHeader(), llvm::SelectionDAGBuilder::visitJumpTable(), llvm::SelectionDAGBuilder::visitJumpTableHeader(), and llvm::SelectionDAGBuilder::visitSPDescriptorParent().

Definition at line 805 of file TargetLoweringBase.cpp.

References llvm::Type::getPointerAddressSpace(), getPointerSizeInBits(), and llvm::Type::isPointerTy().

Referenced by llvm::SelectionDAG::getGlobalAddress(), and llvm::SelectionDAG::InferPtrAlignment().

|

inline |

Return the preferred function alignment.

Definition at line 812 of file TargetLowering.h.

Referenced by llvm::MachineFunction::MachineFunction().

|

inline |

Return the preferred loop alignment.

Definition at line 817 of file TargetLowering.h.

|

inlinevirtual |

Return the register class that should be used for the specified value type.

Reimplemented in llvm::ARMTargetLowering.

Definition at line 258 of file TargetLowering.h.

References llvm::MVT::SimpleTy.

Referenced by llvm::PPCTargetLowering::emitEHSjLjSetJmp(), llvm::FastISel::FastEmitInst_extractsubreg(), llvm::ARMTargetLowering::getRegClassFor(), llvm::AArch64TargetLowering::LowerFormalArguments(), llvm::SparcTargetLowering::LowerFormalArguments_64(), llvm::HexagonTargetLowering::LowerRETURNADDR(), llvm::AArch64TargetLowering::LowerRETURNADDR(), LowerRETURNADDR(), llvm::ResourcePriorityQueue::rawRegPressureDelta(), and llvm::ResourcePriorityQueue::scheduledNode().

Return the type of registers that this ValueType will eventually require.

Definition at line 612 of file TargetLowering.h.

References llvm::array_lengthof(), and llvm::MVT::SimpleTy.

Referenced by llvm::FunctionLoweringInfo::CreateRegs(), ExpandUnalignedLoad(), ExpandUnalignedStore(), getNumRegisters(), getRegisterType(), llvm::GetReturnInfo(), llvm::TargetLowering::getTypeForExtArgOrReturn(), getVectorTypeBreakdown(), getVectorTypeBreakdownMVT(), and llvm::TargetLowering::LowerCallTo().

|

inline |

Return the type of registers that this ValueType will eventually require.

Definition at line 618 of file TargetLowering.h.

References llvm::array_lengthof(), getRegisterType(), llvm::EVT::getSimpleVT(), getTypeToTransformTo(), getVectorTypeBreakdown(), llvm::EVT::isInteger(), llvm::EVT::isSimple(), llvm::EVT::isVector(), llvm_unreachable, and llvm::MVT::SimpleTy.

|

inlinevirtual |

Return the cost of the 'representative' register class for the specified value type.

Definition at line 278 of file TargetLowering.h.

References llvm::MVT::SimpleTy.

Referenced by GetCostForDef().

|

inlinevirtual |

Return the 'representative' register class for the specified value type.

The 'representative' register class is the largest legal super-reg register class for the register class of the value type. For example, on i386 the rep register class for i8, i16, and i32 are GR32; while the rep register class is GR64 on x86_64.

Reimplemented in llvm::MipsSETargetLowering.

Definition at line 271 of file TargetLowering.h.

References llvm::MVT::SimpleTy.

Referenced by GetCostForDef(), and llvm::MipsSETargetLowering::getRepRegClassFor().

Reimplemented in llvm::X86TargetLowering, llvm::PPCTargetLowering, llvm::MipsTargetLowering, llvm::SystemZTargetLowering, llvm::NVPTXTargetLowering, llvm::XCoreTargetLowering, llvm::SparcTargetLowering, llvm::MSP430TargetLowering, and llvm::SITargetLowering.

Definition at line 810 of file TargetLoweringBase.cpp.

References llvm::MVT::getIntegerVT(), and llvm::DataLayout::getPointerSize().

Referenced by getShiftAmountTy(), and getVShift().

|

inlinevirtual |

Return the cost of the scaling factor used in the addressing mode represented by AM for this target, for a load/store of the specified type.

If the AM is supported, the return value must be >= 0. If the AM is not supported, it returns a negative value. TODO: Handle pre/postinc as well.

Definition at line 1149 of file TargetLowering.h.

References isLegalAddressingMode().

|

inline |

Return target scheduling preference.

Definition at line 245 of file TargetLowering.h.

Referenced by llvm::createDefaultScheduler(), llvm::PPCTargetLowering::getSchedulingPreference(), and llvm::ScheduleDAGSDNodes::newSUnit().

|

inlinevirtual |

Some scheduler, e.g. hybrid, can switch to different scheduling heuristics for different nodes. This function returns the preference (or none) for the given node.

Reimplemented in llvm::PPCTargetLowering, and llvm::ARMTargetLowering.

Definition at line 252 of file TargetLowering.h.

References llvm::Sched::None.

|

virtual |

Return the ValueType of the result of SETCC operations. Also used to obtain the target's preferred type for the condition operand of SELECT and BRCOND nodes. In the case of BRCOND the argument passed is MVT::Other since there are no other operands to get a type hint from.

Reimplemented in llvm::X86TargetLowering, llvm::PPCTargetLowering, llvm::AArch64TargetLowering, llvm::ARMTargetLowering, llvm::MipsTargetLowering, llvm::SystemZTargetLowering, llvm::HexagonTargetLowering, llvm::NVPTXTargetLowering, llvm::SITargetLowering, and llvm::R600TargetLowering.

Definition at line 1096 of file TargetLoweringBase.cpp.

References getPointerTy(), llvm::EVT::isVector(), and llvm::MVT::SimpleTy.

Referenced by PerformSELECTCombine(), llvm::TargetLowering::softenSetCCOperands(), llvm::SelectionDAGBuilder::visitBitTestCase(), llvm::SelectionDAGBuilder::visitBitTestHeader(), llvm::SelectionDAGBuilder::visitJumpTableHeader(), and llvm::SelectionDAGBuilder::visitSPDescriptorParent().

Definition at line 814 of file TargetLoweringBase.cpp.

References getScalarShiftAmountTy(), llvm::EVT::isInteger(), and llvm::EVT::isVector().

Referenced by llvm::TargetLowering::BuildExactSDIV(), llvm::TargetLowering::BuildSDIV(), llvm::TargetLowering::BuildUDIV(), ExpandUnalignedLoad(), ExpandUnalignedStore(), llvm::SelectionDAG::getShiftAmountOperand(), LowerVECTOR_SHUFFLEv16i8(), llvm::TargetLowering::SimplifyDemandedBits(), and llvm::TargetLowering::SimplifySetCC().

|

inline |

Return the MVT corresponding to this LLVM type. See getValueType.

Definition at line 603 of file TargetLowering.h.

References llvm::EVT::getSimpleVT(), and getValueType().

Referenced by llvm::TargetLowering::ParseConstraints().

|

inlinevirtual |

Return true if the target stores stack protector cookies at a fixed offset in some non-standard address space, and populates the address space and offset as appropriate.

Reimplemented in llvm::X86TargetLowering.

Definition at line 830 of file TargetLowering.h.

Referenced by CreatePrologue().

|

inline |

If a physical register, this specifies the register that llvm.savestack/llvm.restorestack should save and restore.

Definition at line 773 of file TargetLowering.h.

Referenced by llvm::TargetInstrInfo::isSchedulingBoundary(), and llvm::HexagonTargetLowering::LowerDYNAMIC_STACKALLOC().

|

inline |

Definition at line 145 of file TargetLowering.h.

Referenced by llvm::SITargetLowering::AdjustInstrPostInstrSelection(), llvm::ARMTargetLowering::AdjustInstrPostInstrSelection(), llvm::AArch64TargetLowering::emitAtomicBinary(), llvm::PPCTargetLowering::EmitAtomicBinary(), llvm::AArch64TargetLowering::emitAtomicBinaryMinMax(), llvm::AArch64TargetLowering::emitAtomicCmpSwap(), llvm::PPCTargetLowering::emitEHSjLjLongJmp(), llvm::PPCTargetLowering::emitEHSjLjSetJmp(), llvm::AArch64TargetLowering::EmitF128CSEL(), llvm::SITargetLowering::EmitInstrWithCustomInserter(), llvm::SparcTargetLowering::EmitInstrWithCustomInserter(), llvm::XCoreTargetLowering::EmitInstrWithCustomInserter(), llvm::MSP430TargetLowering::EmitInstrWithCustomInserter(), llvm::MipsTargetLowering::EmitInstrWithCustomInserter(), llvm::ARMTargetLowering::EmitInstrWithCustomInserter(), llvm::PPCTargetLowering::EmitInstrWithCustomInserter(), llvm::X86TargetLowering::EmitInstrWithCustomInserter(), llvm::PPCTargetLowering::EmitPartwordAtomicBinary(), llvm::MSP430TargetLowering::EmitShiftInstr(), findRepresentativeClass(), llvm::X86TargetLowering::getJumpTableEncoding(), llvm::TargetLowering::getJumpTableEncoding(), llvm::MipsTargetLowering::getOpndList(), llvm::PPCTargetLowering::getRegForInlineAsmConstraint(), llvm::TargetLowering::getRegForInlineAsmConstraint(), llvm::X86TargetLowering::getReturnAddressFrameIndex(), llvm::ARMTargetLowering::getSchedulingPreference(), llvm::X86TargetLowering::getSetCCResultType(), llvm::X86TargetLowering::getStackCookieLocation(), llvm::AArch64TargetLowering::IsEligibleForTailCallOptimization(), llvm::isInTailCallPosition(), llvm::X86TargetLowering::isLegalAddressingMode(), llvm::TargetLowering::isOffsetFoldingLegal(), llvm::X86TargetLowering::LowerAsmOperandForConstraint(), llvm::AArch64TargetLowering::LowerBlockAddress(), llvm::HexagonTargetLowering::LowerCall(), llvm::AArch64TargetLowering::LowerCall(), llvm::SparcTargetLowering::LowerCall_32(), llvm::SparcTargetLowering::LowerCall_64(), llvm::HexagonTargetLowering::LowerCallResult(), llvm::AArch64TargetLowering::LowerCallResult(), llvm::X86TargetLowering::LowerCustomJumpTableEntry(), llvm::R600TargetLowering::LowerFormalArguments(), llvm::SITargetLowering::LowerFormalArguments(), llvm::HexagonTargetLowering::LowerFormalArguments(), llvm::AArch64TargetLowering::LowerFormalArguments(), llvm::SparcTargetLowering::LowerFormalArguments_32(), llvm::SparcTargetLowering::LowerFormalArguments_64(), llvm::AMDGPUTargetLowering::LowerGlobalAddress(), llvm::HexagonTargetLowering::LowerGLOBALADDRESS(), llvm::AArch64TargetLowering::LowerGlobalAddressELF(), llvm::AArch64TargetLowering::LowerGlobalAddressELFLarge(), llvm::AArch64TargetLowering::LowerGlobalAddressELFSmall(), llvm::SparcTargetLowering::LowerGlobalTLSAddress(), llvm::AArch64TargetLowering::LowerGlobalTLSAddress(), LowerINTRINSIC_W_CHAIN(), llvm::AArch64TargetLowering::LowerJumpTable(), llvm::HexagonTargetLowering::LowerReturn(), llvm::AArch64TargetLowering::LowerReturn(), llvm::AArch64TargetLowering::LowerTLSDescCall(), llvm::SparcTargetLowering::makeAddress(), llvm::PPCTargetLowering::PerformDAGCombine(), llvm::SITargetLowering::PostISelFolding(), llvm::PPCTargetLowering::ReplaceNodeResults(), llvm::X86TargetLowering::resetOperationActions(), and llvm::ResourcePriorityQueue::ResourcePriorityQueue().

|

inlinevirtual |

Given an intrinsic, checks if on the target the intrinsic will need to map to a MemIntrinsicNode (touches memory). If this is the case, it returns true and store the intrinsic information into the IntrinsicInfo that was passed to the function.

Reimplemented in llvm::ARMTargetLowering, llvm::AArch64TargetLowering, llvm::AMDGPUTargetLowering, and llvm::NVPTXTargetLowering.

Definition at line 383 of file TargetLowering.h.

|

inline |

Return how this store with truncation should be treated: either it is legal, needs to be promoted to a larger size, needs to be expanded to some other code sequence, or the target has a custom expander for it.

Definition at line 479 of file TargetLowering.h.

References llvm::MVT::LAST_VALUETYPE, and llvm::MVT::SimpleTy.

Referenced by isTruncStoreLegal().

|

inline |

Return how we should legalize values of this type, either it is already legal (return 'Legal') or we need to promote it to a larger type (return 'Promote'), or we need to expand it into multiple registers of smaller integer type (return 'Expand'). 'Custom' is not an option.

Definition at line 319 of file TargetLowering.h.

References getTypeConversion().

Referenced by llvm::SelectionDAG::getConstant(), getTypeToExpandTo(), getVectorTypeBreakdown(), and OptimizeNoopCopyExpression().

|

inline |

Definition at line 322 of file TargetLowering.h.

References llvm::TargetLoweringBase::ValueTypeActionImpl::getTypeAction().

|

inline |

Definition at line 1473 of file TargetLowering.h.

References llvm::array_lengthof(), llvm::EVT::getIntegerVT(), llvm::EVT::getPow2VectorType(), llvm::EVT::getRoundIntegerType(), llvm::EVT::getSimpleVT(), llvm::EVT::getSizeInBits(), llvm::TargetLoweringBase::ValueTypeActionImpl::getTypeAction(), llvm::MVT::getVectorElementType(), llvm::EVT::getVectorElementType(), llvm::MVT::getVectorNumElements(), llvm::EVT::getVectorNumElements(), llvm::MVT::getVectorVT(), llvm::EVT::getVectorVT(), llvm::EVT::isInteger(), llvm::EVT::isPow2VectorType(), llvm::isPowerOf2_32(), llvm::EVT::isSimple(), llvm::EVT::isVector(), llvm::NextPowerOf2(), llvm::MVT::SimpleTy, TypeExpandInteger, TypeLegal, TypePromoteInteger, TypeScalarizeVector, TypeSplitVector, and TypeWidenVector.

Referenced by getTypeAction(), getTypeLegalizationCost(), and getTypeToTransformTo().

Estimate the cost of type-legalization and the legalized type.

Definition at line 1312 of file TargetLoweringBase.cpp.

References llvm::CallingConv::C, llvm::Type::getContext(), llvm::EVT::getSimpleVT(), getTypeConversion(), getValueType(), TypeExpandInteger, TypeLegal, and TypeSplitVector.

|

inline |

For types supported by the target, this is an identity function. For types that must be expanded (i.e. integer types that are larger than the largest integer register or illegal floating point types), this returns the largest legal type it will be expanded to.

Definition at line 340 of file TargetLowering.h.

References getTypeAction(), getTypeToTransformTo(), llvm::EVT::isVector(), llvm_unreachable, TypeExpandInteger, and TypeLegal.

If the action for this operation is to promote, this method returns the ValueType to promote to.

Definition at line 555 of file TargetLowering.h.

References getOperationAction(), llvm::MVT::isFloatingPoint(), llvm::MVT::isInteger(), isTypeLegal(), llvm::MVT::isVoid, Promote, and llvm::MVT::SimpleTy.

|

inline |

For types supported by the target, this is an identity function. For types that must be promoted to larger types, this returns the larger type to promote to. For integer types that are larger than the largest integer register, this contains one step in the expansion to get to the smaller register. For illegal floating point types, this returns the integer type to transform to.

Definition at line 332 of file TargetLowering.h.

References getTypeConversion().

Referenced by llvm::FunctionLoweringInfo::ComputePHILiveOutRegInfo(), llvm::SelectionDAG::getConstant(), getMemcpyLoadsAndStores(), llvm::FastISel::getRegForValue(), getRegisterType(), llvm::SelectionDAG::GetSplitDestVTs(), getTypeToExpandTo(), getVectorTypeBreakdown(), and OptimizeNoopCopyExpression().

Return the EVT corresponding to this LLVM type. This is fixed by the LLVM operations except for the pointer size. If AllowUnknown is true, this will return MVT::Other for types with no EVT counterpart (e.g. structs), otherwise it will assert.

Definition at line 582 of file TargetLowering.h.

References llvm::Type::getContext(), llvm::SequentialType::getElementType(), llvm::EVT::getEVT(), llvm::VectorType::getNumElements(), getPointerTy(), llvm::EVT::getTypeForEVT(), llvm::EVT::getVectorVT(), and llvm::Type::isVectorTy().

Referenced by CompactSwizzlableVector(), llvm::ComputeValueVTs(), llvm::NVPTXTargetLowering::getPrototype(), llvm::FastISel::getRegForValue(), getSimpleValueType(), llvm::NVPTXTargetLowering::getTgtMemIntrinsic(), getTypeLegalizationCost(), llvm::SelectionDAGBuilder::getValueImpl(), llvm::ARMTargetLowering::isLegalAddressingMode(), llvm::NVPTXTargetLowering::LowerCall(), llvm::TargetLowering::LowerCallTo(), llvm::NVPTXTargetLowering::LowerFormalArguments(), llvm::NVPTXTargetLowering::LowerReturn(), OptimizeNoopCopyExpression(), llvm::X86TargetLowering::ReplaceNodeResults(), and llvm::FastISel::SelectOperator().

|

inline |

Definition at line 311 of file TargetLowering.h.

|

inlinevirtual |

Returns the type to be used for the index operand of: ISD::INSERT_VECTOR_ELT, ISD::EXTRACT_VECTOR_ELT, ISD::INSERT_SUBVECTOR, and ISD::EXTRACT_SUBVECTOR

Reimplemented in llvm::AMDGPUTargetLowering.

Definition at line 165 of file TargetLowering.h.

References getPointerTy().

Referenced by BuildVectorFromScalar(), getCopyFromPartsVector(), llvm::SelectionDAG::SplitVector(), and llvm::SelectionDAG::UnrollVectorOp().

| unsigned TargetLoweringBase::getVectorTypeBreakdown | ( | LLVMContext & | Context, |

| EVT | VT, | ||

| EVT & | IntermediateVT, | ||

| unsigned & | NumIntermediates, | ||

| MVT & | RegisterVT | ||

| ) | const |

Vector types are broken down into some number of legal first class types. For example, EVT::v8f32 maps to 2 EVT::v4f32 with Altivec or SSE1, or 8 promoted EVT::f64 values with the X86 FP stack. Similarly, EVT::v2i64 turns into 4 EVT::i32 values with both PPC and X86.

This method returns the number of registers needed, and the VT for each register. It also returns the VT and quantity of the intermediate values before they are promoted/expanded.

getVectorTypeBreakdown - Vector types are broken down into some number of legal first class types. For example, MVT::v8f32 maps to 2 MVT::v4f32 with Altivec or SSE1, or 8 promoted MVT::f64 values with the X86 FP stack. Similarly, MVT::v2i64 turns into 4 MVT::i32 values with both PPC and X86.

This method returns the number of registers needed, and the VT for each register. It also returns the VT and quantity of the intermediate values before they are promoted/expanded.

Definition at line 1114 of file TargetLoweringBase.cpp.

References getRegisterType(), llvm::EVT::getSimpleVT(), llvm::MVT::getSizeInBits(), llvm::EVT::getSizeInBits(), getTypeAction(), getTypeToTransformTo(), llvm::EVT::getVectorElementType(), llvm::EVT::getVectorNumElements(), llvm::EVT::getVectorVT(), llvm::isPowerOf2_32(), isTypeLegal(), llvm::NextPowerOf2(), llvm::X86II::TA, TypePromoteInteger, and TypeWidenVector.

Referenced by getCopyFromPartsVector(), getNumRegisters(), and getRegisterType().

Return true if the target supplies and combines to a paired load two loaded values of type LoadedType next to each other in memory. RequiredAlignment gives the minimal alignment constraints that must be met to be able to select this paired load.

This information is not used to generate actual paired loads, but it is used to generate a sequence of loads that is easier to combine into a paired load. For instance, something like this: a = load i64* addr b = trunc i64 a to i32 c = lshr i64 a, 32 d = trunc i64 c to i32 will be optimized into: b = load i32* addr1 d = load i32* addr2 Where addr1 = addr2 +/- sizeof(i32).

In other words, unless the target performs a post-isel load combining, this information should not be provided because it will generate more loads.

Definition at line 1226 of file TargetLowering.h.

Definition at line 1231 of file TargetLowering.h.

|

inline |

If true, the target has custom DAG combine transformations that it can perform for the specified node.

Definition at line 673 of file TargetLowering.h.

References llvm::array_lengthof().

|

protected |

Initialize all of the actions to default values.

Definition at line 702 of file TargetLoweringBase.cpp.

References llvm::array_lengthof(), llvm::ISD::CONCAT_VECTORS, llvm::ISD::ConstantFP, llvm::ISD::DEBUGTRAP, Expand, llvm::MVT::f128, llvm::MVT::f16, llvm::MVT::f32, llvm::MVT::f64, llvm::MVT::f80, llvm::ISD::FCEIL, llvm::ISD::FCOPYSIGN, llvm::ISD::FEXP, llvm::ISD::FEXP2, llvm::ISD::FFLOOR, llvm::ISD::FGETSIGN, llvm::MVT::FIRST_VECTOR_VALUETYPE, llvm::ISD::FLOG, llvm::ISD::FLOG10, llvm::ISD::FLOG2, llvm::ISD::FNEARBYINT, llvm::ISD::FRINT, llvm::ISD::FROUND, llvm::ISD::FTRUNC, llvm::ISD::LAST_INDEXED_MODE, llvm::MVT::LAST_VALUETYPE, llvm::MVT::LAST_VECTOR_VALUETYPE, llvm::Intrinsic::memset, llvm::MVT::Other, llvm::ISD::PRE_INC, llvm::ISD::PREFETCH, setIndexedLoadAction(), setIndexedStoreAction(), setOperationAction(), and llvm::ISD::TRAP.

Referenced by llvm::X86TargetLowering::resetOperationActions(), and TargetLoweringBase().

| int TargetLoweringBase::InstructionOpcodeToISD | ( | unsigned | Opcode | ) | const |

Get the ISD node that corresponds to the Instruction class opcode.

Definition at line 1240 of file TargetLoweringBase.cpp.

References llvm::ISD::ADD, llvm::ISD::ADDRSPACECAST, llvm::ISD::AND, llvm::APIntOps::And(), llvm::ISD::BITCAST, llvm::Call, llvm::ISD::EXTRACT_VECTOR_ELT, ExtractElement(), llvm::ISD::FADD, llvm::ISD::FDIV, llvm::ISD::FMUL, llvm::ISD::FP_EXTEND, llvm::ISD::FP_ROUND, llvm::ISD::FP_TO_SINT, llvm::ISD::FP_TO_UINT, llvm::ISD::FREM, llvm::ISD::FSUB, llvm::ISD::INSERT_VECTOR_ELT, llvm_unreachable, llvm::SPII::Load, llvm::ISD::LOAD, llvm::ISD::MERGE_VALUES, llvm::ISD::MUL, llvm::ISD::OR, llvm::APIntOps::Or(), llvm::TargetOpcode::PHI, llvm::AArch64ISD::Ret, llvm::MCID::Select, llvm::ISD::SELECT, llvm::ISD::SETCC, llvm::ISD::SHL, llvm::ISD::SIGN_EXTEND, llvm::ISD::SINT_TO_FP, llvm::ISD::SRA, llvm::ISD::SREM, llvm::ISD::SRL, llvm::SPII::Store, llvm::ISD::STORE, llvm::ISD::SUB, llvm::ISD::TRUNCATE, llvm::ISD::UDIV, llvm::ISD::UINT_TO_FP, llvm::ISD::UREM, llvm::ISD::VECTOR_SHUFFLE, llvm::ISD::XOR, llvm::APIntOps::Xor(), and llvm::ISD::ZERO_EXTEND.

|

inline |

Definition at line 149 of file TargetLowering.h.

Referenced by llvm::SelectionDAG::getConstant(), getCopyFromParts(), getCopyToParts(), isExtendedBUILD_VECTOR(), and SkipExtensionForVMULL().

|

inline |

Return true if the specified condition code is legal on this target.

Definition at line 546 of file TargetLowering.h.

References Custom, getCondCodeAction(), and Legal.

Referenced by llvm::SelectionDAG::FoldSetCC(), llvm::R600TargetLowering::PerformDAGCombine(), and llvm::TargetLowering::SimplifySetCC().

Return true if an fabs operation is free to the point where it is never worthwhile to replace it with a bitwise operation.

Reimplemented in llvm::AMDGPUTargetLowering.

Definition at line 1252 of file TargetLowering.h.

References llvm::EVT::isFloatingPoint().

Return true if an FMA operation is faster than a pair of fmul and fadd instructions. fmuladd intrinsics will be expanded to FMAs when this method returns true, otherwise fmuladd is expanded to fmul + fadd.

NOTE: This may be called before legalization on types for which FMAs are not legal, but should return true if those types will eventually legalize to types that support FMAs. After legalization, it will only be called on types that support FMAs (via Legal or Custom actions)

Reimplemented in llvm::X86TargetLowering, llvm::PPCTargetLowering, llvm::AArch64TargetLowering, llvm::SystemZTargetLowering, and llvm::SITargetLowering.

Definition at line 1265 of file TargetLowering.h.

Return true if an fneg operation is free to the point where it is never worthwhile to replace it with a bitwise operation.

Reimplemented in llvm::AMDGPUTargetLowering.

Definition at line 1245 of file TargetLowering.h.

References llvm::EVT::isFloatingPoint().

Returns true if the target can instruction select the specified FP immediate natively. If false, the legalizer will materialize the FP immediate as a load from a constant pool.

Reimplemented in llvm::X86TargetLowering, llvm::ARMTargetLowering, llvm::SystemZTargetLowering, llvm::HexagonTargetLowering, and llvm::AMDGPUTargetLowering.

Definition at line 391 of file TargetLowering.h.

Return true if the specified indexed load is legal on this target.

Definition at line 505 of file TargetLowering.h.

References Custom, getIndexedLoadAction(), llvm::EVT::getSimpleVT(), llvm::EVT::isSimple(), and Legal.

Return true if the specified indexed load is legal on this target.

Definition at line 523 of file TargetLowering.h.

References Custom, getIndexedStoreAction(), llvm::EVT::getSimpleVT(), llvm::EVT::isSimple(), and Legal.

|

inline |

Return true if integer divide is usually cheaper than a sequence of several shifts, adds, and multiplies for this target.

Definition at line 183 of file TargetLowering.h.

|

inline |

Return true if Flow Control is an expensive operation that should be avoided.

Definition at line 199 of file TargetLowering.h.

|

inlinevirtual |

Return true if the specified immediate is legal add immediate, that is the target has add instructions which can add a register with the immediate without having to materialize the immediate into a register.

Reimplemented in llvm::X86TargetLowering, and llvm::ARMTargetLowering.

Definition at line 1165 of file TargetLowering.h.

Return true if the addressing mode represented by AM is legal for this target, for a load/store of the specified type.

The type may be VoidTy, in which case only return true if the addressing mode is legal for a load/store of any legal type. TODO: Handle pre/postinc as well.

isLegalAddressingMode - Return true if the addressing mode represented by AM is legal for this target, for a load/store of the specified type.

Reimplemented in llvm::X86TargetLowering, llvm::PPCTargetLowering, llvm::ARMTargetLowering, llvm::SystemZTargetLowering, llvm::HexagonTargetLowering, llvm::XCoreTargetLowering, and llvm::NVPTXTargetLowering.

Definition at line 1340 of file TargetLoweringBase.cpp.

References llvm::TargetLoweringBase::AddrMode::BaseGV, llvm::TargetLoweringBase::AddrMode::BaseOffs, llvm::TargetLoweringBase::AddrMode::HasBaseReg, and llvm::TargetLoweringBase::AddrMode::Scale.

Referenced by canFoldInAddressingMode(), and getScalingFactorCost().

|

inlinevirtual |

Return true if the specified immediate is legal icmp immediate, that is the target has icmp instructions which can compare a register against the immediate without having to materialize the immediate into a register.

Reimplemented in llvm::X86TargetLowering, llvm::ARMTargetLowering, llvm::AArch64TargetLowering, and llvm::HexagonTargetLowering.

Definition at line 1158 of file TargetLowering.h.

Referenced by llvm::TargetLowering::SimplifySetCC().

|

protected |

Return true if the value types that can be represented by the specified register class are all legal.

isLegalRC - Return true if the value types that can be represented by the specified register class are all legal.

Definition at line 888 of file TargetLoweringBase.cpp.

References I, isTypeLegal(), llvm::TargetRegisterClass::vt_begin(), and llvm::TargetRegisterClass::vt_end().

Referenced by findRepresentativeClass(), and llvm::TargetLowering::getRegForInlineAsmConstraint().

|

inline |

Definition at line 150 of file TargetLowering.h.

Referenced by llvm::ARMTargetLowering::allowsUnalignedMemoryAccesses(), ExpandUnalignedLoad(), ExpandUnalignedStore(), getMemsetStringVal(), ShrinkLoadReplaceStoreWithStore(), and llvm::TargetLowering::SimplifySetCC().

isLoadBitCastBeneficial() - Return true if the following transform is beneficial. fold (conv (load x)) -> (load (conv*)x) On architectures that don't natively support some vector loads efficiently, casting the load to a smaller vector of larger types and loading is more efficient, however, this can be undone by optimizations in dag combiner.

Reimplemented in llvm::AMDGPUTargetLowering.

Definition at line 214 of file TargetLowering.h.

Return true if the specified load with extension is legal on this target.

Definition at line 471 of file TargetLowering.h.

References getLoadExtAction(), llvm::EVT::getSimpleVT(), llvm::EVT::isSimple(), and Legal.

Return true if it's profitable to narrow operations of type VT1 to VT2. e.g. on x86, it's profitable to narrow from i32 to i8 but not from i32 to i16.

Reimplemented in llvm::X86TargetLowering.

Definition at line 1272 of file TargetLowering.h.

|

inlinevirtual |

Returns true if a cast between SrcAS and DestAS is a noop.

Reimplemented in llvm::X86TargetLowering.

Definition at line 842 of file TargetLowering.h.

Return true if the specified operation is illegal on this target or unlikely to be made legal with custom lowering. This is used to help guide high-level lowering decisions.

Definition at line 451 of file TargetLowering.h.

References Expand, getOperationAction(), and isTypeLegal().

Return true if the specified operation is legal on this target.

Definition at line 456 of file TargetLowering.h.

References getOperationAction(), isTypeLegal(), Legal, and llvm::MVT::Other.

Referenced by llvm::TargetLowering::BuildSDIV(), llvm::TargetLowering::BuildUDIV(), llvm::R600TargetLowering::PerformDAGCombine(), PerformSELECTCombine(), llvm::TargetLowering::SimplifySetCC(), and tryFoldToZero().

Return true if the specified operation is legal on this target or can be made legal with custom lowering. This is used to help guide high-level lowering decisions.

Definition at line 433 of file TargetLowering.h.

References Custom, getOperationAction(), isTypeLegal(), Legal, and llvm::MVT::Other.

Referenced by areJTsAllowed(), buildFromShuffleMostly(), llvm::TargetLowering::BuildSDIV(), llvm::TargetLowering::BuildUDIV(), FindOptimalMemOpLowering(), isNegatibleForFree(), PerformLOADCombine(), llvm::TargetLowering::SimplifyDemandedBits(), and XFormVExtractWithShuffleIntoLoad().

Return true if the specified operation is legal on this target or can be made legal using promotion. This is used to help guide high-level lowering decisions.

Definition at line 442 of file TargetLowering.h.

References getOperationAction(), isTypeLegal(), Legal, llvm::MVT::Other, and Promote.

Referenced by WidenMaskArithmetic().

|

inline |

Return true if pow2 div is cheaper than a chain of srl/add/sra.

Definition at line 195 of file TargetLowering.h.

|

inline |

Return true if selects are only cheaper than branches if the branch is unlikely to be predicted right.

Definition at line 203 of file TargetLowering.h.

References PredictableSelectIsExpensive.

Returns true if it's safe to use load / store of the specified type to expand memcpy / memset inline.

This is mostly true for all types except for some special cases. For example, on X86 targets without SSE2 f64 load / store are done with fldl / fstpl which also does type conversion. Note the specified type doesn't have to be legal as the hook is used before type legalization.

Reimplemented in llvm::X86TargetLowering.

Definition at line 748 of file TargetLowering.h.

Referenced by FindOptimalMemOpLowering().

|

inline |

Return true if the select operation is expensive for this target.

Definition at line 170 of file TargetLowering.h.

|

inlinevirtual |

Reimplemented in llvm::ARMTargetLowering.

Definition at line 172 of file TargetLowering.h.

|

inlinevirtual |

Targets can use this to indicate that they only support some VECTOR_SHUFFLE operations, those with specific masks. By default, if a target supports the VECTOR_SHUFFLE node, all mask values are assumed to be legal.

Reimplemented in llvm::X86TargetLowering, llvm::ARMTargetLowering, and llvm::MipsSETargetLowering.

Definition at line 399 of file TargetLowering.h.

|

inline |

Returns true if target has indicated at least one type should be bypassed.

Definition at line 186 of file TargetLowering.h.

References llvm::DenseMapBase< DerivedT, KeyT, ValueT, KeyInfoT >::empty().

Return true if it's free to truncate a value of type Ty1 to type Ty2. e.g. On x86 it's free to truncate a i32 value in register EAX to i16 by referencing its sub-register AX.

Reimplemented in llvm::X86TargetLowering, llvm::SystemZTargetLowering, llvm::MSP430TargetLowering, and llvm::HexagonTargetLowering.

Definition at line 1172 of file TargetLowering.h.

Referenced by ExtendUsesToFormExtLoad(), getMemsetStores(), and llvm::TargetLowering::TargetLoweringOpt::ShrinkDemandedOp().

Reimplemented in llvm::X86TargetLowering, llvm::SystemZTargetLowering, llvm::MSP430TargetLowering, and llvm::HexagonTargetLowering.

Definition at line 1185 of file TargetLowering.h.

Return true if the specified store with truncation is legal on this target.

Definition at line 488 of file TargetLowering.h.

References llvm::EVT::getSimpleVT(), getTruncStoreAction(), llvm::EVT::isSimple(), isTypeLegal(), and Legal.

Return true if the target has native support for the specified value type. This means that it has a register that directly holds it without promotions or expansions.

Definition at line 285 of file TargetLowering.h.

References llvm::array_lengthof(), llvm::EVT::getSimpleVT(), llvm::EVT::isSimple(), and llvm::MVT::SimpleTy.

Referenced by llvm::ARMTargetLowering::allowTruncateForTailCall(), llvm::X86TargetLowering::allowTruncateForTailCall(), llvm::TargetLowering::BuildSDIV(), llvm::TargetLowering::BuildUDIV(), canOpTrap(), computeRegisterProperties(), EltsFromConsecutiveLoads(), ExpandBITCAST(), ExpandUnalignedLoad(), ExpandUnalignedStore(), FindMemType(), FindOptimalMemOpLowering(), getCopyFromPartsVector(), getCopyToParts(), llvm::FastISel::getRegForValue(), getTypeToPromoteTo(), getVectorTypeBreakdown(), getVectorTypeBreakdownMVT(), isLegalRC(), isNoopBitcast(), isOperationExpand(), isOperationLegal(), isOperationLegalOrCustom(), isOperationLegalOrPromote(), isTruncStoreLegal(), llvm::X86TargetLowering::isTypeDesirableForOp(), llvm::TargetLowering::isTypeDesirableForOp(), llvm::NVPTXTargetLowering::isTypeSupportedInIntrinsic(), LowerADDC_ADDE_SUBC_SUBE(), LowerATOMIC_STORE(), LowerFP_TO_SINT(), LowerFP_TO_UINT(), LowerSINT_TO_FP(), LowerUINT_TO_FP(), LowerVectorIntExtend(), PerformANDCombine(), PerformExtendCombine(), PerformFMACombine(), PerformLOADCombine(), PerformORCombine(), PerformSELECTCombine(), PerformShiftCombine(), PerformShuffleCombine(), PerformSTORECombine(), PerformVECTOR_SHUFFLECombine(), PerformXORCombine(), llvm::ResourcePriorityQueue::rawRegPressureDelta(), llvm::X86TargetLowering::ReplaceNodeResults(), llvm::ResourcePriorityQueue::scheduledNode(), llvm::TargetLowering::SimplifySetCC(), llvm::SystemZTargetLowering::SystemZTargetLowering(), and llvm::SelectionDAGBuilder::visitBitTestHeader().

|

inlinevirtual |

Similar to isShuffleMaskLegal. This is used by Targets can use this to indicate if there is a suitable VECTOR_SHUFFLE that can be used to replace a VAND with a constant pool entry.

Reimplemented in llvm::X86TargetLowering.

Definition at line 413 of file TargetLowering.h.

Return true if any actual instruction that defines a value of type Ty1 implicitly zero-extends the value to Ty2 in the result register.

This does not necessarily include registers defined in unknown ways, such as incoming arguments, or copies from unknown virtual registers. Also, if isTruncateFree(Ty2, Ty1) is true, this does not necessarily apply to truncate instructions. e.g. on x86-64, all instructions that define 32-bit values implicit zero-extend the result out to 64 bits.

Reimplemented in llvm::X86TargetLowering, and llvm::MSP430TargetLowering.

Definition at line 1197 of file TargetLowering.h.

Referenced by isZExtFree(), and llvm::TargetLowering::TargetLoweringOpt::ShrinkDemandedOp().

Reimplemented in llvm::X86TargetLowering, and llvm::MSP430TargetLowering.

Definition at line 1201 of file TargetLowering.h.

Return true if zero-extending the specific node Val to type VT2 is free (either because it's implicitly zero-extended such as ARM ldrb / ldrh or because it's folded such as X86 zero-extending loads).

Reimplemented in llvm::X86TargetLowering, llvm::ARMTargetLowering, llvm::MSP430TargetLowering, and llvm::XCoreTargetLowering.

Definition at line 1239 of file TargetLowering.h.

References llvm::SDValue::getValueType(), and isZExtFree().

|

inlinevirtual |

Reset the operation actions based on target options.

Reimplemented in llvm::X86TargetLowering.

Definition at line 864 of file TargetLowering.h.

|

inlineprotected |

Specify how the target extends the result of a boolean value from i1 to a wider type. See getBooleanContents.

Definition at line 869 of file TargetLowering.h.

Referenced by llvm::MipsTargetLowering::MipsTargetLowering(), llvm::MSP430TargetLowering::MSP430TargetLowering(), llvm::NVPTXTargetLowering::NVPTXTargetLowering(), llvm::PPCTargetLowering::PPCTargetLowering(), llvm::R600TargetLowering::R600TargetLowering(), llvm::X86TargetLowering::resetOperationActions(), llvm::SystemZTargetLowering::SystemZTargetLowering(), and llvm::XCoreTargetLowering::XCoreTargetLowering().

|

inlineprotected |

Specify how the target extends the result of a vector boolean value from a vector of i1 to a wider type. See getBooleanContents.

Definition at line 873 of file TargetLowering.h.

Referenced by llvm::AArch64TargetLowering::AArch64TargetLowering(), llvm::ARMTargetLowering::ARMTargetLowering(), llvm::MipsTargetLowering::MipsTargetLowering(), llvm::MSP430TargetLowering::MSP430TargetLowering(), llvm::PPCTargetLowering::PPCTargetLowering(), llvm::R600TargetLowering::R600TargetLowering(), llvm::X86TargetLowering::resetOperationActions(), llvm::SystemZTargetLowering::SystemZTargetLowering(), and llvm::XCoreTargetLowering::XCoreTargetLowering().

|

inline |

Override the default CondCode to be used to test the result of the comparison libcall against zero.

Definition at line 1292 of file TargetLowering.h.

References llvm::Call.

Referenced by llvm::ARMTargetLowering::ARMTargetLowering().

|

inlineprotected |

Indicate that the specified condition code is or isn't supported on the target and indicate what to do about it.

The lower 5 bits of the SimpleTy index into Nth 2bit set from the 32-bit value and the upper 27 bits index into the second dimension of the array to select what 32-bit value to use.

Definition at line 1034 of file TargetLowering.h.

References llvm::array_lengthof(), llvm::MVT::LAST_VALUETYPE, and llvm::MVT::SimpleTy.

Referenced by llvm::MipsSETargetLowering::addMSAFloatType(), llvm::MipsSETargetLowering::addMSAIntType(), llvm::HexagonTargetLowering::HexagonTargetLowering(), llvm::PPCTargetLowering::PPCTargetLowering(), llvm::R600TargetLowering::R600TargetLowering(), llvm::X86TargetLowering::resetOperationActions(), and llvm::SITargetLowering::SITargetLowering().

|

inlineprotected |

If set to a physical register, this sets the register that receives the exception address on entry to a landing pad.

Definition at line 913 of file TargetLowering.h.

Referenced by llvm::AArch64TargetLowering::AArch64TargetLowering(), llvm::ARMTargetLowering::ARMTargetLowering(), llvm::HexagonTargetLowering::HexagonTargetLowering(), llvm::MipsTargetLowering::MipsTargetLowering(), llvm::PPCTargetLowering::PPCTargetLowering(), llvm::X86TargetLowering::resetOperationActions(), llvm::SparcTargetLowering::SparcTargetLowering(), llvm::SystemZTargetLowering::SystemZTargetLowering(), and llvm::XCoreTargetLowering::XCoreTargetLowering().

|

inlineprotected |

If set to a physical register, this sets the register that receives the exception typeid on entry to a landing pad.

Definition at line 919 of file TargetLowering.h.

Referenced by llvm::AArch64TargetLowering::AArch64TargetLowering(), llvm::ARMTargetLowering::ARMTargetLowering(), llvm::HexagonTargetLowering::HexagonTargetLowering(), llvm::MipsTargetLowering::MipsTargetLowering(), llvm::PPCTargetLowering::PPCTargetLowering(), llvm::X86TargetLowering::resetOperationActions(), llvm::SparcTargetLowering::SparcTargetLowering(), llvm::SystemZTargetLowering::SystemZTargetLowering(), and llvm::XCoreTargetLowering::XCoreTargetLowering().

|

inlineprotected |

Indicate that the specified indexed load does or does not work with the specified type and indicate what to do abort it.

NOTE: All indexed mode loads are initialized to Expand in TargetLowering.cpp

Definition at line 1009 of file TargetLowering.h.